基于SET的最佳通用逻辑门ULG.2电路优化设计

王 芳,孔伟名,应时彦,乔天泽

(1.浙江艺术职业学院 影视技术系,浙江 杭州 310053;2.浙江工业大学 信息工程学院,浙江 杭州 310023)

随着半导体制造工艺的不断提升, FinFET技术使得MOSFET器件的工艺尺寸再次压缩到了7 nm阶段,但是MOS技术将在3 nm达到其工艺和物理极限[1]。研发非经典MOSFET的新型纳米电子器件如单电子晶体管(Single electron transistor, SET)、碳纳米管场效应管(Carbon nanotube field effect transistor, CNTFET)、量子细胞自动机(Quantum-dot cellular automata, QCA)等无疑是逼近极限的有效途径[2-4]。其中,SET工作时仅需一个或几个电子,功耗极低,且与CMOS工艺结合最紧密,是制造新一代超低功耗、超高密度集成电路的最具竞争力的新型纳米电子器件之一。因此,SET在数字逻辑电路方面的应用受到广泛关注[2,5-7]。

1 逻辑门

1.1 SET的基本逻辑门

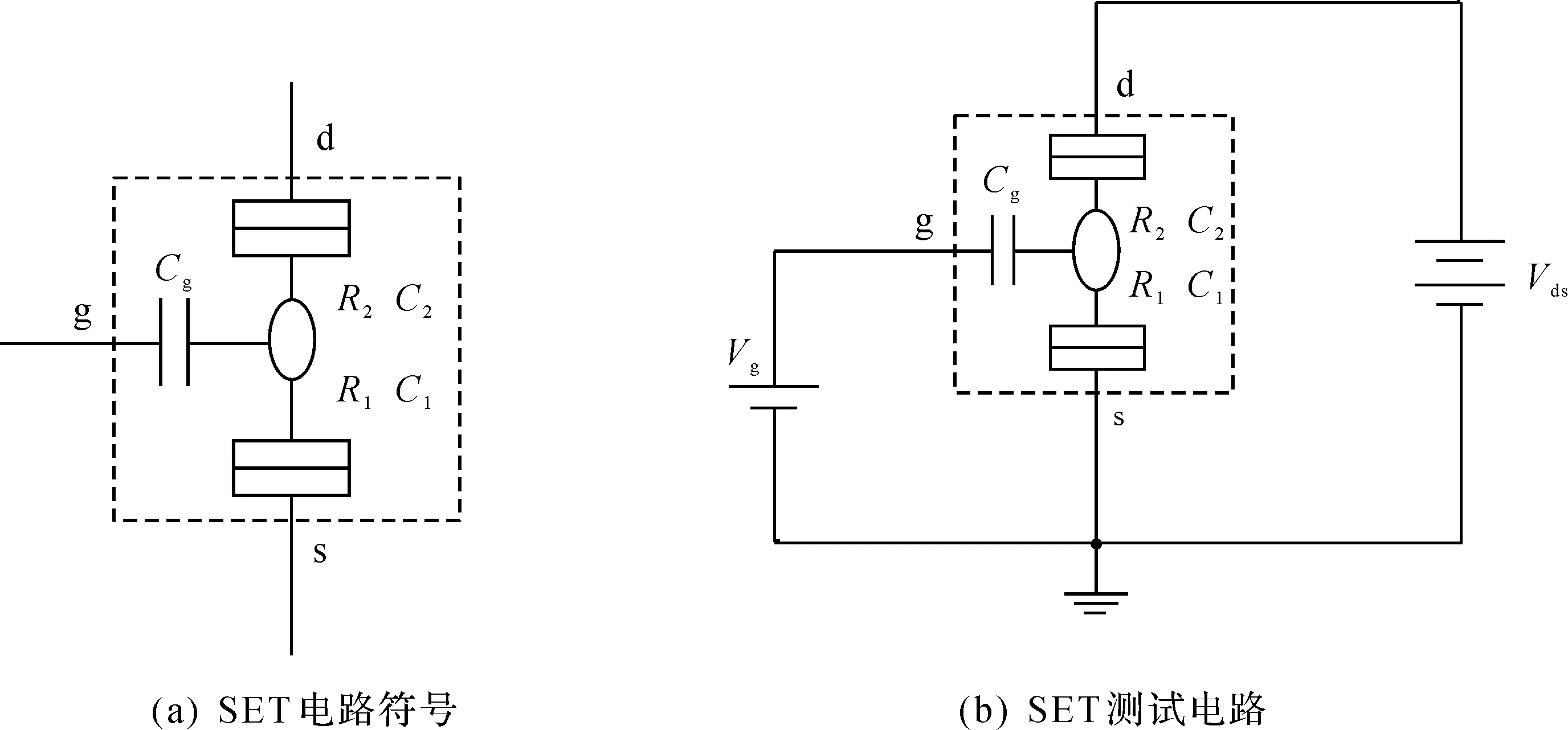

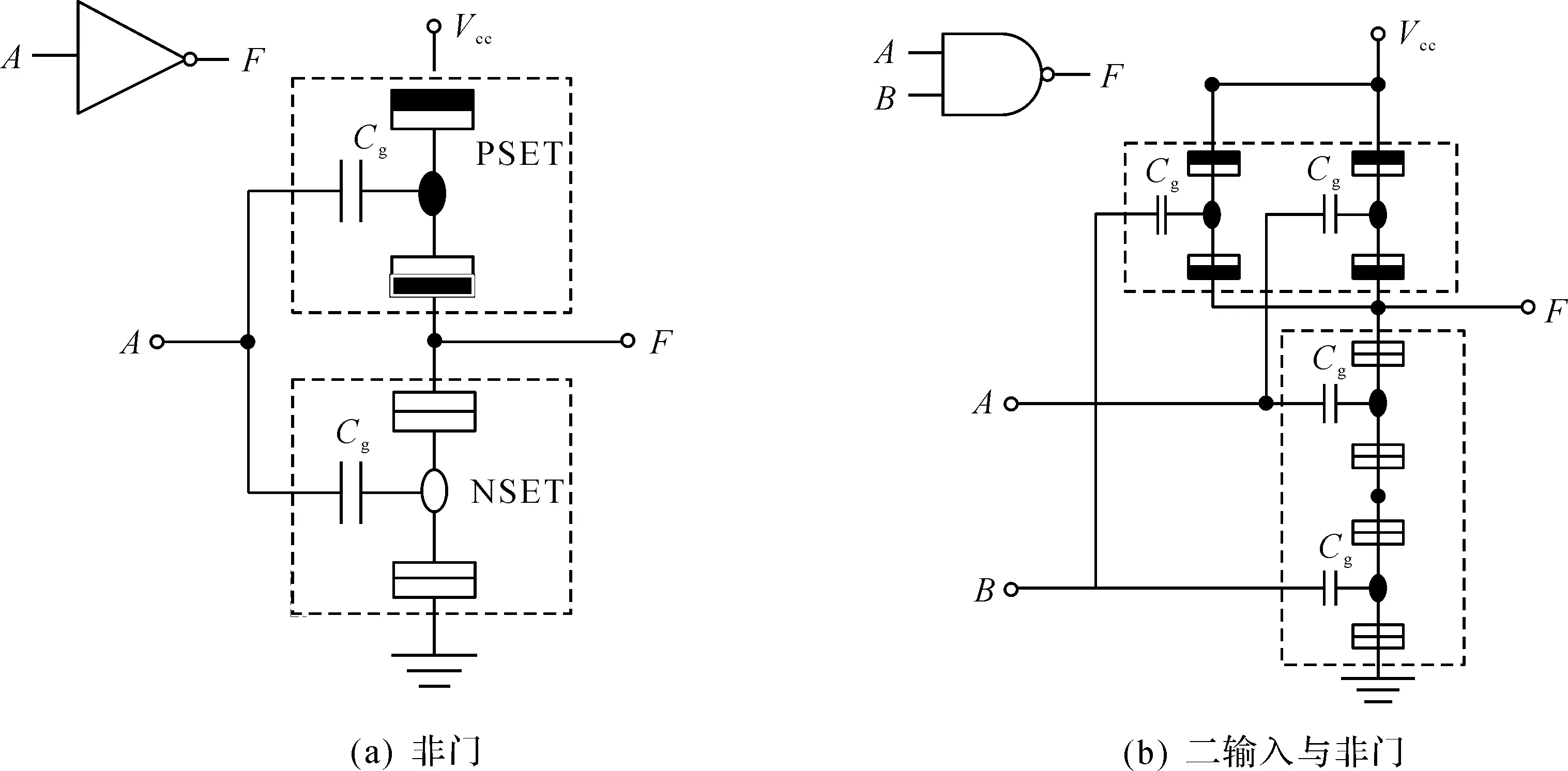

SET电路符号如图1(a)所示,g为栅极,s为源极,d为漏极,其管脚名称跟MOS管一样,工作原理却完全不同,SET是基于库仑阻塞和单电子隧穿等量子现象[8]。当漏源极和栅源极分别加合适的电压Vds和Vg,如图1(b)图所示,则形成漏源电流Ids,如果Vds固定不变,Ids将随Vg的变化形成周期性振荡。利用SET的这种通断特性可设计构造各种功能的SET逻辑电路,如全加器、触发器等[6-7]。SET还有一个重要特性即相移特性,当背景电荷值取得恰当,可使两个SET的库仑振荡曲线相位差180°,从而使它们工作在互补的通断状态,参照CMOS相应的SET分别称为NSET和PSET[8]。利用NSET和PSET,并参照CMOS逻辑电路的设计思想[9],SET设计出如图2所示的非门和二输入与非门。

图1 SET电路符号及测试电路Fig.1 SET circuit symbol and test circuit

图2 SET基本逻辑门Fig.2 Basic SET gates

1.2 最佳通用逻辑门ULG.2

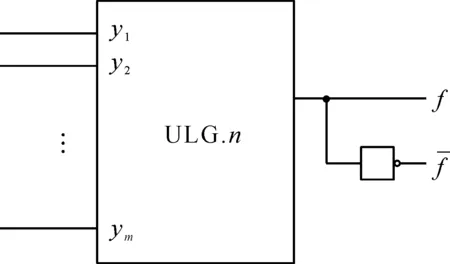

通用逻辑门(Universal logic gate)[10],是一种使用m个尽量不对称的输入端来实现n变量所有函数功能的电路,其是通过不同输入端所对应的不同连接方法来实现不同函数功能,对于实现了n变量函数的通用逻辑门可将其简称为ULG.n,如图3所示。

图3 通用逻辑门ULG.n图形符号Fig.3 Universal logic gate ULG.n graphic symbols

文献[11]证明ULG.n具有完备性,即其可以实现变量数小于以及等于n的所有函数。而且对于变量数大于n的函数,也可以通过连接多个ULG.n来实现。针对ULG.n中的变量数n而言,当n≥4时,ULG.n的电路实现过于复杂,单元占据面积过大,会造成逻辑冗余,因此变量数n<4才是比较实用且合适当作超大型集成电路的单元电路。故ULG.2和ULG.3才是较为实用的通用逻辑门电路,其NPN型电路最少输入端数分别为3和5[12]。

ULG.2一共需要实现16 种变量函数,文献[13]通过谱方法找到了6 种较为可行的ULG.2。通过多方面考量后,最佳ULG.2的函数表达式为

(1)

使用式(1)所代表的最佳ULG.2和传统的与非-非逻辑门相比,具有强的逻辑功能。Hellerman就分别使用最佳ULG.2和传统非-与非逻辑门来实现三变量对应的256 个函数的复杂情况进行研究,其结果表明式(1)所代表的最佳ULG.2具有明显优势[11,14]。

2 ULG.2的SET电路及其应用

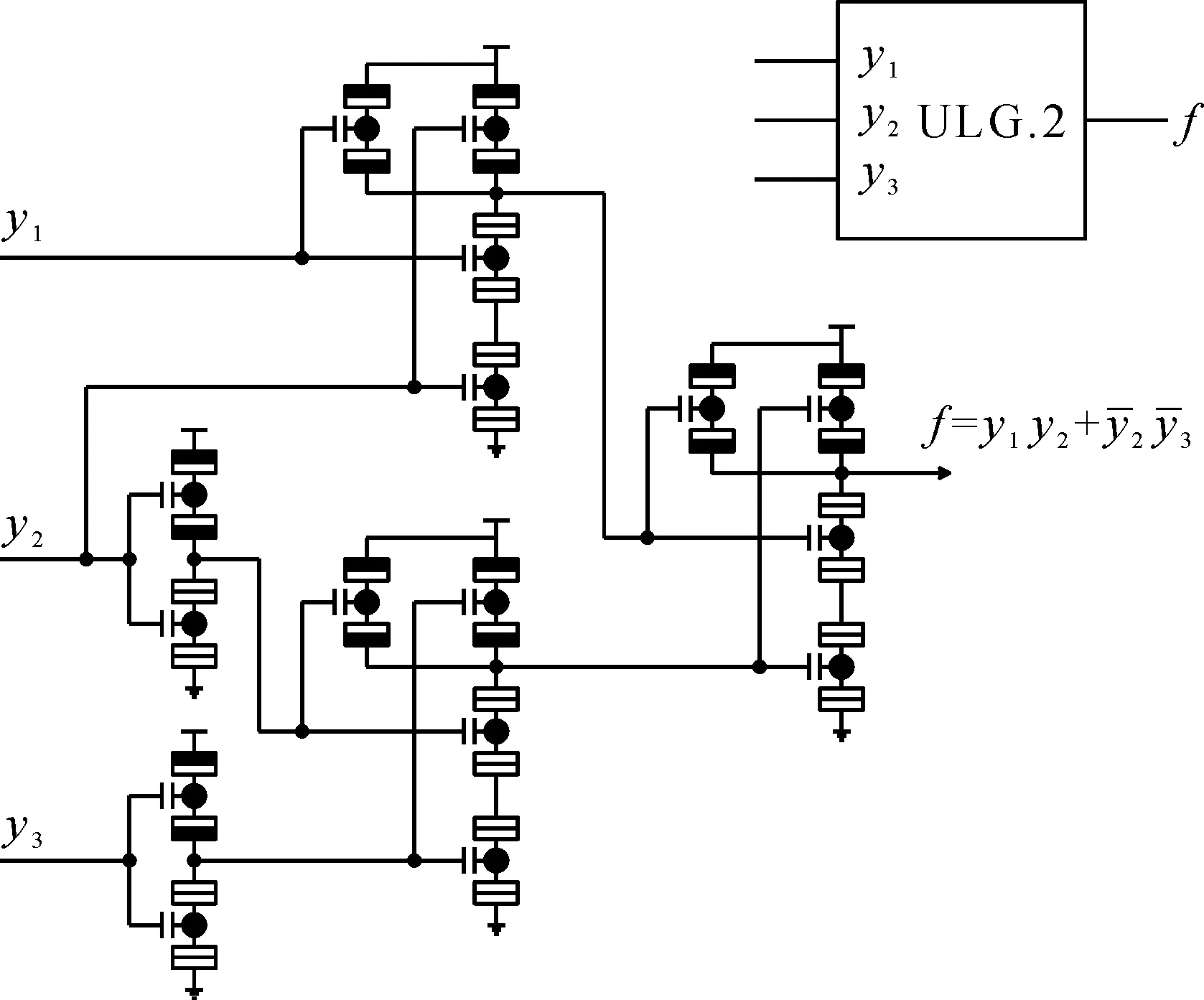

将式(1)使用与非-非的逻辑形式进行展开[15],得函数表达式为

(2)

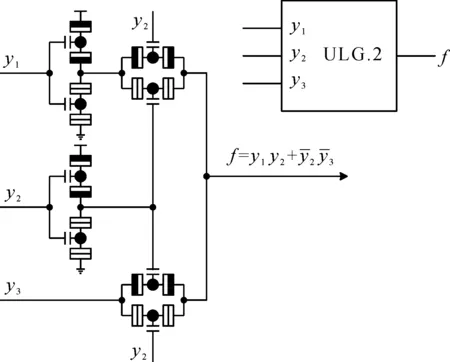

根据式(2)构造的SET电路由3 个与非门和2 个非门来实现,如图4所示。

图4 最佳通用逻辑门ULG.2逻辑符号及电路实现Fig.4 Optimal universal logic gate ULG.2 logic symbol and circuit implementation

图5 最佳通用逻辑门ULG.2电路优化设计Fig.5 Optimal universal logic gate ULG.2 circuit optimization design

基于最佳通用逻辑门ULG.2的全比较器设计过程如下:

1) 全比较器的函数表达式为

(3)

2) 用式(1)来实现式(3),则变换后的表达式为

(4)

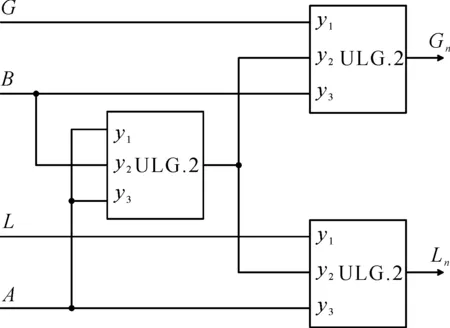

3) 由式(4)可知全比较器可由3 个最佳ULG.2组成,利用笔者优化设计所得的ULG.2实现的全比较器电路如图6所示。

图6 全比较器电路图Fig.6 Full comparer based on optimized ULG.2 circuit

3 电路仿真及分析

利用PSpice软件[16],使用LIENTSCHNIG SET-SPICE模型对第2节中的电路进行仿真,PSET与NSET参数设置参照第1节中的参数设置。电源电压为30 mV,输入信号高低电位电压分别为30,0 mV,输出信号的滤波电容为200 aF,仿真温度为4.2 K,仿真结果如图7所示。

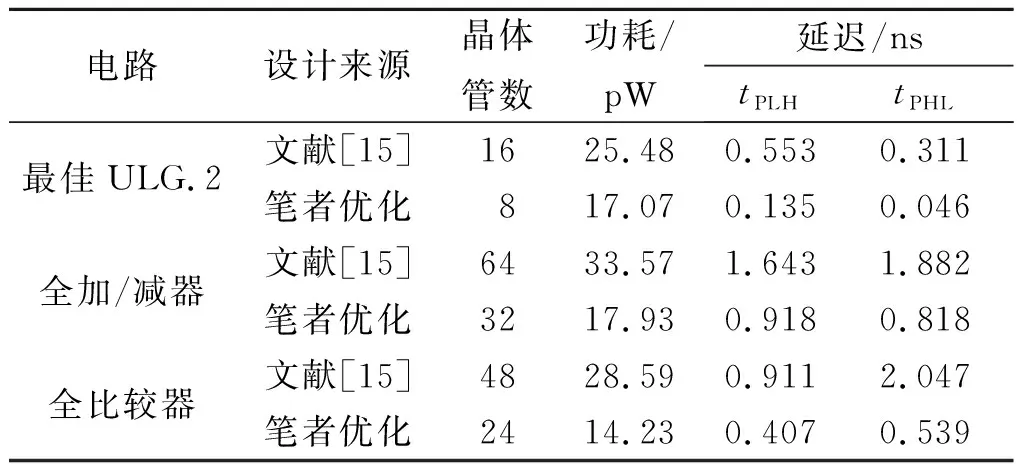

表1从晶体管数、电路功耗和电路延迟三方面比较了文献[15]与笔者所设计的最佳通用逻辑门的电路性能差别。由表1可知:所设计的SET电路与文献[15]的电路相比,全比较器在晶体管数方面减少了50%,在功耗方面降低了50.23%,在延迟方面减少了55.32%。

表1 最佳通用逻辑门电路性能比较Table 1 Optimal universal logic gate performance comparison

4 结 论

单电子晶体管具有体积小、功耗低等优点,是众多纳米器件中的强有力竞争者,而基于SET的最佳通用逻辑门ULG.2与通用逻辑门相比,具有较强的逻辑功能,笔者优化设计了ULG.2的SET电路及全比较器等电路,并用PSpice软件对所设计的电路进行仿真。结果表明:与现有ULG.2的SET电路相比,在晶体管数、电路功耗和电路延迟等都得到了进一步优化,为进一步研究ULG.2应用奠定了基础。