一种快速锁定低抖动的时钟数据恢复电路

武宇轩, 吕方旭, 吴苗苗

(空军工程大学防空反导学院,西安,710051)

近年来,高速串行接口发展迅速,根据ISSCC的统计,不同硬件中,虽然串行接口的速率不同,但均以指数形式增长[1-2]。

时钟数据恢复电路(Clock and Data Recovery circuit,CDR)广泛用于计算机[3]和光通信领域[4]。

不论是日常生活中常见的显卡接口,硬盘接口,还是用于高端研究的超级计算机,它们的快速发展都离不开高速串行接口技术的进步。而CDR正是高速串行接口接收机中最关键的电路模块。

CDR主要用于时钟与数据的同步,从携带噪声的数据中提取出时钟信息,对数据进行重定时,恢复出高质量的时钟和数据[5]。它的抖动容限、稳定性直接决定了接收机的性能[6];而CDR恢复出的时钟质量则决定了数据重定时的效果是否最佳,直接影响到所接收数据的可靠性。

恢复时钟的抖动大小以及环路的锁定时间是决定一款CDR性能优劣的重要指标。在光通信领域,影响环路稳定性的一个重要因素就是CDR的锁定时间,缩短CDR的锁定时间能够提高环路稳定性[7]。

图1 CDR的工作原理示意图

若要缩短环路的锁定时间,就要求环路带宽必须足够大,但其抖动性能则会大幅下降;若要恢复出低抖动的时钟,则环路会耗费较长的时间才能锁定[8]。Tang[6]和Hwang[9]设计了数字频差检测器,使环路滤波器的电阻值可调节;Woo和Chen[10-11]使用了锁定检测器;Chen设计了一种能够检测数据和参考时钟沿时序关系的模块。他们都通过改变比例通路增益的方式来缩短环路锁定时间,但是其电路仅用于较低速率的数据传输,且电路结构较为复杂。本文提出了一种能够应用于高速率CDR的锁定检测判别技术,可根据参考时钟频率和压控振荡器中心频率的频差大小,输出相应的控制信号,实现比例通路增益的可调节,使该CDR同时具备快速锁定和低抖动的特点。

1 低抖动快速锁定的理论分析

CDR主要由鉴相器(Phase Detector,PD)、电荷泵(Charge Pump,CP)、环路滤波器(Low-Pass Filter,LPF)、压控振荡器(Voltage-Controlled Oscillator,VCO)组成,其结构如图2所示[12]。

图2 传统CDR结构

本文所设计的CDR如图3所示,使用比例通路和积分通路分离的结构。比例通路能够对VCO直接、快速地进行频率调节,积分通路能够扩大环路的锁定范围。2个通路能够相对独立地对VCO的输出频率实施不同程度的调节。

图3 比例-积分通路分离CDR

文献[13~14]对CDR的稳定性能进行了研究,并给出了其系统模型,见图4。

图4 CDR的系统模型

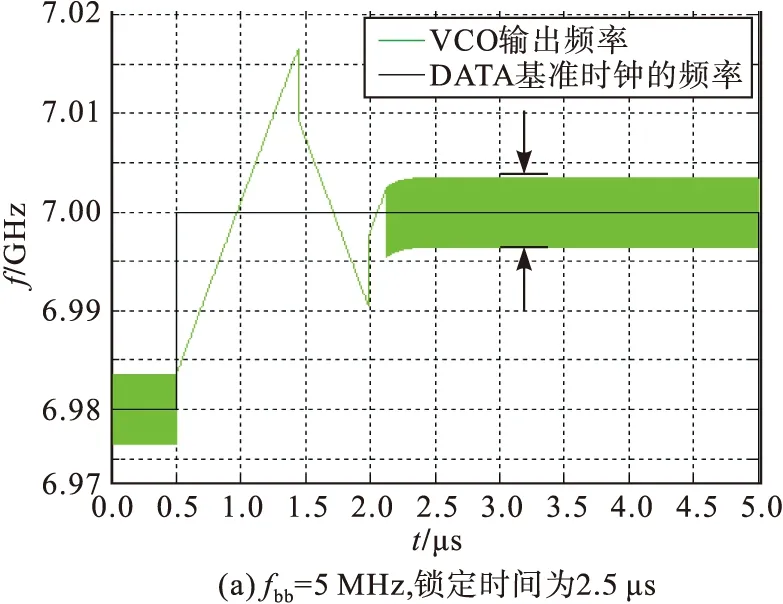

在二阶环路中必须确保比例通路占主导因素,在每一次更新的过程中,比例通路的更新相位要尽可能多的大于积分通路的相位变化量。适当增大比例通路的频率调节步长fbb,从而使稳定因子ζ增大、环路锁定时间缩短取ζ=1 000,δf=20 MHz,fnom=7 GHz,对具有不同fbb值的模型进行MATLAB仿真,结果如图5(a)、(b)、(c)所示。当fbb值分别取5 MHz、10 MHz、20 MHz时的锁定情况,其锁定时间分别为2.5 μs、1.3 μs和0.7 μs。从仿真结果可知,较大的fbb虽然能够缩短环路的锁定时间,但由于锁定后恢复时钟仍在以fbb的大小上下波动,故会引入较大的抖动;若减小fbb,虽可降低恢复时钟的抖动,但却会导致环路的锁定时间延长。基于这个问题,本文提出了一种锁定检测判别技术,利用锁定检测模块,使环路能够根据恢复时钟与VCO中心频率差的大小调整fbb的值,从而在缩短锁定时间的同时降低时钟抖动。

图5 不同fbb值的锁定情况

2 低抖动快速锁定CDR

2.1 整体结构

本文设计的低抖动快速锁定CDR整体架构如图6所示,采用1/4速率系统架构,利用八相正交的7 GHz时钟对数据进行采样。通过二进制鉴相器[15-16]对时钟和数据的相位关系进行判断,所得结果由EARLY 1~3和LATE 1~3输出,再由“择多逻辑门” 电路对判断结果进行选择,得到最终的相位关系EARLY和LATE。鉴相结果通过比例通路和积分通路,以不同的效果作用于VCO:比例通路通过控制信号V_bb0、V_bb1 和V_bb0*、V_bb1*,对2组不同大小的电容阵列分别进行控制,使VCO的频率能够不同程度地快速调节;积分通路则通过积分电容,使电荷泵输出的电流转化为电压信号Vc,实现对VCO精细调节。VCO输出的2路差分正弦信号,经过缓冲器和相位插值器的转换,恢复出CDR的八相时钟。

政府公信力提升是一个长期的过程,离不开稳定的制度保障。 首先,中国行政问责机制依然不完善,问责时机滞后,处于一种“亡羊补牢”的问责状态,呈现出被动问责的局面。 同时,在地方政府运行的过程中,民众参与渠道仍需进一步拓展。 时下,公众参政议政的广度和渠道依然需要改善,尤其是网络参政议政还需要进一步完善。

图6 本文CDR的整体电路结构

2.2 转换装置

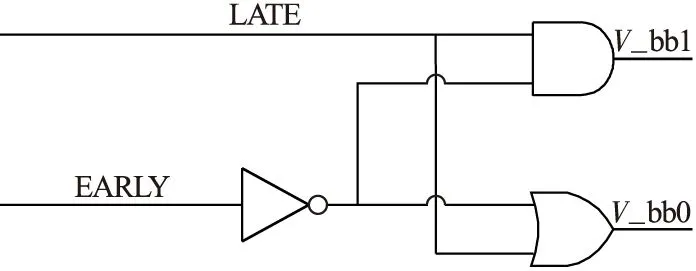

“择多逻辑门”电路产生的最终鉴相结果,分别经过积分通路和比例通路完成对VCO输出相位的调整。比例通路中,鉴相结果的超前、滞后、保持的控制逻辑和VCO的3个控制状态无法一一对应,因此需要增加图7转换电路实现二者之间的对应关系。

图7 比例通路设计

如表1所示,当EARLY/LATE判决结果均为1或均为0时,2个控制字中有一个为1,使VCO频率保持不变;当LATE=0,EARLY=1时,2个控制字均为0,VCO频率下降;当LATE =1,EARLY=0时,2个控制字均为1,VCO频率上升。最终实现对VCO状态的一一对应。

表1 鉴相结果与比例通路输出关系

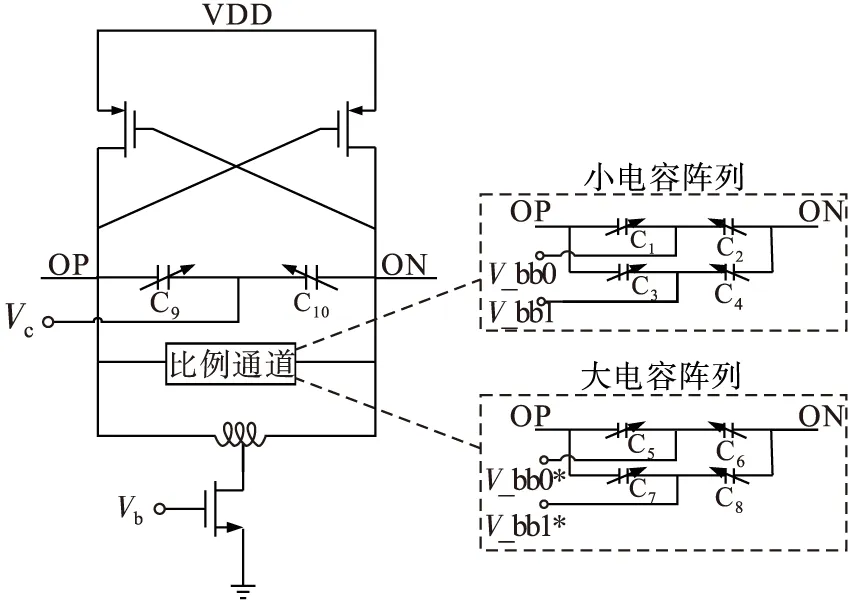

2.3 压控振荡器

本文设计的VCO为LC振荡器,适用于高精度、高频率环境。VCO电路结构如图8所示。

图8 压控振荡器电路设计

VCO的频率由10个压控电容的大小决定。电荷泵的输出电压Vc,控制电容C9,C10,比例通路的控制信号V_bb0和V_bb1控制小电容阵列C1~C4,V_bb0*和V_bb1*控制大电容阵列C5~C8。小电容阵列可实现较小的fbb;大电容阵列可实现较大的fbb。这些电容共同作用,以实现对VCO频率不同程度的调节。

2.4 锁定检测模块

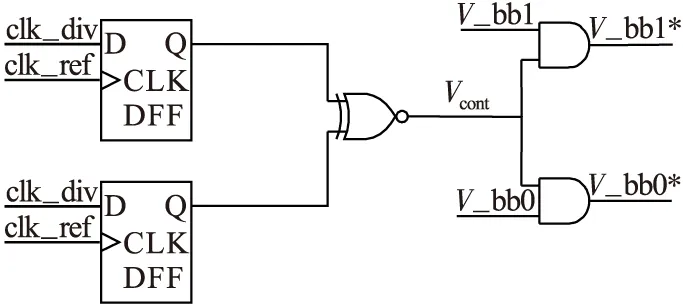

锁定检测模块的电路图结构如图9所示。二分频恢复时钟clk_div和参考时钟clk_ref分别与2个D触发器的clk和D端连接,经过“同或”逻辑门的输出Vcont能够反映2个时钟信号的频差或相差关系。当二者具有较大的频率差时,Vcont输出为高电平;当二者无频率差较小或仅存在相位差时,Vcont输出为低电平。V_bb0和V_bb1是图7中比例通路的2路控制信号,Vcont与V_bb0和V_bb1经过“与”逻辑门输出分别为V_bb0*和V_bb1*,用于控制VCO中大电容阵列C5~C8。

锁定检测模块的功能分析如下。当clk_div和clk_ref存在较大频差时,CDR处于未锁定状态,Vcont处于高电平状态,V_bb0*和V_bb1*的输出取决于V_bb0和V_bb1,VCO中大电容阵列C5~C8和小电容阵列C1~C4同时被接入,使fbb值变大,能够达到缩短锁定时间的作用;当clk_div和clk_ref频差较小或仅存在相位差时,CDR接近或已经进入锁定状态,Vcont处于低电平状态,V_bb0*和V_bb1*的输出为低,大电容阵列C5~C8未被接入,VCO中仅有小电容阵列C1~C4被接入,使fbb值变小,能够实现恢复时钟的的较低抖动。

图9 锁定检测模块

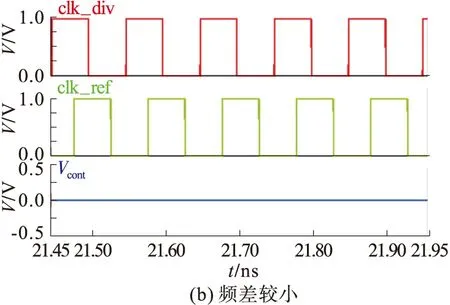

对锁定检测模块在2种不同情况下进行仿真。如图10(a)所示,当clk_div与clk_ref存在频率差时,Vcont输出结果为高电平,如图10(b)所示,clk_div与clk_ref无频率差,仅存在相位差,Vcont输出结果为低电平。

图10 锁定检测模块的仿真

3 仿真结果

本文采取TSMC65nm工艺,利用Cadence Virtuoso设计该时钟数据恢复电路的版图,面积为如图11所示。其中标号1处为CP,标号2处为二进制鉴相器,标号3处为锁定检测模块,标号4处为buffer,标号5处为相位插值器,标号6为VCO。

图11 芯片版图

本文仿真了在不同比例通路增益fbb的情况下环路的性能参数,如表2所示。其中,方案3使用了锁定检测判别技术,可以切换使用2组电容阵列,达到快速锁定。

表2 本文CDR的性能参数

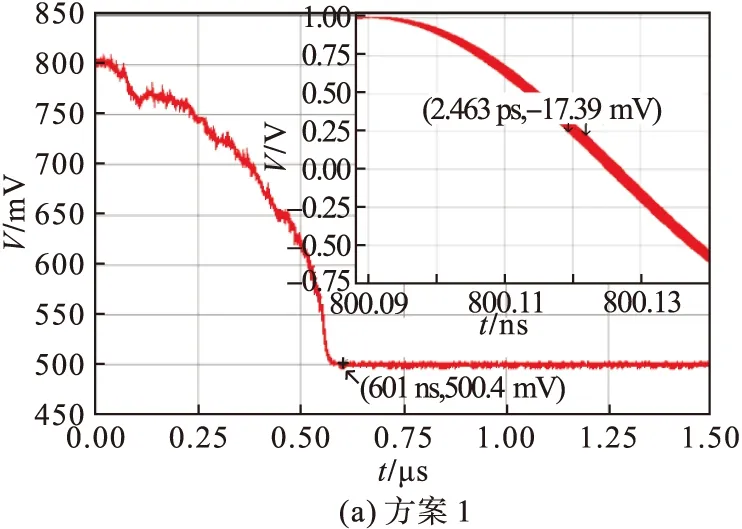

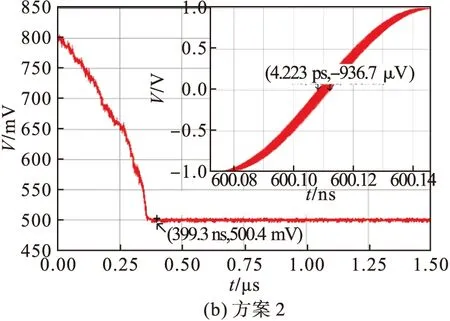

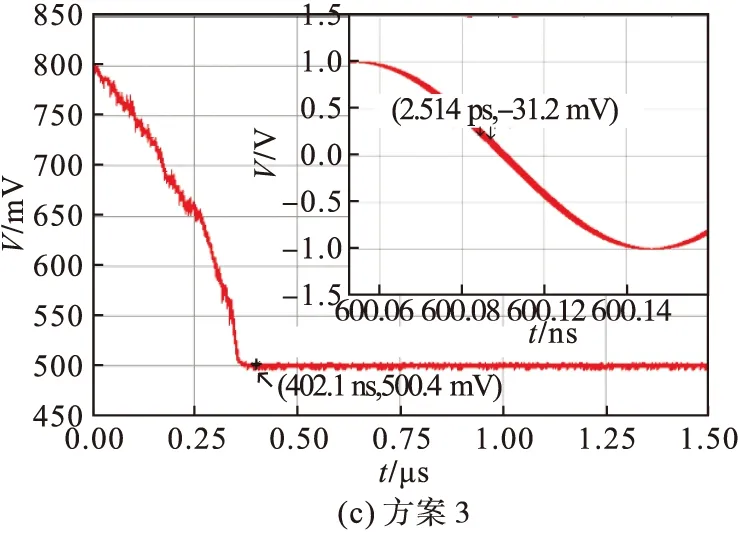

现在向本CDR发送28 Gb/s 非归零码数据。图12给出了3种方案从发送数据开始到环路进入锁定状态的过程中,VCO的控制电压和恢复时钟眼图抖动值的测量结果:方案1仅使用小的电容阵列C1~C4,对应的比例通路增益值fbb约为50 MHz。此方案锁定时间约为600 ns,恢复时钟抖动的峰峰值约为2.463 ps;方案2仅使用大的电容阵列C5~C8,对应的比例通路增益值fbb约为100 MHz。此方案锁定时间约为400 ns,恢复时钟抖动的峰峰值约为4.223 ps;方案3在环路中引入了锁定检测模块,可根据VCO的输出频率与其中心频率偏差值输出高电平或低电平,以达到切换使用大、小2组电容阵列的目的。由仿真结果可知,未引入锁定检测模块前,环路的锁定时间和恢复时钟的抖动值需要相互折衷,二者无法同时达到最优;但在引入锁定检测模块后,环路锁定时间约为400 ns,恢复时钟抖动的峰值约为2.514 ps,能够在不牺牲恢复时钟抖动性能的前提下,使环路以较快的速度进入锁定状态,说明这种方法能够兼顾前2种方案各自的优势。

图13是锁定检测模块的控制信号Vcont随时间变化的图像。在环路锁定之前,其输出常处于高电平状态,以确保2组电容阵列同时工作。此时,比例通路增益值fbb达到150 MHz,能够有效缩短环路的锁定时间;当环路接近锁定及锁定之后,其输出为低电平,使大电容阵列断开,比例通路增益值fbb重新回到50 MHz。此时,环路能够产生低抖动的时钟信号。

图12 VCO的控制电压和时钟抖动的测量

图13 锁定检测模块的输出

4 结语

本文设计了一种应用于28 Gb/s 非归零码接收机的CDR,该CDR应用了锁定检测模块,可根据环路的锁定情况输出不同电平,以达到控制比例通路增益值fbb的目的,有效解决了环路锁定时间和恢复时钟抖动性能难以兼顾的问题,使环路同时具备低抖动、快速锁定的优秀性能。相比于低抖动的方案1,锁定时间得到了缩短;相比于快速锁定的方案2,在保证锁定时间基本一致的情况下,使恢复时钟的抖动值被大大降低。