功率MOSFET并联主动均流设计与仿真

刘 通,崔业兵

(上海航天控制技术研究所,上海 201109)

0 引言

MOSFET以其开关速度快、导通电阻低等优点在电动自行车、电动叉车和电动伺服驱动器中均得到了广泛的应用。在工业应用中,往往需要多个分立器件并联,或采用多器件并联结构的功率模块[1-2],才能实现传导大电流的能力。然而,由于MOSFET器件参数、回路寄生参数和驱动电路的不一致,MOSFET并联时,将产生各并联MOSFET电流不均衡的问题,包括稳定导通后的静态电流不均衡,以及开关过程中的动态电流不均衡[3-4]。不均衡现象会使并联器件产生不对称的开关速度、导通电压和电流以及器件损耗,会使最薄弱的并联器件因过载而损坏,并危及其他并联器件的安全[5-6]。

针对多个MOSFET器件并联的电流不均衡问题,已有文献对其产生机理及应对措施进行了研究。文献[7-9]分别从数学理论推导、多管并联实验以及器件散热条件等方面对并联MOSFET的静态和动态均流特性进行的研究表明:器件参数的差异性以及电路板的布局布线引入的寄生电感对并联MOSFET动态和静态均流具有很大影响,而导通电阻则影响并联器件的静态电流均衡等。文献[10-12]通过仿真对并联MOSFET均流特性进行了分析,提出并验证了各自的均流措施,主要包括筛选参数一致的器件、优化器件布局以及合理布线使寄生参数尽可能均衡等被动均流方法;文献[12]提出了一种栅极电阻补偿方法解决并联MOSFET动态不均衡问题。此外,在文献[13]中提出了一种基于差分电流传感器检测的主动均流方法,通过闭环控制并联器件的电流偏差,达到对各个并联器件的开关时间的控制,进而实现电流调控。然而,由于导致并联MOSFET不均流的因素很难避免,常见的均流方法都有各自的局限性,因此,仍需进一步研究主动均流方法。

本文通过建立功率MOSFET并联的电路及数学模型,在分析导致MOSFET并联支路不均流的影响因素的基础上,根据法拉第电磁感应定律,采用串入耦合电感的均流方法[14],通过仿真实验对该模型以及均流方法的有效性和可行性进行了验证,为基于功率MOSFET并联的低压大电流逆变器设计提供了有效的技术途径。

1 功率MOSFET并联不均流分析

功率MOSFET的并联应用中,并联器件之间的均流问题包括静态均流和动态均流。静态电流是指功率器件在稳定导通的工作状态下通过的电流;动态电流是指功率器件在开通和关断时的电流[11]。

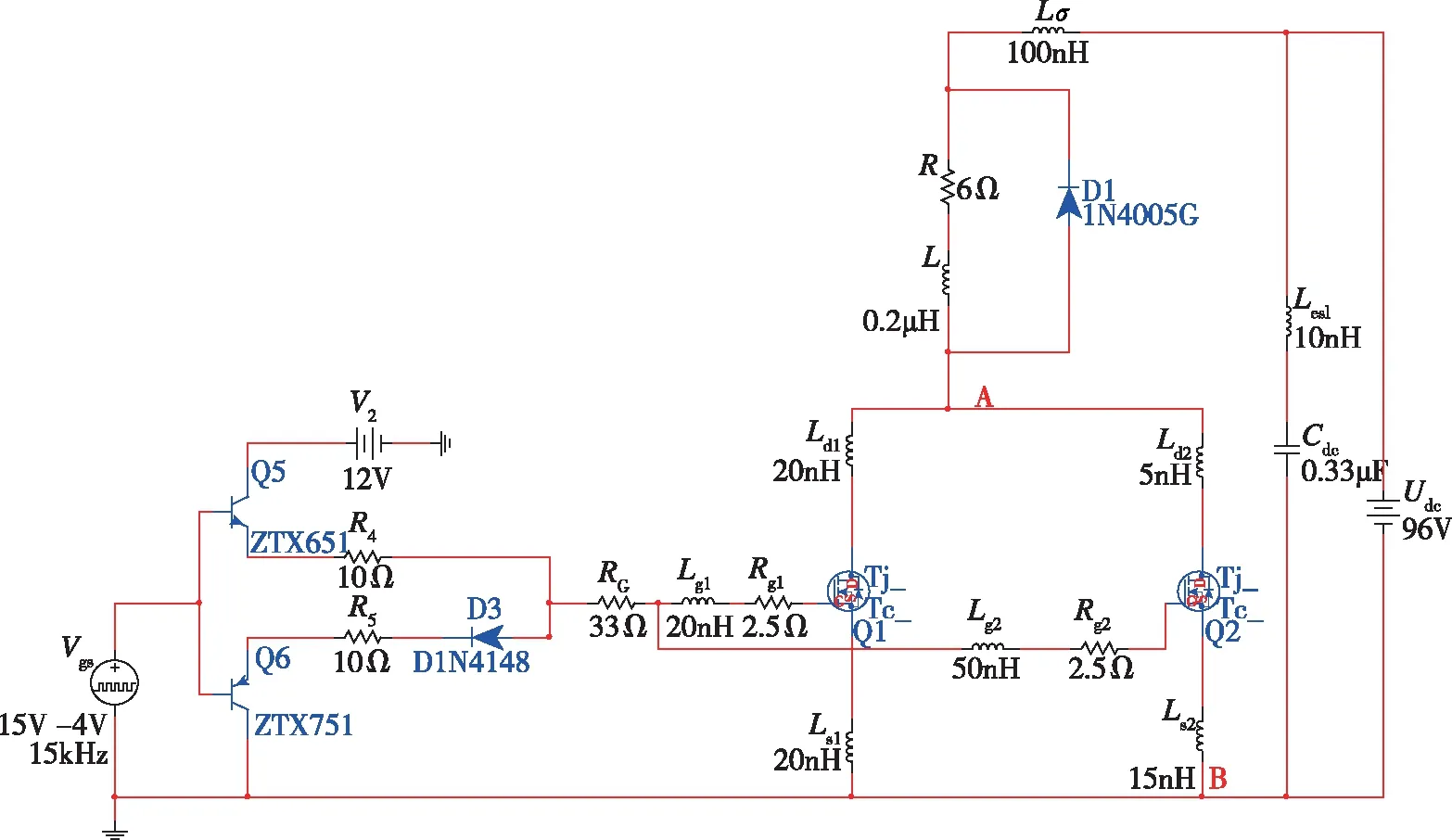

本文将使用仿真软件Multisim 对并联MOSFET回路进行仿真,仿真电路如图1所示,分析并联功率MOSFET各支路的静态和动态均流问题。在测试电路中,包括2个被测器件Q1和Q2,两者并联运行。功率MOSFET的电气特性参数主要包括:栅极内电阻Rg,不规则PCB布线在漏、源、栅极分别引入的寄生电感,Lg、Ld和Ls。Q1和Q2共用同一个驱动电路,总的栅极电阻为RG,驱动电压为VGS。Ld1(Ld2)为不规则PCB布线引起的漏极寄生电感,同理Ls1(Ls2)为源极寄生电感。Lg1(Lg2)为栅极寄生电感。Udc为母线电压,L为负载电感,Cdc为母线电容。Lσ、Lesl分别为母线电源以及母线电容的寄生电感。

并联MOSFET可等效为一个开关功率器件,开通状态时,直流电源和母线电容对其供电;关断状态时,负载电感L、负载电阻及反并联二极管组成续流回路。在功率管导通过程中,母线电源和母线电容的寄生电感Lσ、Lesl,以及负载电感L等构成功率振荡回路。但是,这属于并联器件的外部电路特征,对并联支路电流的影响不大。所以,在分析中将忽略母线电源和母线电容的寄生电感Lσ、Lesl的影响。

因此,图1中各支路寄生电感和电阻可分别简化表示为

(1)

在开通与关断过程中,MOSFET的漏源电阻Rds由栅源电压ugs控制,令uds为漏源电压,Vth为阈值电压,VGP为平台电压,Cgd(av)为栅漏电容平均值,Rdson为漏源极间导通电阻[15]。可得

(2)

在开关过程中,漏极电流id可表示为

(3)

其中,gm为跨导,且有

(4)

其中,ugs(t)为t时刻的栅源电压;μ为载流子有效迁移率;COX为栅氧化层的单位面积电容;W和LCH分别为沟道的宽度和长度;系数β和负荷电流IL可按式(5)、式(6)计算[1]。

(5)

(6)

其中,Δt为器件的开通时间。

图1 并联功率MOSFET的仿真电路Fig.1 Simulation circuit of parallel power MOSFET

1.1 器件参数不一致的影响

由式(3)可知,跨导、阈值电压和导通电阻等因素会对电流的静态特性产生影响,而驱动电阻RG和寄生电感则会对功率MOSFET的动态特性产生影响。当MOSFET并联时,这些影响因素都可能致使各并联支路中产生静态和动态电流不均衡现象。

在稳定导通状态下,并联器件的导通电流特性主要由导通电阻决定。并联支路导通电流可以分别表示为

(7)

式中,Rdson1和Rdson2为导通电阻,iL=id1+id2为2个并联支路的电流之和,则有

(8)

令偏差电流Δid=id1-id2,由式(7)有

(9)

由式(9)可知,偏差电流Δid受导通电阻Rdson的影响。当器件导通电阻越接近相等时,系数λ越接近于1,此时不均衡电流趋于0,从而均流效果最好。

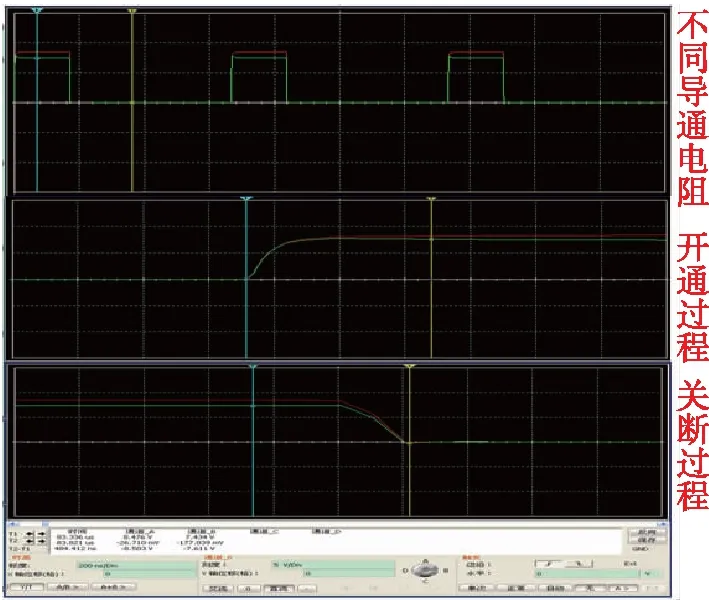

基于Multisim仿真软件,当Rdson有差异时,并联功率MOSFET的电流输出结果如图2所示,其中Q1和Q2的导通电阻分别为50mΩ和60mΩ,导通电阻的偏差导致了并联支路电流的不均衡现象。

图2 不同导通电阻的MOSFET并联效果Fig.2 Paralleled MOSFETs with different on-resistances

1.2 寄生参数不一致的影响

MOSFET并联均流的寄生参数主要包括:栅极引线电感Lg、源极引线电感Ls和漏极引线电感Ld等,在多管并联时一定要尽量使对应的各引线长度相同。

1.2.1 漏极电感

根据基尔霍夫定律,对于漏极电感,有

(10)

在导通电阻一致的情况下,即令Rds1=Rds2=Rds,则有

(11)

对于有差异的漏极电感,令Ld1=Ld2+ΔLd,则有

(12)

(13)

由式(12)、式(13)可得

(14)

(15)

当测试条件一定时,Uds、L、Rds为常数,偏差电流Δid与ΔLd成正比。在 Δt时刻,并联两支路误差电流Δid与Q1导通电流id1的比例可表示为

(16)

并联支路间电流的不均衡度与ΔLd、Rds和Δt均有关系,对于动态的情况,则有

(17)

式(17)表明,导通电阻Rds越大,负荷电流越大,在开关过程中不平衡电流的衰减速率越大,从而有利于达到动态均流。

1.2.2 源极电感

对于源极电感,假定器件的阀值电压和跨导参数相同,令gm为跨导;us为源极电感上的压降;Vth为阈值电压,同理有

(18)

由式(18)可得

(19)

因此,有

(20)

令Ls1=Ls2+ΔLs,则有

(21)

(22)

在Δt时刻,偏差电流与id1间的比例为

(23)

与式(16)相比,假设Ls2=Ld2、ΔLd=ΔLs,由于1/gm>Rdson,因此可知,源极电感较漏极电感对稳态电流差异的影响更小。

在开通和关断时,根据式(21)可知,偏差电流Δid与源极电感差异ΔLs、源极电感Ls、跨导gm和器件的初始电流id1(Δt)有关。由于1/gm>Rds,故动态电流的变化速率更大。

1.2.3 栅极电感

假设并联器件的其他参数一致,仅考虑栅极寄生电感的差异,可得

(24)

其中,ig1和ig2为并联支路栅极驱动电流,故电流的差异可表示为

(25)

(26)

其中,Rg为栅极回路的总电阻。

1.2.4 仿真分析

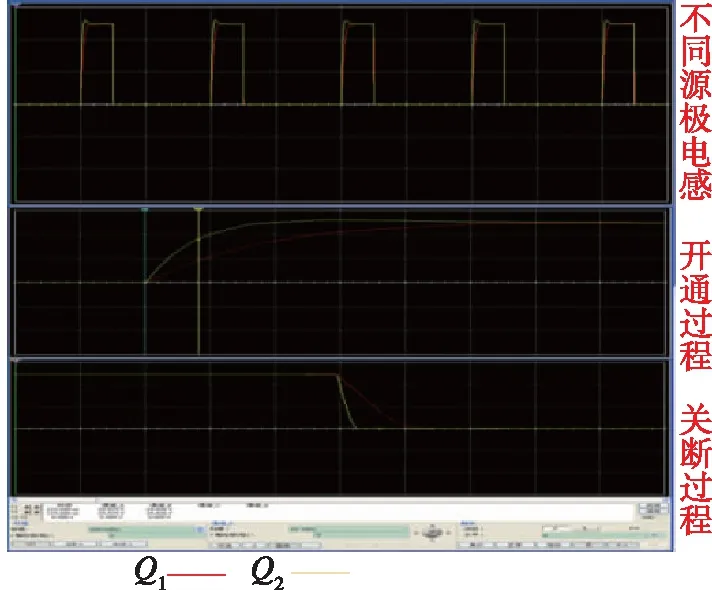

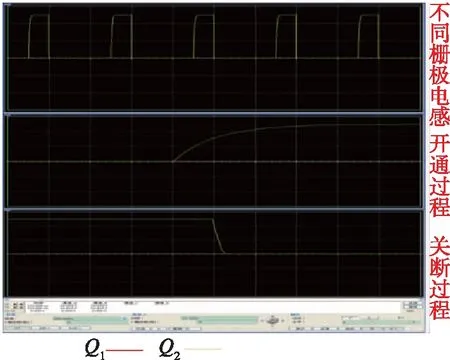

采用Multisim进行仿真分析,如图3所示。

(a)不同漏极电感Ld

(b)不同源极电感Ls

(c)不同栅极电感Lg图3 不同寄生参数对MOSFET并联的影响Fig.3 Influence of different parasitic parameters on MOSFET parallel connection

通过仿真图可以得出如下结论:

1)漏极电感对均流的影响

图3(a)中,Ld1=30nH,Ld2=5nH,设定源极电感、栅极电感和栅极电阻参数均相同。从图中可以看出,当漏极引入电感不同时,Q2先导通,在开通后分担大部分电流,在稳定后两管电流趋于一致。在关断过程中,关断时间受到漏极寄生电感的影响不大。

2)源极电感对均流的影响

图3(b)中,Ls1=30nH,Ls2=5nH,漏极和栅极电感相同,栅极电阻相同,可以看出,源极电感小的Q2先开通并且先关断。在导通时,Q2比Q1多承担了近1倍的电流,并随导通过程而逐渐减小至相同,当2个功率管完全导通后电流才分配均匀;关断过程中源极寄生电感对功率管关断时间有很大影响,图中Q2先关断,过程中Q1比Q2多承担1/4的电流。

3)栅极电感对均流的影响

图3(c)中,Lg1=20nH,Lg2=15nH,漏极和源极电感相同,栅极电阻相同,可以看出,当栅极电感Lg有差异时,导通和关断过程中栅极电感对均流影响很小。

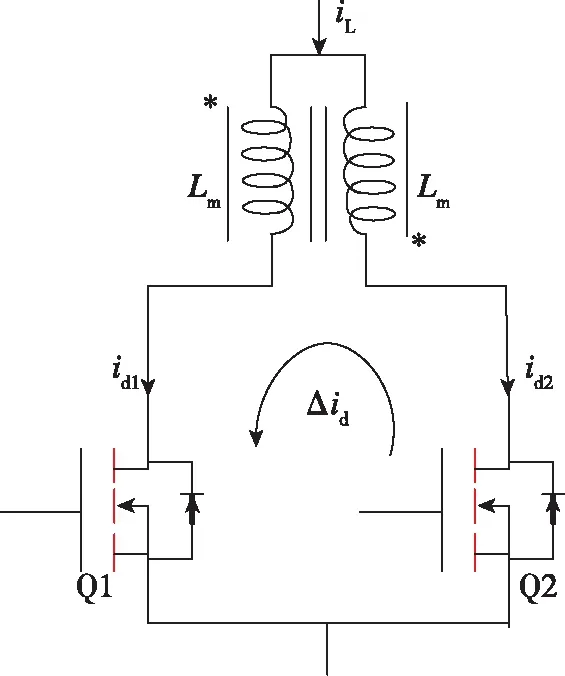

2 功率MOSFET并联主动均流原理

基于耦合电感的MOSFET并联均流控制方法,能够对包括动态不平衡电流以及静态不平衡电流在内的不平衡电流均起到抑制作用,从而实现并联MOSFET的各支路电流的均衡性,并且可以有效降低各MOSFET器件的开通和关断损耗差异,对各MOSFET器件进行有效保护,延长使用寿命,提升并联器件的电气性能和耐用性。

2.1 主动均流的原理

耦合电感实现并联均流的原理为:将耦合在公共磁芯上的匝数相同的2个线圈串入并联支路中,当有电流流过时,磁路中将产生方向相反的磁通。

当并联MOSFET参数一致、并联支路完全对称,且2个并联支路中的电流相等时,合成的磁通为0;当导通电阻和线路寄生参数等有差异时,并联支路产生的偏差电流将在磁芯中产生磁通,并感应出电动势,根据法拉第电磁感应定律,该感应电动势将维持并联支路电流偏差趋向于0,从而实现并联支路电流趋于均衡。

根据环路安培定理,有

ni=∮Hdl=H2πR

(27)

式中:n为线圈匝数;i为流过线圈的电流;H为磁场强度;R为线圈的等效半径。

假设2个线圈匝数相等为n,回路的激磁电感Lm所产生的感应电动势对支路的偏差电流Δid具有抑制作用,Lm和由Δid产生的感应电动势uf满足

(28)

其中

ΔΦ=ΔBS

(29)

ΔB=μrμ0(H1-H2)

(30)

式中:ΔΦ为磁通,ΔB为磁场强度,S为磁芯截面积;μ0为空气磁导率,μr为磁芯相对磁导率,H1和H2分别为并联支路中产生的磁场强度。

由式(27)~式(30)可得,感应电动势uf为

(31)

由式(31)可得,激磁电感为

(32)

由式(32)知,抑制并联支路偏差电流的电感为耦合线圈之间的激磁电感,对其可产生较强的抑制作用。

2.2 耦合电感的设计方法

如图4所示,由基尔霍夫定律,有

(33)

图4 耦合电感对并联均流的影响Fig.4 Effect of coupled inductors on parallel current sharing

其中,Lm≫max{Ld1+Ls1,Ld2+Ls2},故式(33)可简化为

(34)

另Rds1=Rds2+ΔRds,代入式(34)得

(35)

因此,偏差电流的动态响应时间可近似表示为

τs≈Lm/Rds

(36)

(37)

由式(37)可知,Δid的稳态抑制效果和耦合电感的大小无关,其动态抑制效果主要由响应时间τs决定。由于ΔRds≪Rds,采用耦合电感后,不平衡电流可以得到抑制。

3 实验验证

为量化并联器件电流的不平衡情况,定义不平衡度为

(38)

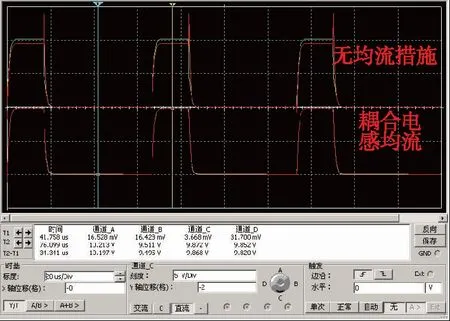

选用功率MOSFET器件IRF530N,构成2个功率器件并联不均衡回路,电磁线圈原副边各5匝,激磁电感Lm和漏感分别为30μH和100nH,测试器件Q1和Q2导通电阻分别为5mΩ和10mΩ。

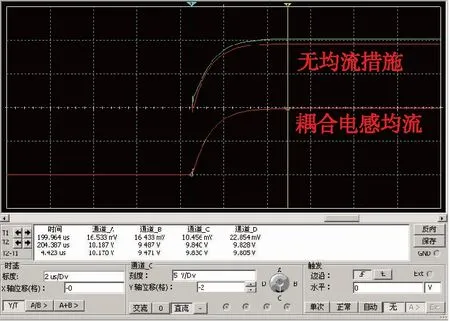

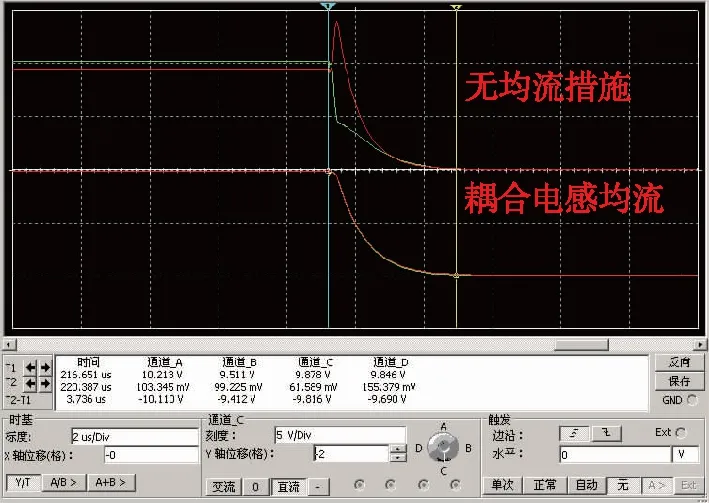

针对无均流措施和耦合电感均流两种情况,如图5所示,给出了并联器件开通、关断以及稳态情况下的运行情况。图5为采用耦合电感前后,均流效果对比图。

(a)无均流措施和耦合电感均流对比

(b)开通过程

(c)关断过程图5 基于耦合线圈的主动均流效果Fig.5 Effect of active current sharing with coupling inductor

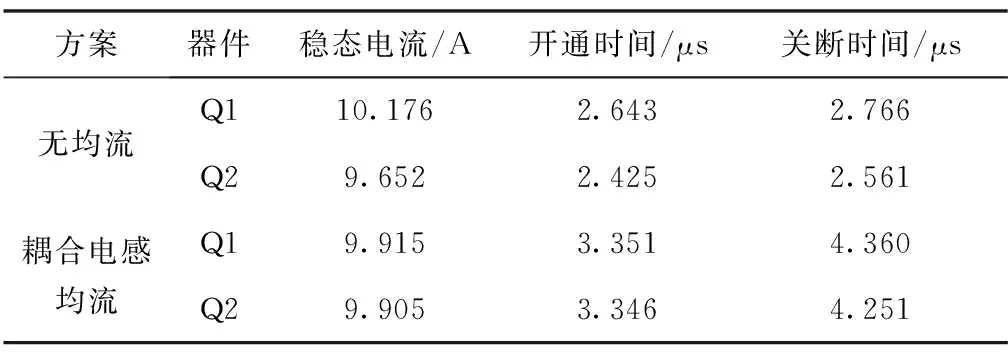

并联均流对比情况如表1所示。

表1 并联均流对比

对于稳态情况下,若不采用均流措施,并联器件的电流分别为10.176A和9.652A,其不平衡度α≈5.28%;采用耦合电感后电流分别控制为9.915A和9.905A,其不平衡度α<1%,更为均衡。另外,并联器件电流开通上升时间,分别从无均流措施的2.643μs和2.425μs,增加为加入耦合电感均流的3.351μs和3.346μs;同理,采用耦合电感均流后,器件的电流下降时间也从2.766μs和2.561μs增大为4.360μs和4.251μs。由此可见,采用串入耦合电感实现并联器件均流的同时,也会延长器件的电流上升和下降时间。

从图5中也可以看出,串入耦合电感后,并联MOSFET之间的静态电流更加均衡,从而使器件的损耗更加均匀;在开通和关断过程中,峰值电流亦得到有效抑制,达到很好的均衡效果,从而显著提高了并联支路电流均流效果。

4 结论

在MOSFET并联工作模式中,由于MOSFET参数的分散性和回路的不对称性等因素,将使并联MOSFET支路中产生电流不均现象。本文通过Multisim仿真,在分析功率MOSFET并联不均流因素的基础上,给出了基于耦合电感的并联主动均流方法;通过理论推导以及仿真试验验证了该方法可以很好地抑制静态和动态电流的不均衡现象,证明了其可行性和有效性,得出如下结论:

1)在并联MOSFET回路中,MOSFET导通电阻的差异,电路参数不匹配,如漏极、源极、栅极电感的差异性等都将导致并联MOSFET回路产生不均衡现象,而这些因素在并联MOSFET设计中均不可避免;

2)不平衡电流会使耦合电感产生较大的激磁电感,而平衡电流使其产生较小的漏感,因此,串入耦合电感可有效抑制并联支路间的不平衡电流,起到主动改善不均流现象的作用;

3)通过仿真试验,得出串入耦合电感不仅可以实现良好的动态均流,而且静态均流也得到显著改善,在均衡各并联器件损耗的同时,还有效降低了并联器件的开通和关断损耗;但是同时也会延缓器件电流的上升和下降速率。