变速率基带脉冲成形滤波技术*

盛德卫,高阳,文海

(北京电子工程总体研究所,北京 100854)

0 引言

随着航天技术快速发展的同时,数字信号处理技术中不断有新的通信协议和调制解调体制被研究和发展,但是不同的通信协议以及不同的通信体制之间互通性、兼容性都比较差,多体制通用信号源模拟技术是在这种背景下发展起来的。而成形滤波器广泛应用于各种信号源模拟体制中。作为全数字调制系统中关键模块之一:一方面它可以减小码间串扰,降低通信误码率;另一方面它可以限制频谱带宽,节省频率资源,它的高效运算及实现对降低整个系统运算量有着非常重要的意义[1-2]。

数字成形滤波器的实现方法通常有插值滤波法[3-4]和查表滤波法[5-9]。插值滤波器法内插倍数只是2的指数幂次,无法对连续变化的符号进行滤波,并且使用滤波器组算法复杂,对硬件实现提出很高的要求;查找表法保存的数据是成形滤波器的脉冲响应的采样值,通过查表后输出,然后再根据输入的数据序列进行简单的求补运算,如果输入数据序列的差值比变化范围比较大的时候,存储系数的存储单元将指数倍的增加,增加硬件实现资源的压力。同时一些先进的滤波算法受制于实现复杂度高和系统资源消耗大等因素,同样受到应用上的限制。

本文研究来源于某多体制通用信号源模拟器项目。在对数字基带信号进行成形滤波处理时,针对常规方法的局限性,给出了一种基于FPGA实现变速率基带脉冲成形滤波器的改进方法,实测验证了方法的可行性和有效性,研制的模拟器已成功应用在某空间型号中。

1 数字成形滤波器基本原理

根据无码间串扰理论,理想低通滤波器可以完美实现无码间串扰通信,且频带利用率达到最高,是基带系统所能达到的极限。但理想低通滤波器是物理不可实现的,因此升余弦滚降成形滤波器、平方根升余弦滚降成形滤波器以及高斯脉冲成形滤波器相继出现。在数字通信领域,为了减少接收端的误码率,普遍采用平方根升余弦滚降滤波器作为成形滤波器,平方根升余弦滚降滤波器在时域具有较快的衰减,降低抽样时判决错误的可能性[10-11]。

平方根升余弦滚降成形滤波器频率响应是升余弦滚降成形滤波器频率响应的开方,频域表达式[12-13]为

Hsrc(f)=

(1)

式中:Hsrc(f)为平方根升余弦滚降成形滤波器频率响应;Hrc(f)为升余弦滚降成形滤波器频率响应。

平方根升余弦滚降成形滤波器的冲击响应为

(2)

图1所示为α=0.5时,平方根滤波器的时域冲击响应与频率响应。

从平方根升余弦滚降特性的频率响应可以看出,它并不满足奈奎斯特第一定律;并且在Ts整数倍(除t=0)时刻并不为0,因此存在码间串扰。

在实际应用中,必须在接收端同时使用同参数平方根升余弦滚降成形滤波器作为匹配滤波器,一起构成一个升余弦滚降成形滤波器,从而消除码间串扰。同时,平方根升余弦滚降成形滤波器具有低通特性,可以降低带外噪声,提高输入信号信噪比。

2 改进的变速率基带脉冲成形滤波器实现方法

无线信号在高动态情况下传输的过程中,不仅载波有多普勒信息,在调制的数据符号上同样会存在多普勒频率,这样就会使得对数据符号进行成形滤波时不能采用常规的处理方法。针对常规方法的局限性,本文给出了一种基于FPGA实现变速率基带脉冲成形滤波器的改进方法,实现过程分为3个步骤,分别是:变速率降采样处理、成形滤波处理、插值上采样处理,实现原理如图2所示。

在多体制信号源设计中,每种模式下,数据相位的产生方式一致,进入到滤波器之前首先应该进行降采样处理,降采样处理主要包括2部分:首先是对数据符号进行抽取,每个数据位抽一个符号;然后对其他的抽取点进行插零处理。将降采样后的数据经过数字成形滤波器,滤波器后的数据速率还是低速率的。最后将数据速率提高到工作时钟频率,通过线性内插的方法进行上采样处理。

2.1 变速率降采样处理过程

输入的数据符号速率是加上动态后,每个符号位之间的长度不一致,由合并数据相位对数据符号进行抽样,降采样的处理过程如图3所示。

具体处理过程如下:

(1) 根据输入的数据小数相位高3 bits,产生抽样脉冲标志;

(2) 对待成形的数据进行抽样处理,每个数据符号采8个点;

(3) 进行数据变换,每个数据位的第一个采样点根据待成形数据判断,如果是‘1’,变换后数据为“01”,如果是‘0’,变换后为“11”;其余采样点数据都为“00”;

(4) 将变换后的数据进入到2 bits的移位寄存器中,完成数据采样。

降采样处理Modelsim仿真结果如图4所示。

2.2 成形滤波处理过程

本文滤波器的系数设计为49阶,如果直接进行卷积滤波处理的话,处理时延比较大,本文根据多相滤波的知识,对滤波器的实现过程采用多相结构[14-15],将49阶的滤波器分为6个8阶的子滤波器和一个滤波系数,通过多相结构的设计(表分割法和滤波系数对称性,增加流水线结构),可以使得滤波器处理的时延大大减少,提高运算速度。滤波处理的过程如图5所示。

具体处理过程如下:

(1) 根据滤波器系数改变标志,生成滤波器系数查找表地址,将系数输出至寄存器中;

(2) 根据滤波器处理过程中的多相滤波算法的原理,将滤波器系数进行分组;

(3) 将移位寄存器中的数据进行分组处理,用于滤波过程中的相乘累加过程,滤波器输入的数据是2 bits,只需通过选择即可完成相乘运算,大大降低了硬件压力;

(4) 将滤波子单元结果进行延迟相加处理,得到低速滤波结果。

滤波处理Modelsim仿真结果如图6所示。

2.3 变速率上采样处理过程

上采样的处理过程采用了线性内插的方法,2个低速滤波之间的内插点数不是固定的,通过计算2个点数之间的时钟个数可以得到内插点数,前后2个滤波结果做差值处理时可以先将其延时一个时钟,然后进行做差处理。然后通过差值和内插点数得到两者之间内插的步进频率字。上采样处理过程如图7所示。

具体处理过程如下:

(1) 将输入的低速滤波结果进行延时处理,与未延时结果进行做差处理;

(2) 统计2次滤波结果之间的工作时钟个数,作为内插的点数;

(3) 根据插值结果和内插点数,计算内插频率字;

(4) 通过线性内插的方法将滤波结果的速率提高,得到最终的滤波结果。

上采样处理Modelsim仿真的结果如图8所示。

3 实测结果验证及分析

3.1 实测结果

在OQPSK的调制过程中用到了平方根升余弦滚将滤波器作为调制系统中的成形滤波器。对输入的数据比特流“111011001011011101”进行成形处理,从图9中可以看出,滤波器最后输出是滤波器冲击响应平移叠加得到的,平移宽度为码元周期Ts。经过成形滤波器前后的数据序列的频谱如图10所示。

在实测中通过Chipscope工具抓取成形前后的数据序列如图11所示。

通过频谱仪观察成形后信号的频谱以及星座图等信息,如12所示。从图中可以看出,信号经过成形调制后,经过匹配滤波器后信号噪声被得到了较好的抑制,星座图中看出信号解调良好。

3.2 资源分析

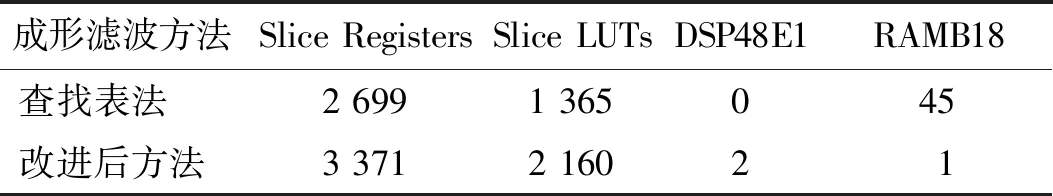

与常规查找表方法实现在占用资源上进行比较,如表1所示。

通过表1可以看出,改进后方法占用的Slice资源和乘法器资源会比常规的查表法高,但是占用RAMB18的资源大大减少,如果需要同时对多通道调制数据进行成形滤波处理的话,改进后的方法可以大大降低对硬件实现的压力。

表1 占用资源比较表Table 1 Comparison table of resource occupancy

4 结束语

针对常规的查表法和可变插值滤波器法存在硬件资源消耗大和无法适应数据速率连续变化的问题,本文给出一种改进方法,该方法易于FPGA实现,相对常规方法降低了实现复杂度,将改进后的滤波器用于OQPSK调制体制中验证方法的可行性和有效性。