衬底温度对共蒸发法制备Cu2ZnSnSe4太阳电池的影响

孙 顶, 李玉丽, 王凌群, 张玉红, 刘 航, 郭秀娟, 迟耀丹, 张 力

(1. 吉林建筑大学 电气与计算机学院, 吉林 长春 130118; 2. 南开大学 光电子薄膜器件与技术研究所, 天津 300071)

1 引 言

Cu(InGa)Se2(CIGS)太阳电池由于具有性能稳定、光电转换效率高等优点,目前已成为最有前景的薄膜太阳电池之一。但该器件需要使用的贵金属In的地球储量较少,而且其中大部分都用于平板显示工业中透明导电膜的制备,因此CIGS电池预计最大的年产量大约为100 GW[1]。

锌黄锡矿结构化合物Cu2ZnSnSe4(CZTSe)与黄铜矿结构的CIGS具有一定的相似性,且具有较高的光吸收系数(104cm-1), 目前转换效率已达到12.6%[2];并且由于贵金属元素In与Ga被廉价的Zn与Sn替换,因此CZTSe太阳电池具有制造成本低的优势,成为了近几年的研究热点。虽然最高效率的CIGS电池是采用共蒸发而非后硒化工艺制备的[3],但目前对共蒸发法制备CZTSe薄膜的研究还相对较少[4-6]。主要原因之一是CZTSe在高温下不稳定容易分解[7],而由于共蒸发法制备CZTSe过程中的Se压没有后硒化法的Se压高,加大了高温下使用共蒸发法制备稳定CZTSe薄膜的难度。本文针对这一问题,就衬底温度对共蒸发法制备CZTSe薄膜及器件性能的影响展开研究。

2 实 验

采用射频溅射工艺在钠钙玻璃上制备钼电极(约1 μm)。共蒸发工艺沉积CZTSe薄膜,通过调控Cu、Zn、Sn、Se 4个蒸发源的蒸发温度调整CZTSe薄膜的组分;沉积过程中衬底温度通过热偶与玻璃衬底的背面接触进行测试,并控制在380~460 ℃的范围内;薄膜生长的本底真空度低于6×10-5Pa。化学水浴法在CZTSe薄膜上制备CdS缓冲层(约50 nm)。MOCVD工艺沉积100 nm本征氧化锌和1 000 nm的硼掺杂氧化锌双层窗口层。蒸发工艺制备铝栅线电极,最终的电池结构为SLG/Mo/CZTSe/CdS/i-ZnO/ZnO∶B/Al[8]。

薄膜的晶相结构通过X射线衍射仪(XRD)(Rigaku, ATX-XRD)进行分析。薄膜的表面形貌通过扫描电子显微镜(SEM)(JSM 6700F)观察。能量色散X射线光谱仪(EDS)(JSM 6700F)分析薄膜的组分。量子效率分析系统(QEX10)测试器件的外量子效率。利用单晶Si标准电池校准的太阳光模拟器(WXS-156S-L2)在标准光强下(100 mW/cm2,25 ℃)测试电池的I-V曲线。

3 结果与讨论

3.1 衬底温度对CZTSe薄膜性质的影响

图1为不同衬底温度条件下制备薄膜的XRD衍射谱。从图中可以看出,低衬底温度下(380 ℃)制备的薄膜存在明显的SnSe和SnSe2相,这主要是由于衬底温度较低,SnSex挥发性降低而残留在薄膜中。随着衬底温度的升高,二元相SnSe和SnSe2在图谱中消失,高衬底温度下制备薄膜的衍射峰都与CZTSe对应[9]。

图1 不同衬底温度制备的CZTSe薄膜的XRD谱

Fig.1 XRD patterns of CZTSe films deposited at different substrate temperatures

图2为不同衬底温度条件下制备薄膜的表面形貌图。从图中可以看到,衬底温度为380 ℃条件下沉积的薄膜表面是一些细小的颗粒;当衬底温度升高到420 ℃时,薄膜的结晶质量明显变好;衬底温度达到460 ℃时,制备的薄膜的晶粒尺寸明显增大。随着沉底温度的升高,原子的迁移率增强,提高了薄膜的结晶质量。

图3分析了衬底温度对CZTSe薄膜组分的影响。研究发现,衬底温度的变化主要影响薄膜中Cu和Sn两种元素的含量。从图中可以看到,随着衬底温度的升高,薄膜中Cu元素的含量升高而Sn元素含量下降,Cu和Sn含量的比例几乎随温度升高而线性增加。这主要是由于随着衬底温度的升高,二元化合物SnSex的挥发性增强,使得Sn在高温下难以进入薄膜中[10];而CuxSey的蒸发温度非常高,所以衬底温度升高不会减少Cu的含量。图3中Cu含量的升高主要是由于Sn含量的相对百分比减少造成的。单质Zn挥发性较强,但沉积到衬底的Zn与Se反应生成的二元化合物ZnSe的挥发性则较小,所以衬底温度的升高可以使Zn进入薄膜的几率略有下降,但随着Sn含量的相对减少,Zn在薄膜中的相对百分比几乎不变;而Se作为非金属元素,比例基本在50%左右,故Zn和Se含量的百分比未在图中列出。

图2 不同衬底温度制备的CZTSe薄膜的表面形貌。(a) 380 ℃;(b) 420 ℃;(c) 480 ℃。

Fig.2 SEM images of CZTSe films deposited at different substrate temperatures. (a) 380 ℃. (b) 420 ℃. (c) 480 ℃.

图3 衬底温度对CZTSe薄膜组分的影响

Fig.3 Effect of substrate temperature on the compositions of CZTSe films

3.2 衬底温度对CZTSe电池性能的影响

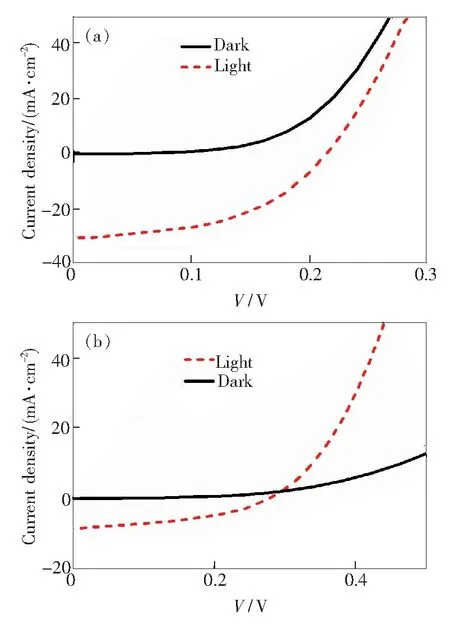

衬底温度为380 ℃条件下制备的CZTSe薄膜由于含有二元化合物SnSe和SnSe2而使电池失效。在衬底温度为460 ℃的条件下,通过降低Cu蒸发温度并延长沉积时间的方法,制备出与420 ℃相同组分及厚度的CZTSe薄膜(约1 μm)。最终得到的电池J-V曲线如图4所示。

图4 不同衬底温度制备的CZTSe电池的J-V曲线

Fig. 4J-Vcharacteristics of the CZTSe-based solar cells fabricated at different substrate temperatures

通过对比发现,衬底温度460 ℃条件下制备电池的开路电压有明显提高,但填充因子略有下降,而短路电流密度明显降低。开路电压增大主要是由于衬底温度升高提高了薄膜的结晶质量,随着晶界的减少载流子的复合几率降低。

量子效率测试表明,衬底温度460 ℃制备的电池在整个波长范围内响应都较低,如图5所示。造成这种现象的可能原因之一是器件中产生了影响空穴收集的势垒。

图5 不同衬底温度制备的CZTSe电池的量子效率曲线

Fig.5 EQE curves of the CZTSe solar cells fabricated at different substrate temperatures

对不同衬底温度制备的CZTSe电池进行光、暗J-V特性测试,如图6所示。高衬底温度制备电池的光暗J-V曲线发生了交叉,这也说明背电极存在势垒的可能性,并且是器件填充因子下降的原因之一。

图6 不同衬底温度制备的CZTSe电池的光暗J-V曲线(a)420 ℃;(b)460 ℃。

Fig.6 Dark and white lightJ-Vcurves for CZTSe solar cells fabricated at different substrate temperatures.(a) 420 ℃. (b) 460 ℃.

3.3 器件模型

图7为存在背电极势垒的CZTSe电池的能带示意图,假定Mo与CZTSe交界处坐标为x=0。由于势垒的存在将导致背电极处复合电流增大,并使光暗曲线产生交叉。

图7 存在背电极势垒的CZTSe电池能带示意图

Fig. 7 Band diagram of a CZTSe solar cell with back contact barrier

首先忽略背电极处空间电荷区内的载流子复合,则电子电流Jn(x)在吸收层恒定,并可用输运方程(1)进行描述:

(1)

其中Dn为电子扩散系数,Nc为导带有效态密度,Ec(x)为在x处的导带能量。经典的界面复合边界条件通常用公式(2)描述:

Jn(Lc)=Jn(0)=qSn(n(0)-n0),

(2)

Sn为表面电子的复合速率,n(0)为x=0处的电子浓度,n0为x=0处的平衡电子浓度。电子电流的计算借鉴肖特基势垒多子电流的计算方法[11],即对方程(1)在x=0和x=Lc的范围内积分,并利用边界条件(2)得到:

(3)

对于真实材料的参数,当qφbi的值足够大时,公式(3)中分母的第二项可以省略并只保留Sn项,最终简化为:

(4)

其中Vj的饱和值与光电流的存在与否有关,并可分别用公式(5)和(6)表示[12]:

(5)

(6)

由公式(5)、(6)可知在光照条件下Vj的值比暗态下高。并且在PN结较大正向偏压下,界面电子复合电流Jn(Lc)饱和且数值在光照条件下比暗态下高(在较大正向偏压下,公式(4)中的项在较大的正向偏压下可忽略),而空穴电流饱和值Jp(Lc)可用公式(7)表示[13],其饱和值为Jc与光照无关。

(7)

这意味着总电流在光照条件下达到饱和值比暗态下更高,而这可能会导致图6(b)中所示的光暗曲线交叉现象。在短路状态下,光电流正向流过背电极附近的势垒,势垒可等效成电阻。且理想状态下,器件在最高功率点和短路状态下的电流差别不会过大,因此势垒仍可等效成电阻,串联电阻对填充因子(K)的影响可以用经典公式描述:

(8)

串联电阻的存在可以导致填充因子减小,这也与图4的实验结果一致。ZnSe的禁带宽度比CZTSe宽,并且可以形成弱N型[14]。所以衬底温度460 ℃条件下制备电池所产生的问题可能与背电极附近产生的ZnSe有关,下面从蒸发法制备CZTSe薄膜生长机理讨论ZnSe产生的原因。

在衬底温度较低的条件下(420 ℃),Cu、Zn、Sn、Se四种元素可直接在衬底上反应生成CZTSe薄膜。而当衬底温度较高时(460 ℃),初始阶段SnSex很难在高温衬底上附着进而参与反应,生成的是稳定的二元化合物CuxSey和ZnSe。由于Cu原子的迁移能力强[15],随着蒸发的进行,薄膜底层的Cu扩散至表面与Sn和Se反应生成三元化合物Cu2SnSe3作为中间化合物[16],进而与表面蒸发的Zn和Se反应生成CZTSe。但Zn原子扩散能力较弱,导致初始阶段的ZnSe以二元化合物的状态留在背电极附近。

4 结 论

本文研究了衬底温度对共蒸发法制备CZTSe薄膜材料性质及电池性能的影响,得出如下结论:

(1)衬底温度380 ℃条件下,SnSex的挥发性不强;XRD测试发现制备的CZTSe薄膜中含有二元锡化物使电池失效。

(2)衬底温度升高到420 ℃时,二元锡化物的挥发性增强并从薄膜中消失。SEM测试发现薄膜的结晶质量随温度升高而提高,电池的开路电压由于晶界的减少而增大。

(3)当衬底温度升高到460 ℃时,电池的开路电压继续提高但短路电流密度及填充因子下降,这可能与高衬底温度制备CZTSe薄膜初始阶段产生的ZnSe有关。

(4)在高衬底温度下优化CZTSe薄膜沉积工艺将是进一步提高蒸发法制备CZTSe太阳电池转换效率的关键。