高速光接收机中低温漂基准电压源设计

童 伟,任 军

(成都嘉纳海威科技有限责任公司,成都 610000)

1 引言

光纤通信系统大大提升了通信容量和信息传输速度,推动了光通信芯片的广泛应用。高速光接收芯片的性能(灵敏度、动态范围、噪声等)对光信号传输质量至关重要。而以跨阻放大器为核心的模拟前端是光接收机芯片中最重要的模块,其噪声和动态范围直接决定了整个光接收机芯片的灵敏度和动态范围。因此,模拟前端的性能决定了光接收机乃至整个光纤通信系统的性能。而在光接收机芯片中,集成有高灵敏模拟前端、带宽/增益控制逻辑等诸多高速度、高带宽和高灵敏模块,为保证各个模块之间的独立工作,通常采用PMU单独为每个模块产生相应的供电,以保证光接收机芯片的整体性能。因此,PMU中需要设计低温度系数电压基准源为各电源调整模块提供稳定、不受工艺偏差影响的参考。

低温度系数电压基准源的设计由来已久。工业界和学术界进行了大量卓有成效的工作。传统意义上的电压基准源通过叠加负温系数VBE电压和正温系数ΔVBE实现[1-2]。为了进一步消除VBE中的非线性部分,一系列的高阶温度补偿技术得以发展,包括分段线性补偿技术[3-4]、亚阈工作MOSFET补偿技术[5-7]、指数补偿技术[8]等。从工程应用角度而言,常规一阶补偿结构已经可以满足以电源产品为代表的低精度应用,设计者更关心的是如何保证量产的一致性和规避工艺偏差的影响。

本文第2节主要介绍本文提出的低温度系数电压基准源的基本原理;第3节介绍电压基准源电路结构、OOS补偿电路结构;第4节介绍电路仿真结果和测试结果;第5节给出结论。

2 光接收芯片的PMU原理

高速光接收机芯片中,电源完整性问题不容忽视。片上PMU的设计直接关系到产品的噪声、稳定性、一致性[9]。通常片上电源需要满足低噪声、高响应速度、高电源抑制和高一致性。性能良好的片上电源通常需要具备以下几个特点:

(1)较低的噪声。提供低噪声的供电,可以有效降低跨阻放大器由电源引入的噪声,提升跨阻放大器的信噪比。

(2)较高的响应速度。光纤通信系统具有大动态范围、高传输速度,因此片上电源的控制带宽要与光接收机比特率相适应。一般需要规定满功率快速跳变时的电源变化范围,若带宽太小,动态响应过程中片上电源超出了允许的范围,往往会带来误码,影响信号质量,严重时可能使功能失效。

(3)较高的PSR。PSR表征了片上电源对供电的高频成分抑制作用。高速光接收机芯片中各个模块共用的电源往往存在不同模块不同工作状态情况下的跳变,因此共用电源往往存在大幅度的扰动。片上电源需提升PSR性能,为各模块去除电源中的高频成分,因此高灵敏度的接收机芯片必须具有高PSR的片上电源系统。

(4)较高的一致性。对于量产产品而言,批次一致性是至关重要的指标。而对电源而言,为保证精度(例如0.5%),需要对参考电压基准源进行修调。但修调的方式引入了额外的加工步骤,增加了测试成本或片上测试电路面积。由于片上PMU输出通道较多,希望电压基准源不修调的情况下保证足够的精度和低温度系数,从而降低测试的工作量。

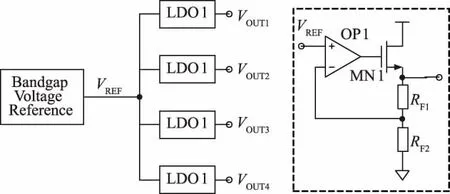

本文介绍的高速光接收芯片片上PMU功能框图如图1所示。

图1 高速光接收芯片片上PMU电路功能框图

在PMU的设计中,共用一个带隙基准电压源,而后送入到各个电压调整器中。片上电压调整器采用Capless-LDO形式设计,采用NMOS作为调整管,以得到较好的高频PSR能力。通过运放钳位VOUT分压后电压到基准电压VREF,从而为各个模块提供相应的供电。

3 低温度系数电压基准源电路设计

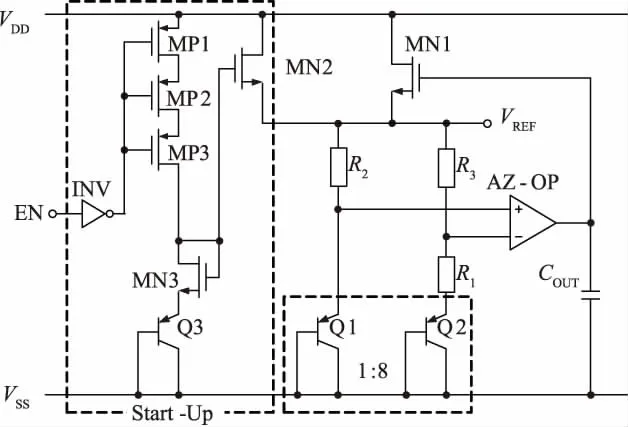

3.1 电压基准源核心电路设计

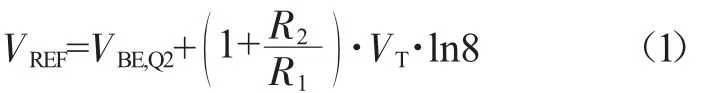

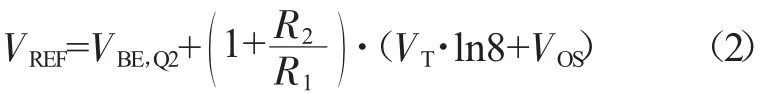

基准电路的作用是产生一个与温度和电压无关的基准电压VREF,基准电压大小为1.2 V,本文采用了如图2所示的一阶温度补偿带隙基准结构[1]。Q1、Q2为PNP晶体管,其中Q2发射极面积为Q1的8倍。运放AZ-OP钳位Q1发射极和R1,因此R1电流为PTAT电流。MN1受AZ-OP控制,其源极为基准电压VREF输出。左边虚线框内为启动电路,当EN为高时,PMOS管MP1、MP2、MP3开启,MN3和Q3导通。MN2连接了VREF和VDD,从而为VREF节点注入电流。当基准核心电路启动后,VREF电压上升,关闭MN2管,完成启动过程。基准电压的表达式为:

对于运放AZ-OP而言,由于MOS器件存在较大的阈值电压适配,且单位电流产生的跨导较小,因此相比双极工艺而言,MOS器件构成的运放失调电压较大。考虑失调电压的情况下,基准表达式变为:

因此基准电压受到了失调电压的影响,而且失调电压被增加了(1+R2/R1)倍。从式(2)可以看到,失调电压同时对基准的输出精度和温度系数产生了影响,在批量生产中将产生较大影响[10]。

图2 本文采用的电压基准源电路

3.2 OOS技术

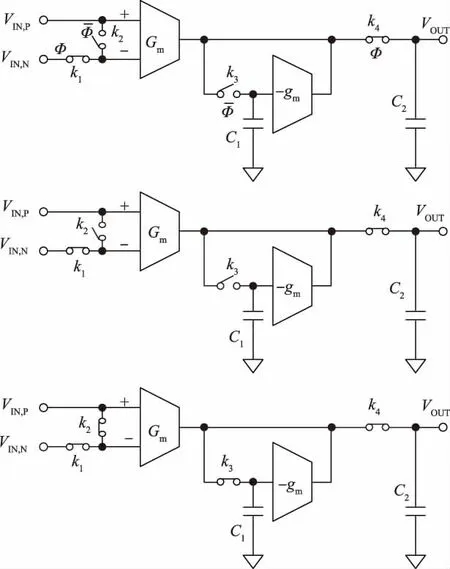

采用CMOS工艺的集成运放失调电压一般在1~20 mV之间。为了降低电压基准源中运算放大器失调电压对基准电压精度和温度系数的影响,需要对失调电压进行消除。常见的失调电压消除方法主要包含了自调零(Auto Zero)、斩波(Chopping)和相关双采样(Correlated Double Sample,CDS)3种方式。本文采用了 OOS(输出失调存储,Output Offset Storage)技术[2],通过采保电路存储输出失调电压,并对应产生失调电流补偿输出失调电流,得到了不同PVT情况下失调电压的消除效果,可以视为自调零技术的一类实现方法。

图3所示为OOS技术原理介绍[3-4]。其中端口VIN,P和VIN,N为运放的输入,VOUT为运放的输出。运放输入受开关k1、k2控制,主放大器为Gm,-gm为辅助放大器。k3和 C1、k4和 C2构成了两个采样-保持电路(Sample-Hold)。在时钟控制下,不同时刻有着不同的等效电路。在 Φ 有效时,k1、k4关闭,k2、k3开启。主放大器Gm表现为正常的放大器,而C1上存储的电压通过gm输出电流叠加在Gm的输出,此电流在主放大器Gm的输入等效为一个失调电压。在Φ无效时,k1、k4开启,k2、k3关闭。主放大器Gm的输入端连接在一起,等效为输入失调电压作为Gm的输入,从而产生了输出失调电压。-gm此时连接为单位增益反馈电路,主放大器的输出失调电压被-gm所捕获,并叠加响应的电流在主放大器的输出端,从而消除掉主放大器的输出失调电流。下一个相位,在 Φ 有效时,k1、k4关闭,k2、k3开启。C1存储的电压通过-gm产生失调电流,叠加到Gm的输出端,从而消除Gm的输入失调电压。在这个过程中,Gm的输出失调电压经过了采样、消除过程,因此称之为输出失调存储(Output Offset Storage,OOS)技术。相比传统的自调零技术,OOS技术实现较为简单,通过电流运算方式而不是电压方式进行失调电压的消除,具有更加紧凑的片上面积和较好的工艺适应性。

图3 OOS技术

3.3 采用OOS技术的运算放大器设计

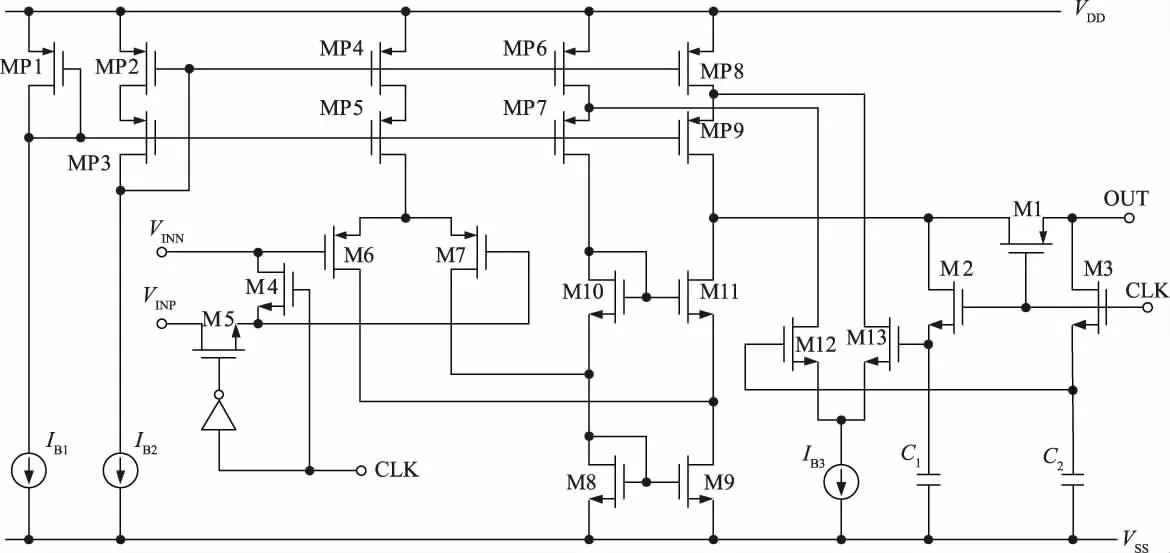

图4给出了采用OOS技术的运算放大器电路图。

(1)时间段A,时钟这时为一个固定电平,使BANDGAP工作在常规模式。M1导通,M2和M3关断。M4关断,M5导通,即运放的两个输入端VIP和VIN分别接到BANDGAP需要钳位的两端node1和node2。由于运放的功能是把两个输入端的电压钳成一样,所以这时VIP和VIN1端相等,而VIP和VIN之间差7 mV。

图4 AZ-OP的具体实现电路图

(2)时间段B,VCP这时为一个高电平,VCN为低电平,使BANDGAP工作在非常规模式。M1关断,M2和M3导通。M4导通,M5关断,即运放的两个输入端VIP和VIN都接到BANDGAP需要钳位的一端node2。由于这时强制性地保证VIP和VIN相等,所以这时VIP和VIN1之间差7 mV,而且由于是将VIP从连接到node1切换为连接到node2,所以VIP跳变为和VIN相等,即现在VIP比VIN1低7 mV。由于VIP和VOUT_OPA极性相同,所以VOUT_OPA变低。由于VFP在这半个时钟周期直接跟随VOUT_OPA,所以VFP也变低,并和VOUT_OPA相同;但由于这时VFN跟随前半个时钟周期的VOUT_OPA,所以VFN不变。

(3)时间段C,VCP这时为一个低电平,VCN为高电平,使BANDGAP工作在常规模式。M1导通,M2和M3关断。M4关断,M5导通,即运放的两个输入端VIP和VIN分别接到BANDGAP需要钳位的两端node1和node2。这时,由于M2和M3关断,所以VFP和VFN都保持时间段B的值,即VFP和VFN都不变。由于这是常规工作模式,VFP比VFN低,经过极性推导,会导致VOUT_OPA变高,经过基准整体电路,从而导致VIP和VIN变高,以及VIN1变高,VREF变高。这时,运放需要钳位的两端node1和node2,即VIP和VIN会钳到尽量一致。而VIP和VIN1有个压差,可以这么理解:失调电压等效成运放差分输入对管的W或L尺寸不一样,从而等效为VIP和VIN1有个压差(将失调电压设为零,运放差分输入对管的左边管的L由1 μm修改为1.1 μm,观察运放的两端输入信号,和VIP和VIN时序波形效果相同)。

(4)时间段D为重复时间段B的过程。

(5)时间段E为重复时间段C的过程。

(6)最终达到的效果是VREF随着时钟在一个非常小的范围内波动(小于1 mV),即达到的效果是运放两个输入端的失调电压经过一定的时序,转换为运放的两个反馈端VFP和VFN之间有一定的电压差,从而保证运放的输出不受运放失调电压的影响。

(7)如果从某个时刻开始,时钟信号始终为低,即BANDGAP会一直工作在常规模式,M1导通,M2和M3关断。M4关断,M5导通。由于M2和M3等的漏电流的存在,VFP和VFN会逐渐趋于一致,失调电压会重新逐渐影响VREF。经过一段时间后,VREF即回到最初没有时钟时候的值。

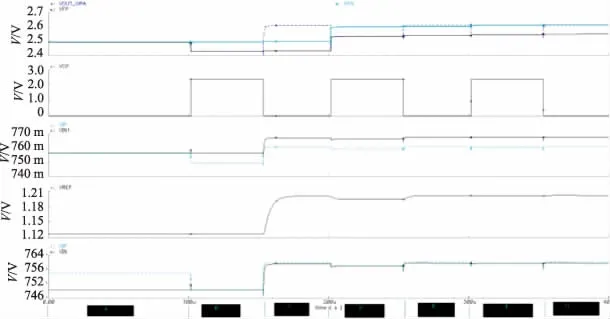

4 电路仿真和版图设计

本文所设计的低温漂基准源基于0.18 μm CMOS工艺进行设计。将时钟设置为延时100 μs,即开始时将时钟信号设置为使BANDGAP工作在常规模式。运放输入的VIN段到VIN1之间加入了7 mV的失调电压。为了方便分析,将时钟信号频率设置为10 kHz,仿真结果如图5所示。下面以时段来分析BANDGAP的工作过程。

图5 典型工艺角仿真(TT,25℃)

该基准电路模块中,通过BANDGAP_REGLATOR产生TIA芯片内部需要的多组电源电压,其优点是保证TIA芯片各模块工作电压之间互相干扰小,隔离度高。在BANDGAP核心电路中引入了时钟,通过时钟消除BANDGAP核心电路中运放的失调,从而保证芯片的一致性。基准电路模块中,时钟产生电路摆幅很大,所以噪声较大,所以在进行版图布局时,时钟产生电路的版图单独放在芯片右下角。同时,时钟产生电路产生的时钟信号需要送到基准电路模块中的时钟整形电路,再送到BANDGAP中的开关管。所以,在版图布局时所有的时钟线要尽量短,而且尽量少和基准电压线以及电源线交叉,否则输出基准电压上的毛刺会明显增大。

采用该结构的低温漂基准电压源测试结果如表1所示,可以看到温度系数完全满足指标要求。

表1 电压基准源量产测试结果

5 结论

本文介绍了一种应用于高速光接收芯片中的低温度系数电压基准源设计,所采用的OOS技术有效消除了工艺波动导致的失调电压对电压基准源的影响,在运放输入端的初始失调电压为7 mV时,输入失调电压可被降低到0.1 mV以下,温度系数最高为20.5×10-6/℃。量产测试结果显示该设计具有良好的性能。