低温漂高抑制比带隙基准电压源设计*

罗治民,刘伯权,郭佳佳

(湘潭大学微电子科学与工程系,湖南湘潭 411105)

1 引言

带隙基准电压源是许多模拟集成电路中的重要模块,作为基本参考源直接给电路提供高精度和高稳定性基准电压,被广泛应用于集成传感器、电压调整器、锁相环、低噪声放大器等电路中[1-2]。因此,带隙基准电压源对电路的性能具有决定性的影响。集成电路的发展以及应用环境需求的提高对带隙基准电压源的性能要求也愈来愈高,带隙基准电压源的性能取决于温漂系数、电源抑制比、输出电压精度及温度范围等[3]。而传统一阶带隙基准电压源的温漂系数在20×10-6/℃~100×10-6/℃,已经无法满足低温漂系数的要求[4],因此需要进一步降低传统带隙基准电压源的温漂系数。

降低传统带隙基准电压源的温漂系数除了对双极型晶体管基极-发射极电压VEB展开式一阶温度项进行曲率补偿外,在此基础上还需要对高阶温度项进行曲率补偿。目前高阶曲率补偿技术有采用不同的温度系数电阻补偿[5]、指数补偿[6]、采用两个带隙基准电路相减补偿[7]、分段补偿[8-9]等。采用不同的温度系数电阻补偿的电阻随温度变化非线性,受工艺影响较大;指数补偿利用晶体管增益的指数相关性进行补偿,晶体管占用版图面积较大,并且使带隙基准电压源的其他性能指标下降;采用两个带隙基准电路相减补偿电路结构比较复杂并且不易调控,故分段补偿是目前最常用的补偿方式。文献[10]、[11]中提到的分段补偿电路通过比较正、负温度系数电流大小,控制开关管的开启状态以进一步控制补偿电流,能使温漂系数达到4×10-6/℃左右,效果并不理想,因为正、负温度系数电流的大小随温度有微小波动,电路不易调控,并且额外增加正、负温度系数电流产生电路使得电路结构变得更复杂。在文献[12]中提到的分段补偿电路,高温段补偿是将MOS管漏、源极旁接在输出电阻两端,栅极接在输出电压上,电路结构简单,能使温漂系数降低到0.728×10-6/℃,但是电路的电源抑制比下降到只有-40~-50 dB,从而导致电路对电源波动抑制能力下降,因为栅极直接接在输出电压上,当电源电压波动时,MOS管的栅源电压波动较大,导致输出电压波动较大,从而使电路的电源抑制比下降。

基于以上的分析,本文设计了一种电流抽取与注入结构的补偿电路,能有效地降低温漂系数。补偿电路在基准输出电压随温度升高而增大的阶段抽取一定大小的正温度系数电流,在基准输出电压随温度升高而减小的阶段注入一定大小的正温度系数电流,通过只抽取或注入单一的正温度系数电流,电路容易实现,选择合适阻值的电阻来控制开关管开关状态,调试电流镜中MOS管的宽长比来控制补偿电流的大小,从而使基准输出电压的温漂系数得到优化。

2 带隙基准原理

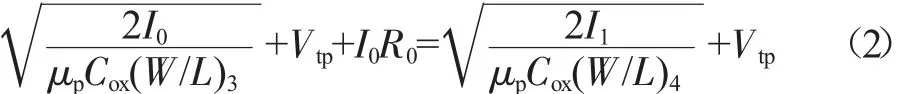

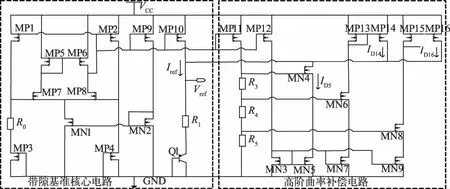

本文设计的带隙基准核心电路如图1所示[13]。基于放大器的钳位结构产生正温度系数电流I0、I1,通过设置电阻R0的阻值和MP3、MP4的宽长比来控制I0、I1电流的大小,并由电流镜镜像为Iref,注入到电阻R1上得到正温度系数电压VR1,并与负温度系数电压VEB1按一定权重相加,得到带隙基准核心电路的基准输出电压Vref:

式(1)中:VEB1是双极型晶体管Q1的基极-发射极的电压,Iref是正温度系数电流。根据MP1、MP2及MP5构成电流镜并由镜像关系,有Iref=I0=I1。

正温度系数电流产生电路工作原理为:运算放大器OP与MP1、MP2构成负反馈环路,使电阻R0上端A点和MOS管MP4源端B点电位近似相等,根据平方律公式[14],由此可得:

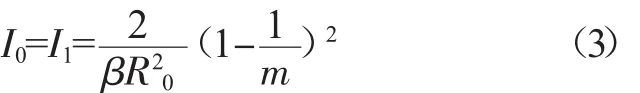

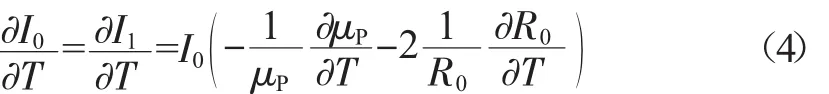

式(2)中:μp和Vtp分别为PMOS管的空穴迁移率和阈值电压,Cox是单位面积栅氧化层电容,PMOS管MP3的宽长比为(W/L)3设为m2,而MP4的宽长比为(W/L)4设为 1,令 β=μpCox(W/L)4。则有:

图1 带隙基准核心电路

根据式(3)可以推导出电流的温度系数:

式(4)中:迁移率的负温度系数的值为-4300×10-6/℃,电阻的正温度系数值为 1000×10-6/℃[15],带入到式(4),可知I0、I1随温度的升高而增大,即具有正温度系数。

温度系数为负的VEB1在温度为27℃时,温度系数在-1.5 mV/℃左右,再根据式(1),调节好正温度系数电流Iref的大小和电阻R1的阻值,即可得到温漂系数较小的基准输出电压。

3 带隙基准电路结构设计

本文设计的带隙基准输出电压的温度曲线呈现开口向下的抛物线变化趋势,即先随温度升高而增大,到达一定值后再随温度升高而减小。在基准电压增大阶段,表明正温度系数大于负温度系数。在基准输出电压减小阶段,表明正温度系数小于负温度系数。而基准输出电压的正温度系数就是电流Iref的正温度系数,负温度系数就是电压VEB的负温度系数。在电路中晶体管VEB的负温度系数的大小是不可通过电流来改变的,因此可通过调节电流Iref来降低基准输出电压源的温漂系数。在基准输出电压随温度升高而增大阶段,减小正温度系数电流Iref,以此减小基准电压的增大;在基准输出电压随温度升高而减小阶段,增大正温度系数电流Iref,以此减小基准输出电压的减小,从而达到降低带隙基准输出电压温漂系数的目的。

本文设计的高阶曲率补偿带隙基准电压源整体电路如图2所示,由带隙基准核心电路、高阶曲率补偿电路两部分组成。其中VCC是接供电电源,GND是接地端。带隙基准核心电路由晶体管MP5、MP6、MP7、MP8构成的差分放大器钳位使晶体管MP4的栅源电压与MP3的栅源电压差加载到电阻R0上,从而产生一个正温度系数电流,晶体管MN1、MN2、MP9构成恒流源为差分放大器提供偏置电流使其正常工作,晶体管MP1、MP2、MP10构成电流镜将正温度系数电流镜像到输出端,注入到电阻R1上形成正温度系数电压,再加上双极型晶体管的基极-发射极的负温度系数电压,构成带隙基准核心电路。

高阶曲率补偿电路通过NMOS管的导通在基准输出电压上升阶段抽取相应的正温度系数电流来降低电压的上升速率,在基准输出电压下降阶段注入相应的正温度系数电流来降低电压的下降速率,以此来降低带隙基准输出电压的温漂系数。晶体管MP10与MP12 构成电流镜,晶体管 MN3、MN5、MN7、MN9 的漏源极产生一个镜像于晶体管MP9的正温度系数电流。如果开关管MN4、MN6、MN8都导通,则晶体管MN5、MP14、M916 的漏源极会镜像晶体管 MN3、MN7、MN9的正温度系数电流。晶体管MP11也与MP10构成镜像电流源,在晶体管MP11的支路上产生一个正温度系数电流,于是在电阻R3、R4、R5上端产生正温度系数电压V3、V4、V5,它们随着温度的升高而增大,其大小控制着开关管MN4、MN6、MN8的开启关闭状态。随着温度升高到一定值,使得V3大于开关管MN4的开启电压,由晶体管MN4、MN5构成的支路导通,抽取相应的正温度系数电流使流过R1的电流减小,从而降低基准输出电压的上升速率,当温度继续上升时开关管MN4一直导通。当电压V4大于开关管MN6的开启电压时,由晶体管 MN6、MN7、MP13、MP14组成的支路导通,晶体管MP14的支路镜像晶体管MN7的正温度系数电流注入到电阻R1上,从而降低基准输出电压的下降速率。随着温度升高时抽取的电流越来越大于注入的电流,所以需要再注入电流,当电压V5大于开关管MN8的开启电压时,由晶体管MN8、MN9、MP15、MP16 组成的支路导通,晶体管MP16的支路镜像晶体管MN9的正温度系数电流注入到电阻R1上,从而降低基准输出电压的下降速率。

图2 分段线性补偿带隙基准电压源电路

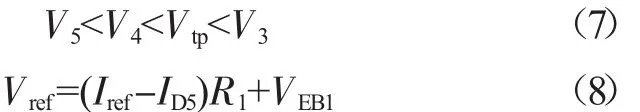

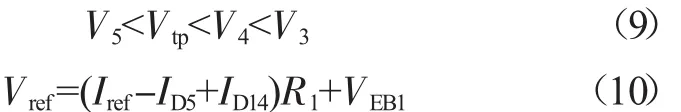

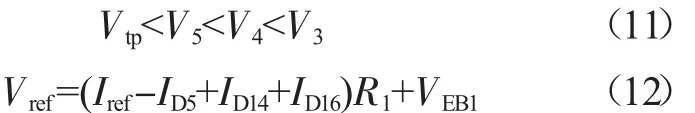

设置好 R3、R4、R5的阻值,使得温度为 T1、T2、T3时开关管 MN4、MN6、MN8 分别开启,其中-40℃< T1<T2<T3<125 ℃,Iref为流过 R1的正温度系数电流,Vtp为开关管 MN4、MN6、MN8 的开启电压。若 T<T1时,则有:

若 T1≤T<T2时,则有:

若 T2≤T<T3时,则有:

若T>T3时,则有:

4 仿真结果

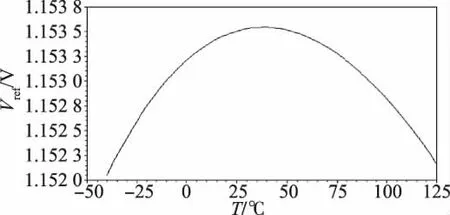

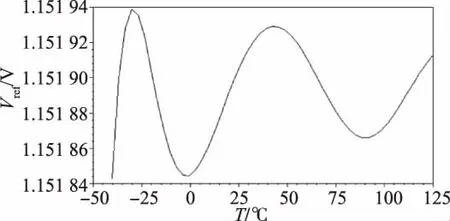

基于0.5 μm CMOS工艺库,使用Cadence Spectre软件对本文所设计的高阶曲率补偿的带隙基准电压源电路进行仿真。当电源电压为5 V、温度在-40~+125℃范围内时,基准电路补偿前后的温度特性曲线仿真结果如图3及图4所示,曲线上下起伏波动幅度可反映温漂系数大小,而温漂系数越小即基准输出电压随温度变化的起伏波动越小,表明基准输出电压具有较好的温度稳定性。由Spectre软件计算,可得未补偿时基准输出电压温漂系数为7.833×10-6/℃,而补偿后的温漂系数仅为0.5057×10-6/℃。故基准输出电压的温漂系数精度提高15.5倍,补偿电路具有良好的补偿效果。

图3 补偿前的基准输出电压温度曲线

图4 补偿后的基准输出电压的温度曲线

图5 带隙基准输出电压随电源电压变化曲线

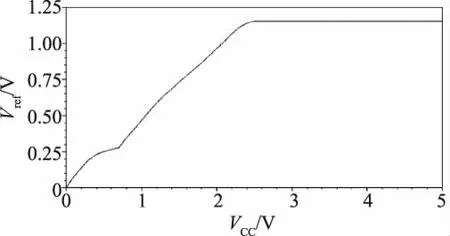

电路的直流仿真情况,在室温为27℃下,电源电压从0~5 V变化时,得到带隙基准输出电压Vref随电源电压的变化曲线,如图5所示,电路在电源电压为2.4 V时即可正常工作,带隙基准输出电压典型值为1.151 V。

图6 带隙基准源的电源抑制比曲线

在电源电压为5 V时,对带隙基准电压源的电源抑制比进行仿真,如图6所示。从图6可知,在低频段时带隙基准电压源的电源抑制比为-81.8 dB,具有良好的电源波动抑制能力。

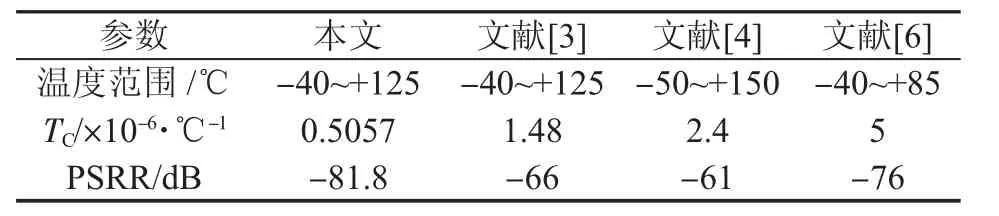

本文与其他文献中基准电压源性能的比较如表1所示。本设计基准电路具有较低的温漂系数,而且电源抑制比也比较高。

表1 基准电压源性能比较

5 版图设计

对上述整体电路的版图绘制,通过用四方交叉来实现放大器输入对管高度匹配性,在双极晶体管周围增加Dummy器件使中间有效器件刻蚀一致,以达到晶体管的匹配设计。电阻采用Poly电阻,选择合适阻值作为根器件,其他阻值通过根器件的串、并联得到,并在两端增加Dummy电阻以达到电阻匹配。各模块加上保护环抑制闩锁效应和噪声,再通过合理的布局布线,最终绘制的版图如图7所示,总面积为195 μm×184 μm。由于电路结构简单并且器件数目较少,所以芯片面积有较大的优化。

图7 带隙基准源版图

6 总结

本文提出的带隙基准源通过加入电流抽取与注入的补偿电路,在不同温度段对输出端电流进行抽取或注入,只抽取或注入正温度系数电流,电路结构简单且易于调试,通过调整电流镜中MOS管的宽长比,能精确地控制输出端的电流大小,有效降低了带隙基准电压源的温漂系数。在0.5 μm CMOS工艺模型下,使用Cadence Spectre软件对电路进行仿真。电源电压为5 V,温度在-40~+125℃范围内,基准电压源的温漂系数仅为0.5057×10-6/℃,在低频段时,电路的电源抑制比为-81.8 dB。