基于OS-PWM算法的LED驱动芯片设计与实现

范学仕,唐茂洁,曾 忠

(中国电子科技集团公司第五十八研究所,江苏无锡 214072)

1 引言

LED作为新型半导体照明材料,凭借其功耗低、寿命长、体积小、成本低、高效安全以及绿色无污染等优点,在照明设备、显示屏及其他电子设备中得到广泛应用[1-2]。小点间距LED显示屏具有无缝拼接、色彩自然真实、画面清晰、模块化维护、显示均匀性好等优点,不仅满足显示屏对高刷新、流畅无闪烁的需求,而且具有高灰阶的输出能力,可以显示高清晰、更细腻、更多色彩的图像,逐渐成为研究热点[3-4]。多路恒流LED驱动芯片通过串行数字信号和PWM配合使用,具有匹配性好、精准电流控制、高灰度显示的特点,达到了良好的显示效果,在小点间距LED驱动芯片中得到广泛应用[5-6]。

在传统多通道恒流LED驱动芯片中,多采用PWM方式进行显示控制,通过控制LED亮/暗的时间,达到不同灰阶亮度的显示效果。当所显示的灰阶亮度较低而连续不发光时间较长时,就会出现闪烁现象[7]。在小点间距LED显示屏中,传统的PWM存在刷新率较低、灰度等级不高、低灰麻点、首行偏暗、开路十字架等亟待解决的问题[8]。张晋芳等提出通过对8421码或格雷码进行重新编码的方式将一个PWM周期重新分割为若干段,从而提高显示屏的刷新率,该方法在硬件实现上只需很小的额外消耗[9]。郑扬旗等提出了根据不同更新率划分一个PWM周期的算法,以提高刷新率,降低闪烁现象[10]。王顶提出在低灰条件下,每组数据将以优先满足多个时钟周期为基础平均分布,使模拟通道能够识别有效显示时间,从而解决LED显示屏的“麻点”问题[6]。赵肃等提出一种乱序PWM算法以提高芯片刷新率,在一定程度上提高了色彩灰度等级[11]。

本文在PWM算法的基础上提出了一种OS-PWM算法,在不改变总灰度的前提下提高了刷新率,同时对低灰麻点、首行偏暗等问题进行了算法优化。对于开路十字架问题设计了开路检测模块,内建消影电路消除鬼影。本文基于OS-PWM算法设计的LED驱动芯片最多支持32行扫16位灰度数据,16通道PWM恒流输出显示,可以有效解决传统的PWM刷新率较低、灰度等级不高、低灰麻点、首行偏暗、开路十字架等问题,并在实际样片中得到验证。

2 OS-PWM算法实现

2.1 传统PWM算法

在传统LED驱动芯片中,多基于外置PWM和内建PWM两种方式进行显示控制。外置PWM利用外部控制器来控制每颗LED灯珠的导通时间,使LED屏表现出期望的亮度和灰度。而内建PWM只需固定传递灰度数据,其LED灯珠的导通时间由驱动芯片内部的计数器GCLK进行控制,无需外部控制信号,较外置PWM提高了刷新率。如图1所示,以4位灰度数据4’b0101为例,具有16级灰度,T为一次显示周期,t为每一个小时钟周期,T=15t。在外置PWM控制系统中,一组数据的发送需要分4次完成,每次传输一位数据,考虑到计数时间,这就导致时序的浪费和刷新率的降低;内建PWM中驱动芯片自带计数功能,一次就可以发送完一组数据。较外置PWM,内建PWM设计更加容易,刷新率高。但同样存在集中显示的问题,整体刷新率仍然较低。

图1 外置PWM与内置PWM显示原理

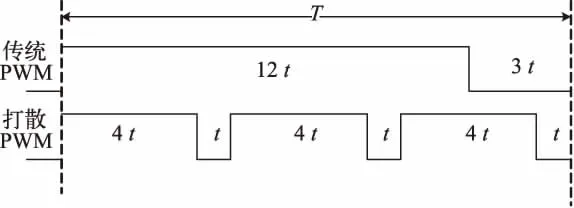

打散PWM是基于传统PWM功能的改进,其原理是将一组数据的导通时间打散成几个较短的时间段,每个较短的时间段均保持原先的占空比,以增加LED显示屏的整体刷新率。内建的SPWM技术将原本每个计数周期T从亮到灭的过程方式,平均打散成多个等份并维持原先未打散前的占空比。如图2所示,以4位灰度数据4’b1100为例,根据二进制位权机制,通过时间占空比显示其灰度,即一组数据周期需要点亮LED的时间长度为12t,熄灭时间为3t;而根据SPWM的工作原理,则将点亮时间平均打散为3个等份,每份 5t,亮灭 1t,总的占空比保持不变(4:1),总点亮时间依然是12t,从而在不影响灰度和亮度的情况下提高了LED显示屏的刷新率。

图2 打散PWM显示原理

2.2 OS-PWM算法

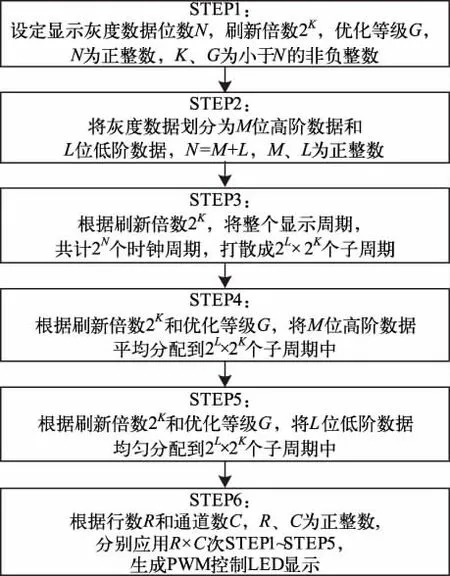

在数字PWM波形的上升沿和下降沿,如果边沿倾斜很小,模拟通道将不能快速反映数字信号的变化,另外在每颗芯片之间或者芯片通道之间的工作过程不可能完全一样,产生的脉冲倾斜也将不同,由此会在LED显示屏上产生“麻点”现象。这种情况在低灰条件下更为明显,因为打散的脉宽将更小。本文采用的OS-PWM算法是在打散PWM算法的基础之上,增加等级优化功能,在不改变总灰度的前提下提高刷新率,使显示画面更加清晰、细腻,同时在低灰条件下进行等级优化,有效解决低灰色块、偏色、麻点、第一行偏暗等问题。该算法流程如图3所示,在本文中的具体步骤为:

(1)16 位二进制灰度数据 D15D14…D1D0,由外部输入至驱动芯片中,范围为0~65535,刷新倍数2K=1/2/4/8倍,为在打散成64个子周期的基础上进一步打散提高的刷新倍数,优化等级G=0/1/2/3,要求每个子周期中每组PWM脉冲不小于设定的参考时钟周期数1/2/4/8个GLCK。

(2)将灰度数据划分为10位高阶数据和6位低阶数据,每个打散子周期的时钟周期数为1024个GCLK,整个显示周期最小打散的子周期个数为64。在设计中定义一个10位的计数器CNT1用于计数每个子周期时钟周期数,6位的计数器CNT2用于计数打散的子周期个数,优先计数CNT1,在每个时钟上升沿加1,当CNT1溢出时CNT2自动累加。

(3)根据刷新倍数,将整个显示周期打散成64/128/256/512个子周期,此时每个子周期的时钟周期数为1024/512/256/128个,整个显示周期依旧为65536个GCLK。

(4)根据刷新倍数和优化等级,将10位高阶数据平均分配到64/128/256/512个子周期中,每个子周期中PWM脉冲个数为TM=D1529-K-G+D1428-K-G+…+D6+K+G20,在每个子周期中,CNT1从0-TM-1依次输出PWM脉冲。

(5)将剩余6位低阶数据均匀分配到64/128/256/512个子周期中,此时每个子周期中PWM脉冲个数TL不超过1/2/4/8个,并按照均匀分配原则分布到各子周期中,其均匀分布原则为按照CNT2[0:5]//{CNT[9],CNT2[0:5]}/{CNT[8:9],CNT2[0:5]}/{CNT[7:9],CNT2[0:5]}顺序,在 CNT1 为 TM时,依次将TL个PWM脉冲输出。

(6)根据行数32和通道数16,分别应用32×16次步骤(1)~(5),生成 PWM 控制 LED 显示。

图3 OS-PWM算法流程

3 驱动芯片设计与实现

3.1 总结架构设计

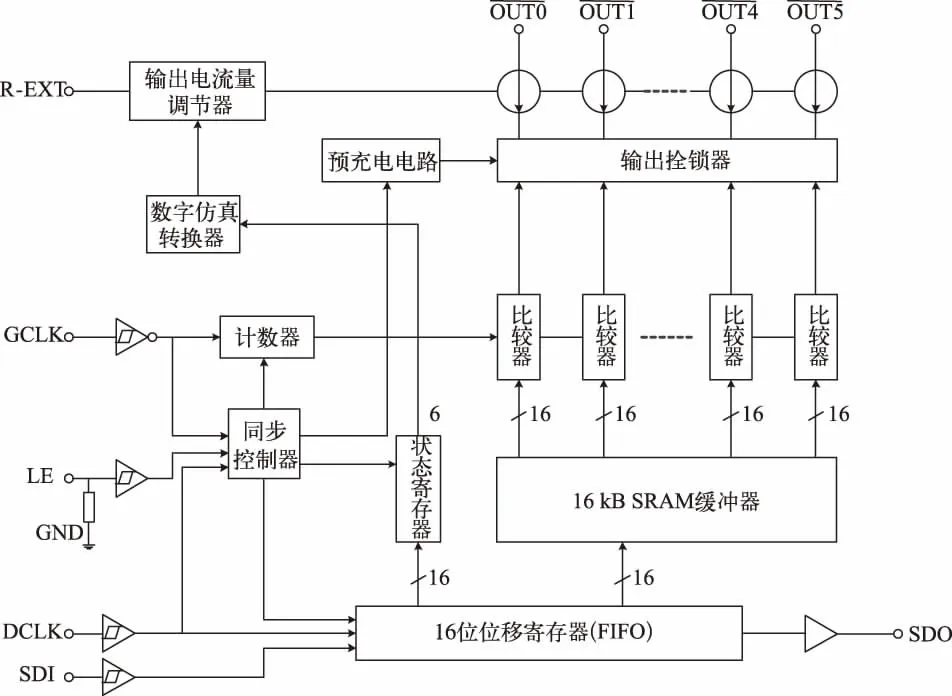

图4所示为本文设计的32扫16通道恒流LED驱动芯片的整体结构图。R-EXT为外挂电阻输入端,可调节输出端恒流值;GCLK为灰度显示周期;DCLK为数据时钟,用于写入数据或指令;LE为数据与指令的锁存端,不同的LE长度代表不同指令;SDI为串行数据输入端;SDO为串行数据输出端;GND为接地端;OUT0~OUT15为16通道的恒流输出端。整个芯片包括数字和模拟两个部分,模拟部分配合数字部分产生特定大小恒定的输出电流,包括基准、振荡器、输入输出保护(ESD)、过温保护、输出电流调节、输出电流镜像等模块。数字部分主要包括同步控制器模块、寄存器配置模块、移位寄存器模块、SRAM缓冲器模块、开路功能模块和PWM生成模块等。

在图4中,输出电流调节器代表的就是芯片的整个模拟部分,比较器与16位计数器则构成OS-PWM信号的输出模块,控制器控制整个芯片各个模块之间的协调工作,对状态寄存器数据的读写依靠16位移位寄存器来完成,灰阶数据缓存的更新方式依赖于状态寄存器内数据位的具体数值。通过移位缓存器将串行数据转换成并行数据输入灰阶数据缓冲存储器当中,然后调制成OS-PWM信号进行输出。每个通道间的电流大小不受负载的影响,透过外接电阻(REXT)的大小以及存储于状态寄存器的8位电流增益数值来调整输出电流的大小。

图4 LED驱动芯片整体架构图

3.2 同步控制器模块设计

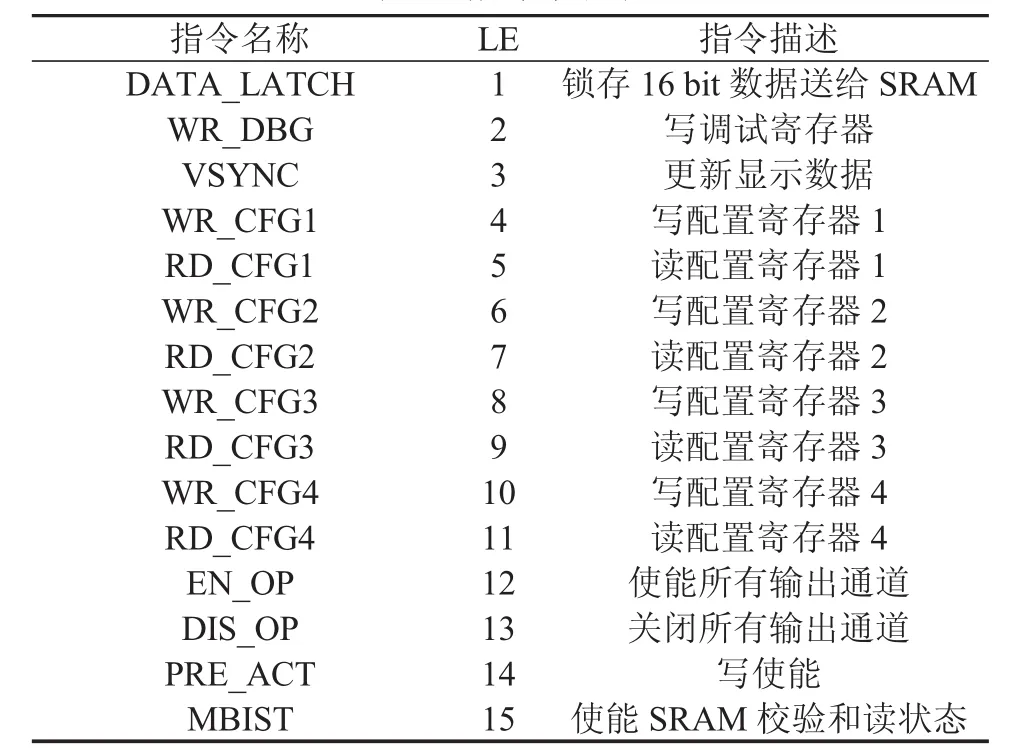

同步控制器模块由LE指令译码模块和控制逻辑模块两部分组成。LE指令译码模块为整个芯片工作模式的设定提供外部操作接口,主要通过LE和DCLK两个信号产生全局的控制信号。根据LE高电平期间DCLK上升沿个数,译码成相应的控制指令,如表1所示。在每帧开始发送前,需要先发送PRE_ACT和EN_OP指令,然后再配置寄存器,配置每个寄存器前也需要先发PRE_ACT。

控制逻辑模块主要产生SRAM行列计数使能信号控制SRAM地址变换,行扫换行信号控制多行显示时不同行之间的切换,消影控制使能信号控制消影在PWM输出或停止时是否有效,PWM刷新倍率根据需求自由配置成1/2/3/4倍刷新,低灰白平衡使能信号控制低灰白平衡功能开启和关闭,消影时间控制信号用于消除下鬼影。

表1 指令系统表

3.3 寄存器模块设计

寄存器模块分为移位寄存器和状态寄存器。16位移位寄存器的主要功能是将串行输入的数据转换成并行数据传输至PWM信号发生模块的缓存器、状态寄存器的数据读取和测试调试模块;通过SDO端口可以将移位寄存器内的数据串行发送至下一芯片,完成芯片的串联使用。16位移位寄存器由D触发器级联,在DCLK的上升沿触发,将16位数据依次移位,最后根据LE译码指令进行锁存,根据输入的数据类型和译码指令传输至相应模块进行后续操作。

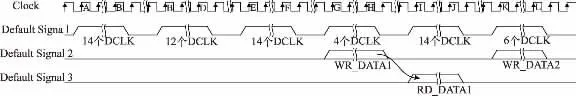

状态寄存器包含了芯片配置信息、功能配置以及测试信息,共5组16位寄存器,通过LE和DCLK的适配命令,通过移位寄存器实现对状态寄存器的读写操作。配置寄存器的时序如图5所示,具体步骤如下:

(1)时刻A到B,发送PRE_ACT指令(14个DCLK的LE高电平);

(2)时刻C到D,发送EN_OP指令(12个DCLK的LE高电平),使能通道;

(3)时刻E到F,发送PRE_ACT指令(14个DCLK的LE高电平);

(4)时刻G到H,发送WR_CFG1指令(4个DCLK的LE高电平),将16位串行数据WR_DATA1通过SDI写入寄存器1;

(5)时刻 I到 J,发送 PRE_ACT指令(14个DCLK的LE高电平),此时SDO串行输出RD_DATA1;

(6)时刻 K到L,发送 WR_CFG2指令(6个DCLK的LE高电平),将16位串行数据WR_DATA2通过SDI写入寄存器2;

(7)重复I到L,依次写入寄存器3和4的值。

图5 寄存器配置时序图

3.4 SRAM缓冲器模块设计

本文设计的驱动芯片内建 16 kB(4×32×8×16 bit)双SRAM(SRAM 1/3和SRAM 2/4)的创新架构,用于缓存多行灰度数据,有4个完全一样的SRAM,IO接口位宽为16位,深度256(32行8通道),平均分成SRAM 1/3和SRAM 2/4两组。当主机通过DCLK将灰度数据写进SRAM 1/3时,在SRAM 2/4中的灰度数据将通过GCLK产生PWM波形驱动LED显示屏,两者同时工作,互不影响。如果SRAM 1/3写满和SRAM 2/4读空,将会通过指令VSYNC交换两组SRAM的功能,即SRAM 1/3转换为发送显示数据,SRAM 2/4转换为接收主机数据,依此反复执行,从而实现利用双SRAM结构存储和处理灰度数据的目的,使数据能够“流水线”式读写,最大程度节省数据频带。

本芯片支持1~32扫任意配置的LED显示屏,并仅需传送一次完整的帧数据,就可以将灰度数据储存在芯片内的SRAM中。此方法不但能够节省数据的频带,也可以在非常低的时钟频率下达到高灰阶的显示效果,即显示系统的控制器只需提供数据给驱动芯片,芯片就可以通过输入的灰度数据来调整相应LED灯珠的亮度,并使每个输出通道表现出16位(65536种灰阶)的颜色变化。

在灰度数据存储进SRAM之前,该驱动芯片有三种类型的数据处理方式,分别为:

(1)根据状态寄存器1中的GRAY_DIS位(REG1[2:0]),当灰度数据值在0-GRAYDIS时灰度数据将被直接置换成GRAY_DIS。比如GRAY_DIS的值为3,写进SRAM的数据灰度值为1或2时将被直接置换成3;若灰度数据大于GRAY_DIS中的数据,则原数据不做变化。

(2)状态寄存器 1中的 OPEN_DEF位(REG1[14])为1时,开路检测功能有效。若驱动芯片的一个通道被检测为开路状态,所有写入该通道的灰度将直接清零。

(3)如果是MBIST模式,则输入到SRAM的数据为固定值{8{mbist_data}}。

3.5 PWM信号发生模块设计

PWM信号发生模块的功能是将亮度控制信号即灰度数据运用OS-PWM算法转换成PWM信号,并传输至模拟部分,控制输出电流的通断。其主要有一个16位的计数器,由时钟GCLK控制计数间隔,通过同步控制模块进行控制;16个比较器,比较缓存中的灰度数据与计数器输出数据的大小,输出高低电平;输出栓锁器用来缓存灰度数据,提高芯片的工作性能以及稳定性。

将16位数据分为10位的高阶数据和6位的低阶数据。由于高10位的高阶数据在图像显示中占有主要作用的地位,故采用将高阶数据计数打散的方式来提高LED显示屏的刷新率。高阶数据的计数周期打散后将重复计数多次,再加上一次低阶数据的计数周期就可以达到和未分解的PWM一样的分辨率。如图6所示,将一个显示周期T分为64等分,每份以10位1023 t为基础,和一个低位数据的计时时钟周期t组成1024个计数周期。这样总计仍为1024 t×64=65536t=T,总灰度不变,但刷新率提高了64倍。同理,打散成128/256/512组,即刷新倍数K为1/2/3时,也提高了相应的倍数。

本文增加了优化等级G,在低灰条件下,设定每个子周期最小PWM脉冲数,如图7所示,当优化等级G=1时,每个子周期的最小PWM脉冲数为2个GCLK,当优化等级G=2时,每个子周期的最小PWM脉冲数为4个GCLK,当优化等级G=3时,每个子周期的最小PWM脉冲数为8个GCLK,增加通道打开时间,提高亮度,增强显示效果,解决“麻点”现象。

图7 OS-PWM算法优化等级显示控制图

对于LED显示首行偏暗的现象,本文增加计数器反向计数设计,在通道打开前,提前预留时间,图8中预留12个GCLK时间,降低列上的电压,使电容提前放电,有助于解决首行偏暗的问题。当灰度值特别小时,图8中输入灰度大小为3,低灰显示效果较差,本文增加置换低灰度值设计,设置一个灰度阈值,图8中该阈值为7,当灰度值低于该阈值时,将该阈值作为该灰度值使用,可有效地改善低灰显示效果。

图8 OS-PWM算法反向计数和低灰度替换控制图

3.6 其他模块设计

其他模块主要包括开路检测模块和测试调试模块。

开路的LED灯珠会影响周围灯珠的显示效果,容易产生“开路十字架”问题。通过检测开路LED灯珠,将已开路的LED灯珠信息记录下来,在显示过程中不点亮开路LED灯珠,由此从根本上解决了“开路十字架”的问题。

本文的开路检测由配置REG1[14]的OPEN_DEF位及REG4[7]的OPEN_SCAN位控制。其中OPEN_DEF为开路检测总开关,一般全程开启;OPEN_SCAN为开路复位重置,在开启新的开路检测时会打开,检测完成后关闭。当我们检测到通道x为开路时,输出会自动将第x个通道屏蔽。

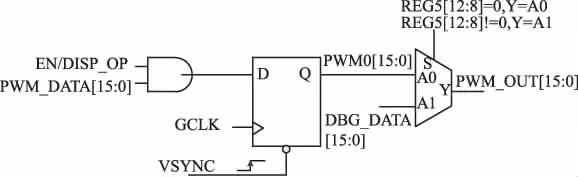

测试调试模块用于工作模式选择以及相关测试调试模式,图9所示为工作模式选择图,PWM_DATA[15:0]是PWM输出的显示数据,EN/DIS_OP是通道使能信号,VSYNC是数据同步信号,它们用来产生PWM0[15:0]信号,正常工作时,REG5[12:8]=00,选择PWM0信号输出到DRV模块,去驱动LED屏,而当REG5[12:8]是数值(01~1F)之间任何一个值时,电路进入DEBUG工作模式,一共有31种选择,此时把DEBUG_DATA[15:0]输出到16通道输出端口OUT[15:0]。

图9 工作模式选择图

4 结果及分析

4.1 样片介绍

本文设计的32扫恒流PWM输出LED驱动芯片是一款全彩LED显示屏驱动芯片,内建PWM高刷新算法,专门针对小间距显示屏存在的低灰问题做出优化处理,可以有效地解决传统的PWM刷新率较低、灰度等级不高、低灰麻点、首行偏暗、开路十字架等问题。样片整体布局如图10所示。

图10 样片整体布局

4.2 实验结果分析

通过对芯片内部各个模块单独的设计仿真,以不同的状态值实现对数据流的控制,在PSM输出端得到灰度控制信号,驱动LED显示屏;最后整合各个部分设计模块到顶层TOP模块,基于LINUX系统,进行全局仿真。仿真实验中,重点实现16位数据PWM灰度输出,并完成对状态转移的控制,主要仿真功能可分为5类,如表2所示。

表2 仿真测试表

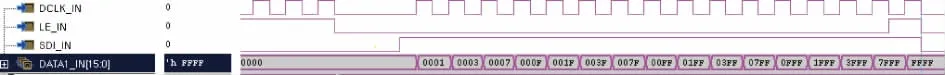

图11所示为寄存器配置仿真图,依次读出寄存的复位值为:0x1F00、0x7FFF、0x4007、0x0 和 0x8。根据输入的不同LE指令,在LE的下降沿将数据依次写入相应寄存器。写入数据依次为0xAAAA、0x5555、0xFFFF、0x0000,由于各寄存器的最高位为保留位,实际写入值依次为 0x2AAA、0x5555、0x7FFF、0x0000。

图11 寄存器配置仿真图

图12为数据0xFFFF锁存,输入写使能指令PRE_ACT,输入通道使能指令EN_OP,再次输入写配置寄存器指令PRE_ACT,输入指令DATA_LATCH,则该指令LE信号下降沿前的16位数据将打入RAM中。

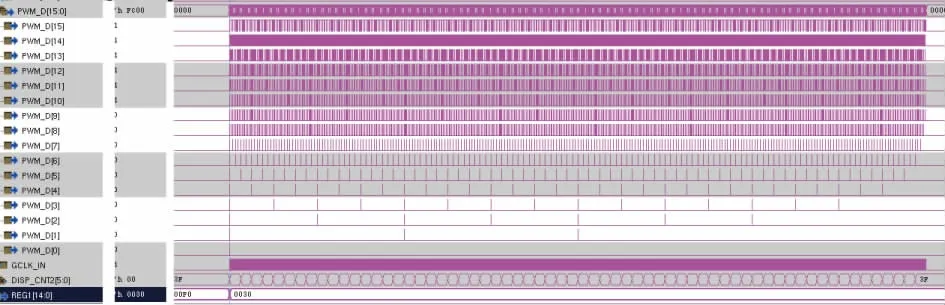

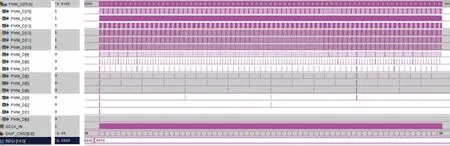

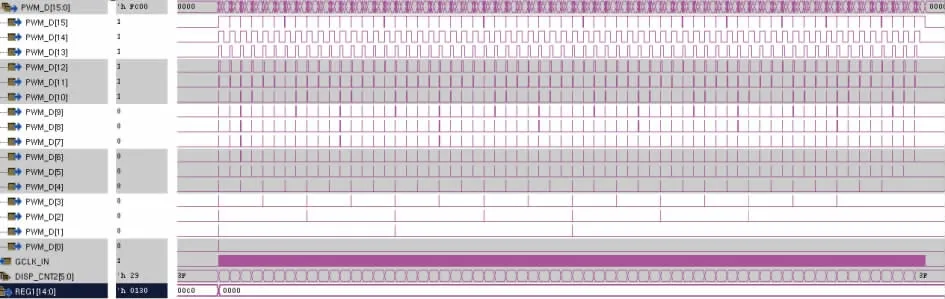

图13到图15为应用OS-PWM算法之后的PWM输出波形图。通道15~0写入的数据依次为0xFFFF、0x7FFFF、…、0x3、0x1,在图 13 和图 14 中,刷新倍率相同,优化等级不同,优化等级1时最小PWM脉冲个数为4;在图13、图15中,优化等级相同,刷新倍率不同,图13刷新倍数提高了8倍。

图12 数据锁存0xFFFF

图13 OS-PWM算法刷新倍率8,优化等级0

图14 OS-PWM算法刷新倍率8,优化等级1

图15 OS-PWM算法刷新倍率1,优化等级0

图16所示为通道15~0依次开路检测仿真图。配置REG1[14]的OPEN_DEF位及REG4[7]的OPEN_SCAN位控制。其中OPEN_DEF为开路检测总开关,一般全程开启;OPEN_SCAN为开路复位重置,在开启新的开路检测时会打开,检测完成后关闭。当我们检测到通道x为开路时,输出会自动将第x个通道屏蔽。

图16 通道15~0开路检测

仿真结果符合预期,本文所设计的芯片已完成流片,芯片尺寸为 1288 μm×1266 μm,测试验证结果与仿真一致。

5 总结

本文针对小间距LED显示屏中存在的刷新率较低、灰度等级不高、低灰麻点、首行偏暗、开路十字架和下鬼影等问题,基于传统PWM算法,提出了OS-PWM算法,并设计了一款多通道恒流LED驱动芯片。针对刷新率较低、灰度等级不高的问题,通过OS-PWM算法将显示周期均匀打散,在不影响总体灰度的前提下,提高刷新率,同时支持多灰度等级;针对低灰麻点增加了等级优化,提升低灰显示效果;针对首行偏暗的问题提出了反向PWM计数方法,预留时间使电容提前放电,有助于改善该问题;针对开路十字架问题,内建开路检测模块,从根本上屏蔽了这一问题。实验测试结果证明了本文设计的正确性和合理性。