碳化硅MOSFET特征参数随温度变化的比较研究

江芙蓉,杨 树,盛 况

(浙江大学电气工程学院,杭州 310027)

相比于传统硅(Si)材料,碳化硅 SiC(silicon carbide)材料因其更宽的禁带宽度(3.26eV)、更高的热导率和更高的临界击穿场强,在大功率开关电路和电力系统应用领域得到了广泛的关注[1-2]。SiC功率器件最突出的性能优势在于其高压、高频和高温工作特性,可以有效地降低电力电子系统的功率损耗。目前,国际上以美国Cree公司和日本Rohm公司等为代表的半导体器件厂商,已在SiC MOSFET器件产品化道路上取得了巨大进展。目前,已推出沟槽型SiC MOSFET的只有Rohm、Infineon公司等少数厂商,商用SiC MOSFET产品绝大多数为N沟道平面垂直结构。在2010年和2013年分别生产出第一代和第二代1 200V SiC MOSFET后,Cree公司于2015年推出了基于第三代技术的900 V平面型SiC MOSFET。作为行业内第一款900 V SiC MOSFET,这一产品不仅拓展了SiC MOSFET产品的电压等级,更表现出比同等级Si基超级结MOSFET更低的导通电阻[3]。

由于半导体材料对温度变化十分敏感,环境温度的改变对SiC功率器件的工作特性有着不可忽略的影响。已经有研究工作表明,MOS结构中SiO2/SiC界面处存在的高浓度的界面陷阱,是导致SiC MOSFET的阈值电压随温度升高而变小的主要原因[4]。虽然SiC材料的热氧化工艺与Si材料相似,但因为碳原子的存在,在SiC氧化层生长的过程中其SiO2/SiC界面产生了比SiO2/Si界面高近3个数量级的界面陷阱[5]。对于平面型SiC MOSFET来说,SiO2/SiC界面品质至关重要,直接影响着沟道的电子迁移率和场氧化层的可靠性[6]。本文通过对Cree公司第一、二、三代SiC MOSFET进行从低温-160℃到高温200℃全温度范围内的工作特性测试和对比分析,提取出三代样品的一系列特征参数,然后通过计算机数值仿真的手段,比较研究了三代产品SiO2/SiC界面态密度及其对器件性能的影响。

1 测试方法

本文选取的测试样品为Cree公司第一、二、三代SiC MOSFET产品,型号分别为CMF20120(80 mΩ,1 200 V,简称 CMF),C2M0080120D(80 mΩ,1 200 V,简称 C2M)和 C3M0065090D(65 mΩ,900 V,简称C3M)。对每个型号的MOSFET分别取三个分立器件进行全温度范围内的重复测试,考虑到同一型号的不同器件在常温下的阈值电压也会有不同,选取其中一组测量数据作为代表性结果。测试环境为计算机控制温度的测试箱,低温由通入液氮来实现。将待测器件置于其中,以开尔文四探针法接线,可以消除引线和接触电阻阻抗的影响。测量仪器为Tektronix®371A大功率晶体管测试仪,该仪器是应用漏源极加脉冲电压测试方法,脉冲宽度为200 μs,以确保器件自身发热所引发的温度变化控制在可忽略的范围内。测试时先将温度降至约-180℃,待温度稳定后保持10 min,再以每升高20℃作为一个温度点,在温度稳定10 min后,再进行脉冲信号的输出特性测试。每一次脉冲信号可测试10个不同栅压下的一系列输出曲线,调节栅压大小及步长,实现栅压从2~20 V范围内的输出特性的测试。

2 实验参数提取

2.1 阈值电压

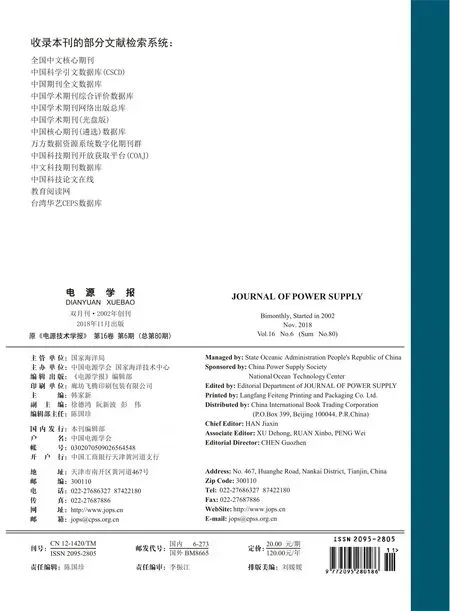

阈值电压的温度稳定性是影响器件能否满足电力电子系统处在正常工作模式的一个重要因素。图1为不同温度下CMF、C2M、C3M系列三代SiC MOSFET器件在VDS=10 V时的转移特性曲线。

在VDS=10 V时,MOSFET工作在饱和区(VDS≥(VGS-VT)),由于器件MOS结构沟道长,不考虑短沟道效应,饱和区漏源电流可表示为

式中:μn为反型沟道电子有效迁移率;L为沟道长度;W为沟道宽度;Cox为单位面积栅氧化层电容;VT为阈值电压;VDS为漏源电压;VGS为栅源电压。根据测量所得的转移曲线,可通过二次函数拟合的方式,提取出每一测量温度下的阈值电压VT。图1中图标数据点为实际测量值,实线为拟合的二次函数曲线,由图可以看出拟合结果较好。

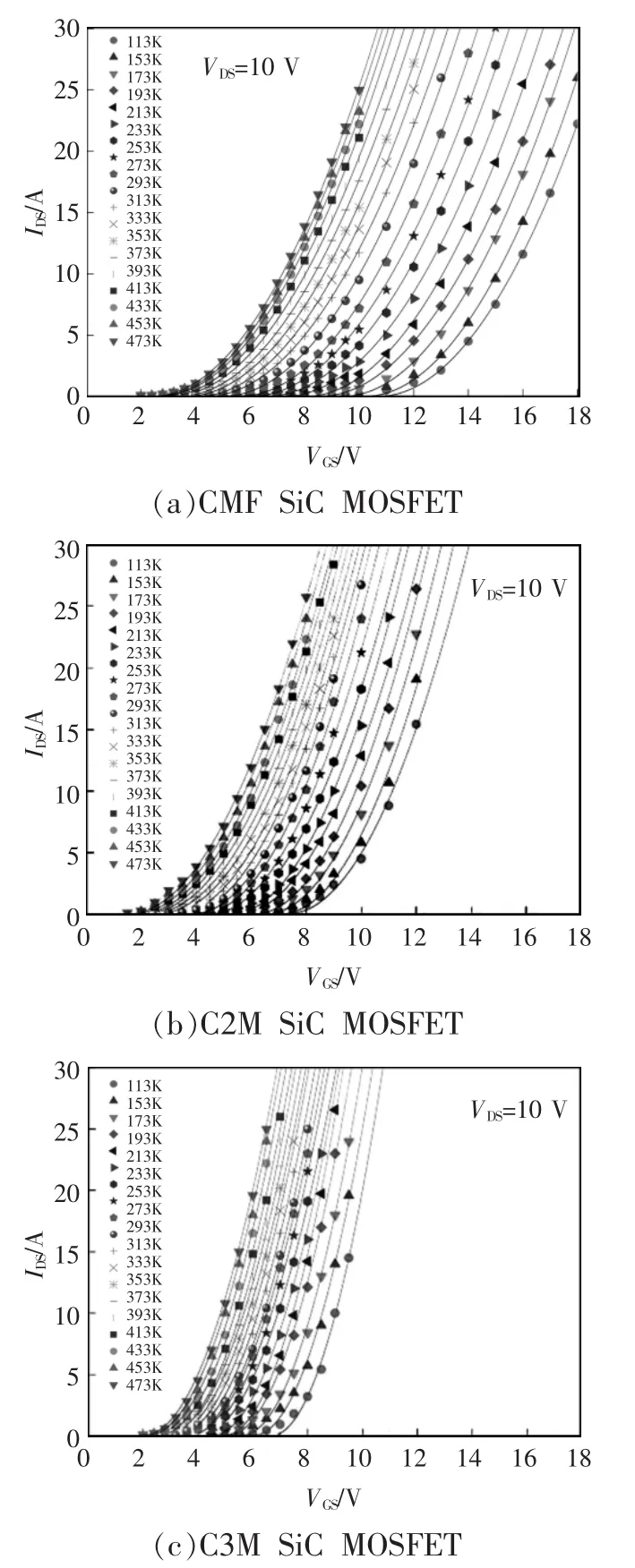

图2为在不同温度下通过转移特性拟合的方法提取出的CMF、C2M、C3M SiC MOSFET的阈值电压,可以看出阈值电压随着温度的升高而减小,且C2M、C3M的VT随着T的升高而减小的幅度比CMF有明显的下降。本研究分析认为,这主要是由于SiC MOSFET中SiO2/SiC界面品质的改善导致的,在后文物理建模部分中将具体分析。

2.2 导通电阻

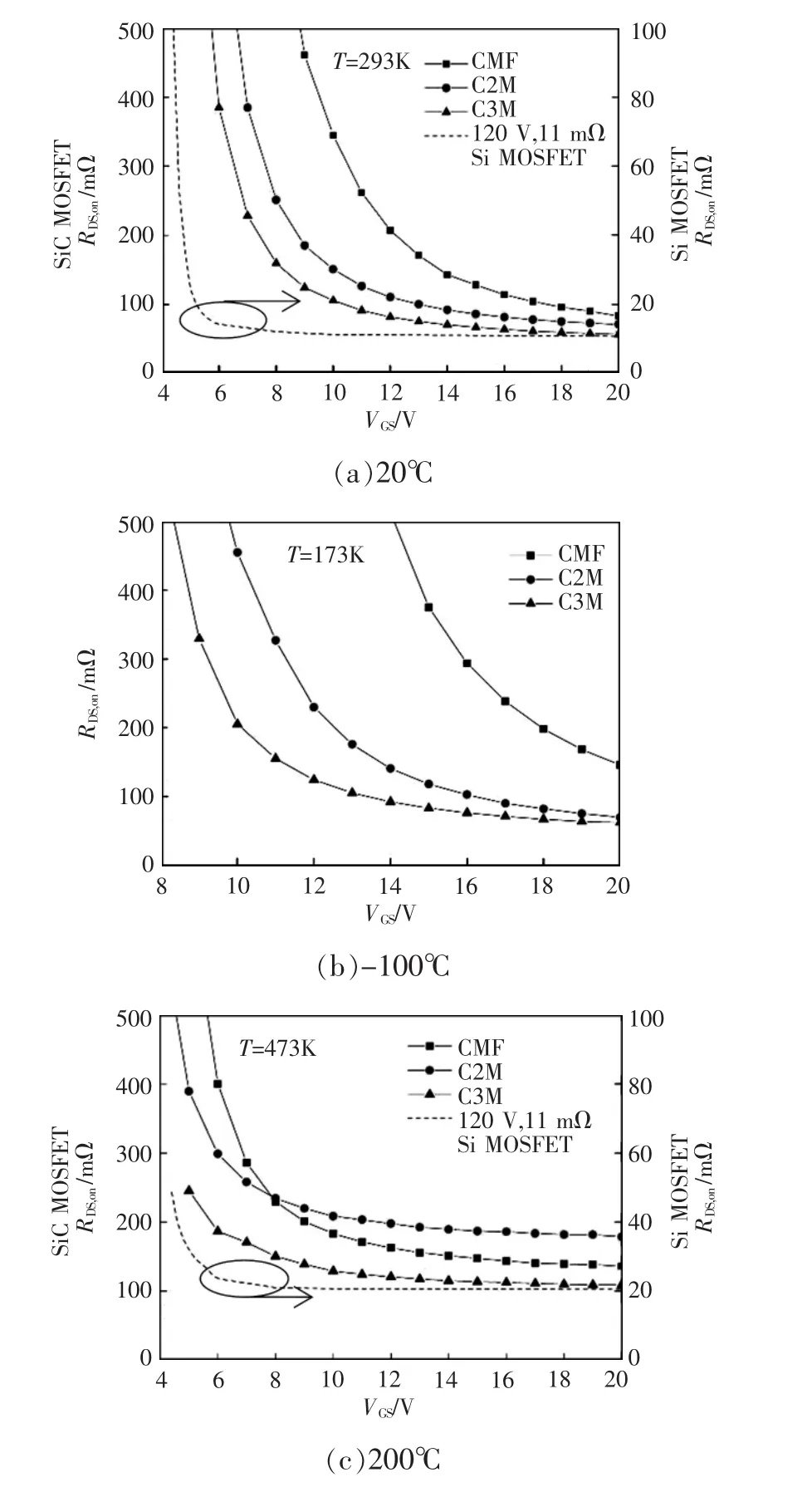

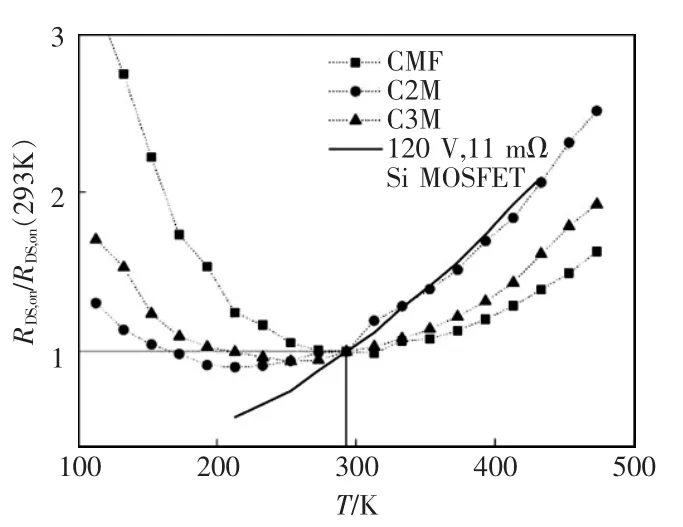

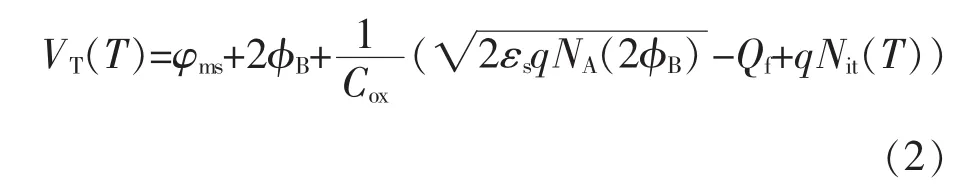

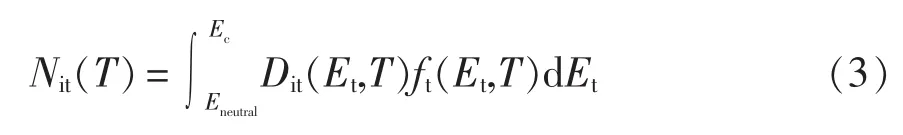

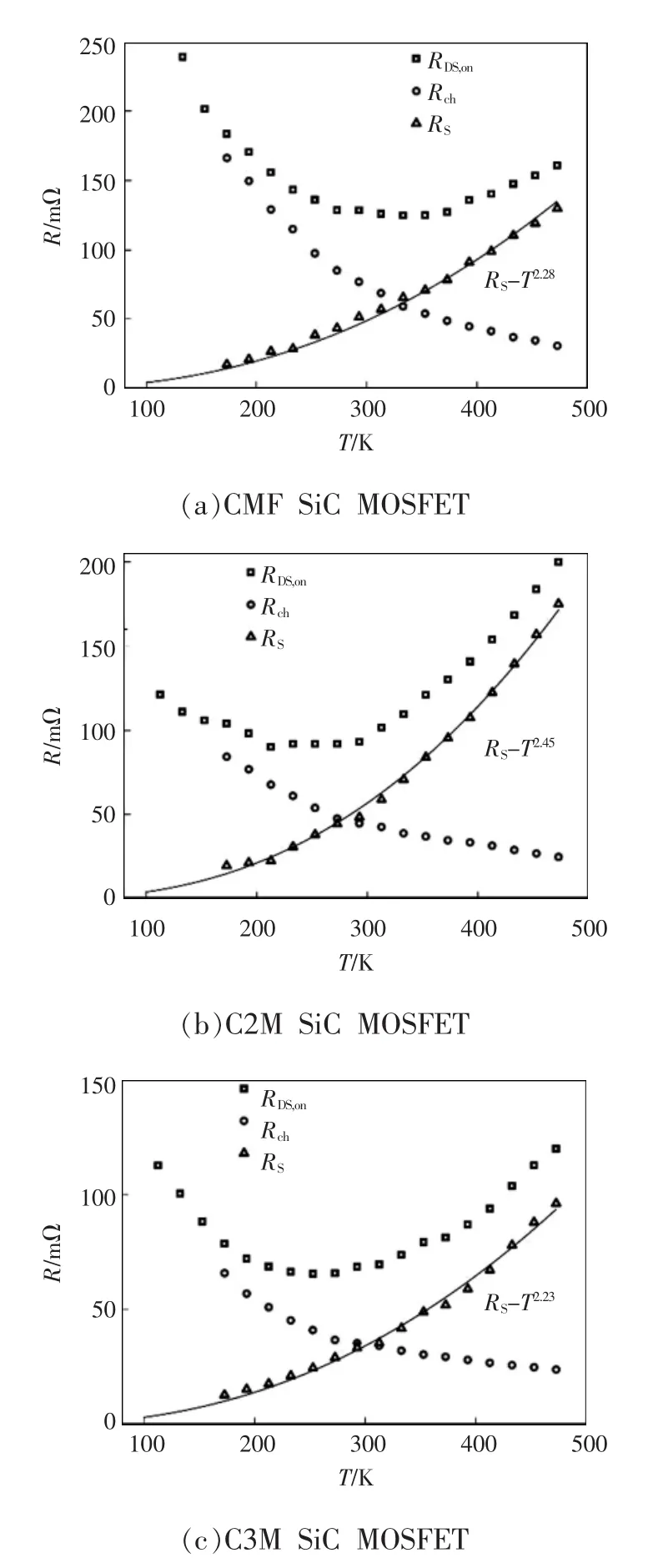

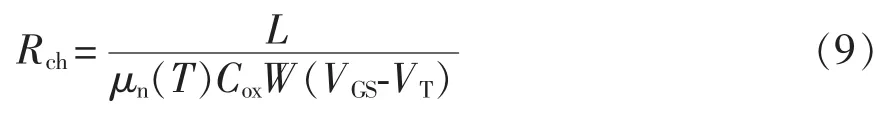

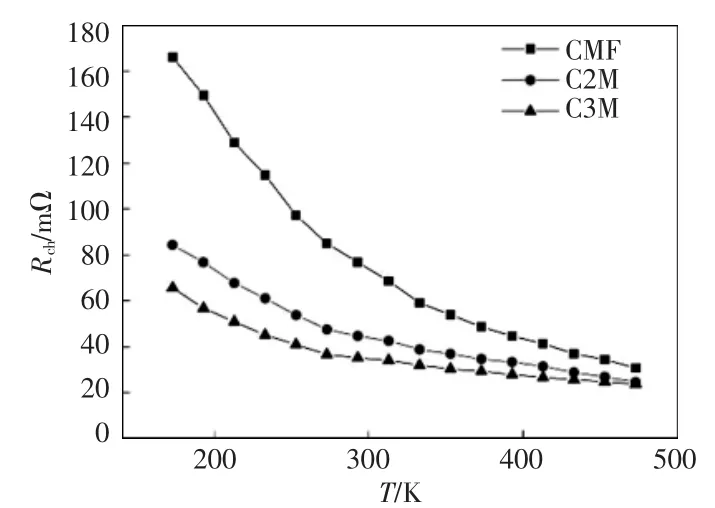

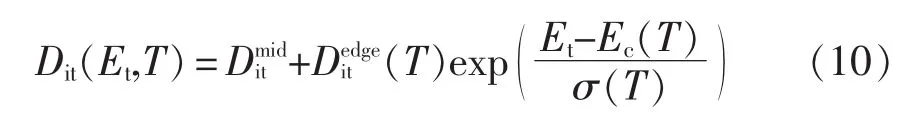

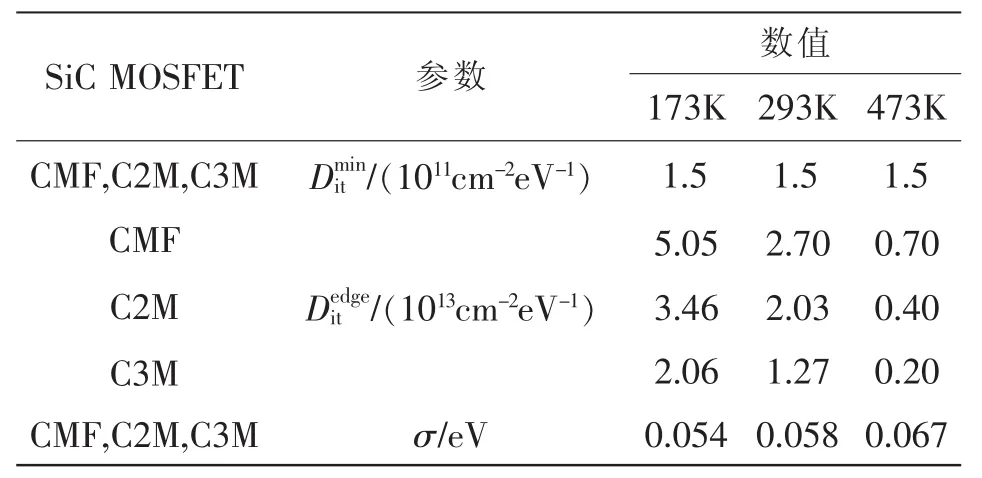

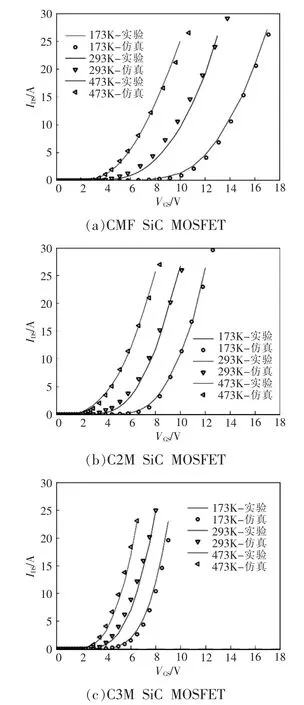

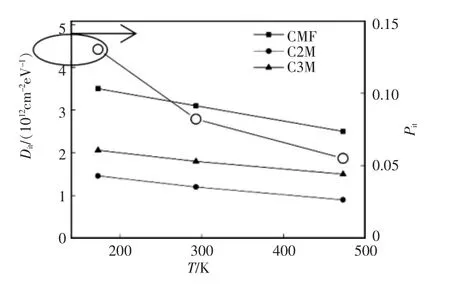

导通电阻RDS,on为影响器件工作时导通损耗的一重要特征参数,其数值会随VGS以及T的变化而改变。图3为 20℃、-100℃和 200℃下 CMF、C2M、C3M SiC MOSFET器件在线性工作区(VDS 图1 不同温度下CMF、C2M和C3M三代SiC MOSFET转移特性曲线Fig.1 Transfer characteristic curves of CMF,C2M and C3M three generations of SiC MOSFETs at varying temperatures 图2 三代SiC MOSFET阈值电压与温度关系Fig.2 Temperature dependence of VTfor three generations of SiC MOSFETs SiC的临界击穿场强为3 MV/cm,是Si的10倍,因此1 200 V的SiC MOSFET器件与120 V的Si MOSFET的漂移区厚度近似。图3(a)中,对比于常温下11 mΩ、120 V Si MOSFET的RDS,on-VGS曲线可以看出,SiC MOSFET的RDS,on对栅压变化的敏感性比Si MOSFET强。CMF SiC MOSFET的RDS,on在栅压20 V左右时仍会随着栅压的改变而变化,说明在栅压不足20 V时不能达到足够低的RDS,on。相比之下,C2M、C3M SiC MOSFET在栅压16 V左右就能得到较低的RDS,on,而Si MOSFET(图中虚线)在栅压8 V就基本稳定,说明SiC一、二、三代产品性能有明显提升,但和Si器件相比还有很大差别。 图3 在温度为20℃、-100℃和200℃时,三代SiC MOSFET RDS,on-VGS关系Fig.3 RDS,onvs.VGSat 20℃,-100℃,and 200℃ in three generations of SiC MOSFETs 图3(b)中,在低温-100℃时,CMF 的 RDS,on比常温时升高了很多,这主要是因为低温下沟道参与导电的自由电子浓度和迁移率大大降低;CMF的RDS,on随栅压下降升高得很快,相比之下C2M、C3M两代产品低温下RDS,on对栅压的敏感性都有所减弱。 图3(c)中,200℃高温时,三代 SiC 器件 RDS,on对栅压的敏感性都比常温下有所降低,接近于Si器件,说明SiC器件在高温下工作性能和Si器件没有很大差别。这是由于高温下,SiC MOSFET中的界面态在常温下俘获的电子被放出,且沟道电子迁移率增大,导通性能受界面态的影响减小。 当VGS为额定工作电压20 V时,温度变化也会引起 RDS,on改变,SiC MOSFET归一化 RDS,on-T关系如图4所示,可见SiC MOSFET三代器件的RDS,on取最小值时的温度分别为20℃、-60℃和-20℃,而Si MOSFET的RDS,on在测量温度范围内是随温度单调上升的。这是由于SiC MOSFET的RDS,on中包含的两部分电阻成分与温度的关系是相反的。 图4 VGS=20 V时SiC MOSFET归一化RDS,on-T关系Fig.4 Temperature dependence of normalized RDS,onat VGS=20 V for SiC MOSFET 基于对 SiC MOSFET三代器件 VT-T,RDS,on-T以及RDS,on-VGS的比较分析结果,SiC MOSFET进行物理建模分析进一步研究SiC MOSFET性能在不同温度下的变化。 建立阈值电压物理模型,说明其随温度变化的原因。考虑固定电荷和界面态电荷对阈值电压的影响,阈值电压可表示[7]为 式中:φms为栅材料和半导体之间的功函数差;2φB为半导体两端的电势差;为氧化层两端电势差;Cox为栅氧化层的单位面积电容;Qf为栅氧化层中单位面积固定电荷;Nit为单位面积界面态电荷数。 当VGS>VT时,半导体表面呈强反型,表面能带向下弯曲,电子占据受主态界面陷阱,此时半导体表面出现负的界面态电荷[6,8],可表示为 式中:Eneutral为界面陷阱的电中性点的能带值;Ec为导带能带值;ft(Et,T)为费米分布函数,表示某一点的界面陷阱俘获电子的概率;Dit为界面态密度的分布函数,模型参数在后文界面态陷阱密度建模部分指出。由于界面态可以被认为是一个热平衡系统,ft(Et,T)可以表示为 式中:kB为玻尔兹曼常数;0.5为简并因子[6]。 强反型时,SiO2/SiC界面存在大量的负的界面电荷,是阈值电压与温度呈负相关的主要原因[4]。比较图2CMF、C2M、C3M SiC MOSFET样品的VT随T变化趋势,可以看出,阈值电压的温度变化率dVT/dT随着产品工艺的更新换代在逐代下降。这说明SiC MOSFET产品的界面品质在逐代改善,其阈值电压对温度的敏感性也在逐代降低。 对导通电阻的组成以及各部分与温度的关系进行建模分析,解释SiC MOSFET的导通电阻随温度变化的原因。 3.2.1 导通电阻的组成 图5为平面垂直型SiC MOSFET的各部分等效电阻示意,RDS,on可表示为沟道电阻Rch和剩余电阻RS之和,其中RS包含JFET区电阻RJFET、扩展电阻RSp、漂移区电阻RDrift和衬底电阻RSub。 图5 平面垂直型MOSFET各部分电阻截面Fig.5 Cross-section of component resistances in a planar MOSFET 在实际沟道两端电压Vch很小的情况下,可认为反型区电子迁移率恒定,漏源电流[7]可表示为 式中,β为比例系数,β=μnCoxW/L。测量所得的平面垂直型MOSFET的漏源电压VDS可看作沟道两端电压Vch与剩余电阻RS两端电压之和,即 实验测得的栅压VGS、漏源电压VDS和漏源电流IDS满足 为排除不同温度下阈值电压不同所引起的导通电阻的变化,对于各温度,选取VGS-VT=10 V附近,VDS<0.5 V时输出特性的测量数据VGS、VDS和IDS拟合式(7),可提取出比例系数β和剩余电阻RS。 图6为 CMF、C2M、C3M SiC MOSFET在 VGS-VT=10 V时的导通电阻RDS,on、拟合所得的RS以及二者相减所得的沟道电阻Rch。从图6可以看出,常温下,1 200 V电压等级的第一代CMF SiC MOSFET和第二代C2M SiC MOSFET的 RS数值相近,而900 V电压等级的第三代C3M SiC MOSFET的RS比前两代小。对于电压等级为1 200 V和900 V的SiC MOSFET器件来说,RS中漂移区电阻RDrift占主要部分[3]。 图6 CMF、C2M和C3M三代SiC MOSFET RDS,on,RS和Rch与温度关系Fig.6 Temperature dependence of RDS,on,RS,and Rchfor CMF,C2M,and C3M three generations of SiC MOSFETs 从-160℃到高温200℃,RDS,on随温度升高是先减小后增大的,这是由于组成RDS,on的两部分电阻随温度变化的趋势是相反的,RS与T呈正相关,而Rch与T呈负相关。 3.2.2 漂移区电阻 在低掺杂的漂移区内,体声子散射为主导的电子散射机制,电子迁移率[8]可表示为 式中:μB0为300 K时的电子迁移率;T为绝对温度;θ为经验公式参数。假设杂质完全电离的情况下,漂移区电阻RDrift理论值应正比于Tθ。考虑到RJFET、RSp和RSub的存在带来的误差,由测量结果提取出的RS与漂移区电阻RDrift并不完全一致,所以图6中三代SiC MOSFET器件的RS-T关系中,拟合参数θ值不同,分别为2.28、2.43和2.23。 3.2.3 沟道电阻 图7中环形的数据点为在不同温度下计算所得的器件完全开启状态下的沟道电阻Rch,表示[9]为 由图7中可以看出,在常温下三代产品的Rch逐代减小,且Rch随温度升高而减少的幅度也在逐代降低。当VGS-VT为一固定值且足够大时,器件处于完全开启状态,Rch与沟道电子迁移率成反比。 SiO2/SiC界面存在的大量界面态是导致SiC MOSFET沟道电子迁移率过低的主要原因[4]。在VDS较小、沿沟道方向的横向电场较低的情况下,由界面态电荷引发的库仑散射是反型层内主导的散射机制。当VGS较小时,反型电荷很少而由于俘获电子而带负电的界面态电荷却很多,因而导致可移动的电子受界面态电荷影响而发生库仑散射[10]。当VGS较大时,有相当多数量的反型电荷,可以在一定程度上屏蔽由界面态电荷引起的库仑散射,但半导体表面的电流密度很大,而表面电子仍受库仑散射影响。所以在弱反型和强反型区,由界面态引发的库仑散射均为主导的散射机制[5]。 图7 三代SiC MOSFET Rch-T关系对比Fig.7 Comparison of Rch-T among three generations of SiC MOSFETs 图8中为以20℃室温下测量值作为标准CMF、C2M、C3M SiC MOSFET的归一化沟道电子有效迁移率。已有关于SiC MOSFET沟道迁移率理论建模的研究[5,6,11]提出了多个SiO2/SiC表面库仑迁移率的数学模型,都证明了库仑迁移率是与温度呈正相关,与界面态密度呈负相关的。由于库仑散射机制的主导地位,随着界面态密度的增加,沟道迁移率温度变化率也随之增加[11]。但是因为三代芯片导通状态时有效沟道的几何参数无法获得,所以不便比较产品间沟道迁移率的绝对值的差别。图8中可以看出,在VGS-VT一定且足够大的情况下,归一化沟道迁移率随温度升高而增大的趋势在逐代降低。这一结果验证了CMF、C2M、C3M SiC MOSFET界面态密度是逐代下降,且C2M、C3M SiC MOSFET的界面品质相比CMF有很大程度的提升。 图8 三代SiC MOSFET与Si MOSFET归一化μn-T关系对比Fig.8 Comparison of normalized μn-T among three generations of SiC MOSFETs and Si MOSFET 为了验证界面态陷阱是影响SiC器件在不同温度下工作特性不同的重要原因,对SiC MOSFET器件的转移特性运用TCAD进行仿真拟合,仿真软件选用Silvaco公司的Atlas。 大量实验与理论研究结果表明,对反型沟道电子产生散射作用的,主要是禁带上半部分的类受主型界面态。一般认为类受主型界面态密度的能量分布模型[11]可以写为 式中:Dmidit和Dedgeit分别为禁带中央和导带底的界面态能量密度;Et和Ec分别为界面陷阱和导带底能量;σ为带尾衰减能量参数。禁带下半部分的类施主型界面态也可用相似形式表示。研究表明[11],Dedgeit比Dmidit大2~3个数量级,是影响界面态密度的最重要的参数。将式(10)代入式(3)中,可以得到某一温度下的界面态密度。由于SiC MOSFET中电子为多数载流子,仿真中类施主型界面态的影响可以忽略。且考虑到禁带宽度会随温度变化,其数学模型[12]为 式中:Eg,0为300 K时SiC的禁带宽度理论值,Eg,0=3.26eV;α=3.3×10-4。 通过调整仿真计算中Dmidit、Dedgeit和σ,来拟合转移特性曲线IDS-VGS。仿真中取P-well掺杂浓度为4×1016cm-3,为校正阈值电压相对值,CMF、C2M、C3M SiC MOSFET器件仿真氧化层厚度分别选择45、35、45 nm。表1为仿真拟合所得界面态模型参数,其中Dmidit和σ数值选取参考文献[11]。 图9为 VDS=10 V 时在-100℃、20℃和 200℃下三代器件转移特性加入界面态模型后仿真拟合结果,可以看出,仿真结果与实验数据拟合程度较好。 图10为仿真拟合所得第一代CMF SiC MOSFET模型界面态能量分布曲线。从图10可以看出,禁带宽度随温度下降而变宽,从而导致界面态能带分布向导带方向延伸,与此同时导带底部界面态能量密度Dedgeit也相应增大。σ决定界面态能量分布曲线靠近带尾部分变化趋势的,σ越大界面态能带尾部曲线越平缓。随着温度的升高,界面态能带尾部或有变宽的趋势,所以σ增大[11]。因此对于同一器件,由式(3)可得,温度升高会使类受主型界面态俘获电子概率降低,从而导致阈值电压大幅降低。 表1 三代SiC MOSFET界面态模型仿真参数对比Tab.1 Comparison of simulation parameters of interface state model among the thind generation SiC MOSFETs 图9 CMF、C2M 和C3M三代SiC MOSFET转移特性数值仿真和实验对比Fig.9 Simulation and experimental comparison of transfer characteristics among CMF,C2M,and C3M three generations of SiC MOSFETs 图10 第一代CMF SiC MOSFET界面态能量分布Fig.10 Distribution of interface state energy for the first generation CMF SiC MOSFET 图11为仿真所得 CMF、C2M、C3M SiC MOSFET器件模型在完全开启状态下,在受主态界面陷阱密度的平均值Dit和界面陷阱俘获电子的概率Pit。如图11所示,三代SiC MOSFET仿真所得Dit随温度升高变化不大,可推测虽然界面态能量的分布情况在温度升高时由于禁带宽度变窄而有所不同,但界面态密度平均值变化不大。图中环形所示分别为3个仿真温度下界面陷阱俘获电子的概率Pit,可以看出在温度降低时Pit增大,从而推测Dit变化不大的情况下界面态陷阱俘获的电子数目增多,可能是导致器件转移曲线在温度降低时变缓的原因。仿真结果进一步验证了三代SiC MOSFET产品SiO2/SiC界面陷阱密度在逐代下降。 图11 三代SiC MOSFET Dit-T关系对比Fig.11 Comparison of Dit-T among three generations of SiC MOSFETs 目前SiC MOSFET已在中低压领域实现了产业化,国际上各大功率器件公司都在陆续推出更优性能的商业化产品。本文以Cree公司CMF20120D、C2M0080120D和C3M0065090D分别作为其三代SiC MOSFET商业器件的代表,完成了从-160℃到200℃全温度范围的静态工作特性测试,并提取出各个温度下的VT与RDS,on,比较分析T与三代产品VT和RDS,on关系,以及不同温度下RDS,on随VGS的变化情况。 SiC MOSFET中SiO2/SiC界面存在的大量的界面陷阱,是导致阈值电压随温度下降而升高的主要原因。低温下沟道电阻的增加,也主要是因为界面态导致沟道迁移率下降。通过建立物理模型的方式,比较CMF、C2M、C3M三代SiC MOSFET产品阈值电压、沟道电阻的温度变化率,可以发现SiO2/SiC界面品质在逐代提升。 通过建立界面态能量分布模型,利用TCAD仿真,拟合三代SiC MOSFET分别在-100℃、20℃和200℃时的转移曲线,定性地比较了三代产品界面态能量分布密度,验证了工艺水平的提高促进了SiC MOSFET产品的更新换代,SiO2/SiC界面态密度在逐代减小,阈值电压对温度的敏感性也在逐代降低。

3 物理模型分析

3.1 阈值电压物理模型

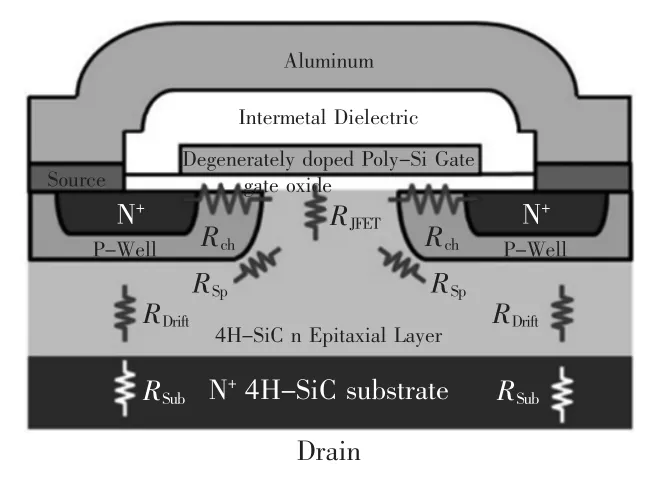

3.2 导通电阻物理模型

4 界面态陷阱密度仿真建模

5 结论