一种捷变频宽带微波频率合成器的设计

杜 勇,李光灿,廖海黔

(贵州航天计量测试技术研究所 5室,贵州 贵阳 550009)

一种捷变频宽带微波频率合成器的设计

杜 勇,李光灿,廖海黔

(贵州航天计量测试技术研究所 5室,贵州 贵阳 550009)

针对当前多数宽带捷变频频率综合器电路结构复杂、成本高等缺点,文中通过将高参考时钟的DDS倍频后与宽环路带宽、高鉴相频率的锁相环电路上变频,再通过滤波器组件输出的频率合成方式,实现了频率范围覆盖8~12 GHz的宽带捷变频频率综合器。采用该方案实现的宽带微波频率合成器,具有电路结构简洁、频率切换时间短、频率分辨率高、高杂波抑制度及小型化等优点。通过测试数据表明,该频率源频率达到切换时间<5 μs,相位噪声优于-100dBc/Hz@10kHz,杂波抑制优于-63 dBc的优良指标。

捷变频;宽带;频率合成器

微波频率合成器正朝着捷变频、小型化、多功能的趋势发展。频率快捷变是微波频率合成器的一项核心技术指标[1-3],同时也是设计难点。宽带捷变频频率合成器通常采用直接频率合成技术[4](DS)、直接数字频率合成[5-9](DDS)或者两者相结合的方式实现[10-11]。然而,采用些频率合成方式实现的宽带捷变频频率合成器结构复杂,难以实现低成本及小型化。

本文采用将高参考时钟DDS与高鉴相频率、宽环路带宽锁相环电路相结合的方式。实现了频率范围覆盖8~12 GHz的宽带捷变频频率合成器。该方案充分发挥了DDS输出频率切换时间快和锁相环电路结构简单的优势[12-13],较好的实现了频率合成器的输出带宽、频率切换时间、相位噪声、杂散抑制等技术指标与结构复杂程度和实现成本间的平衡。该频率合成方法对低成本、小型化宽带捷变频频率综合器的设计具有较好的参考价值。

1 频率合成器实现方案

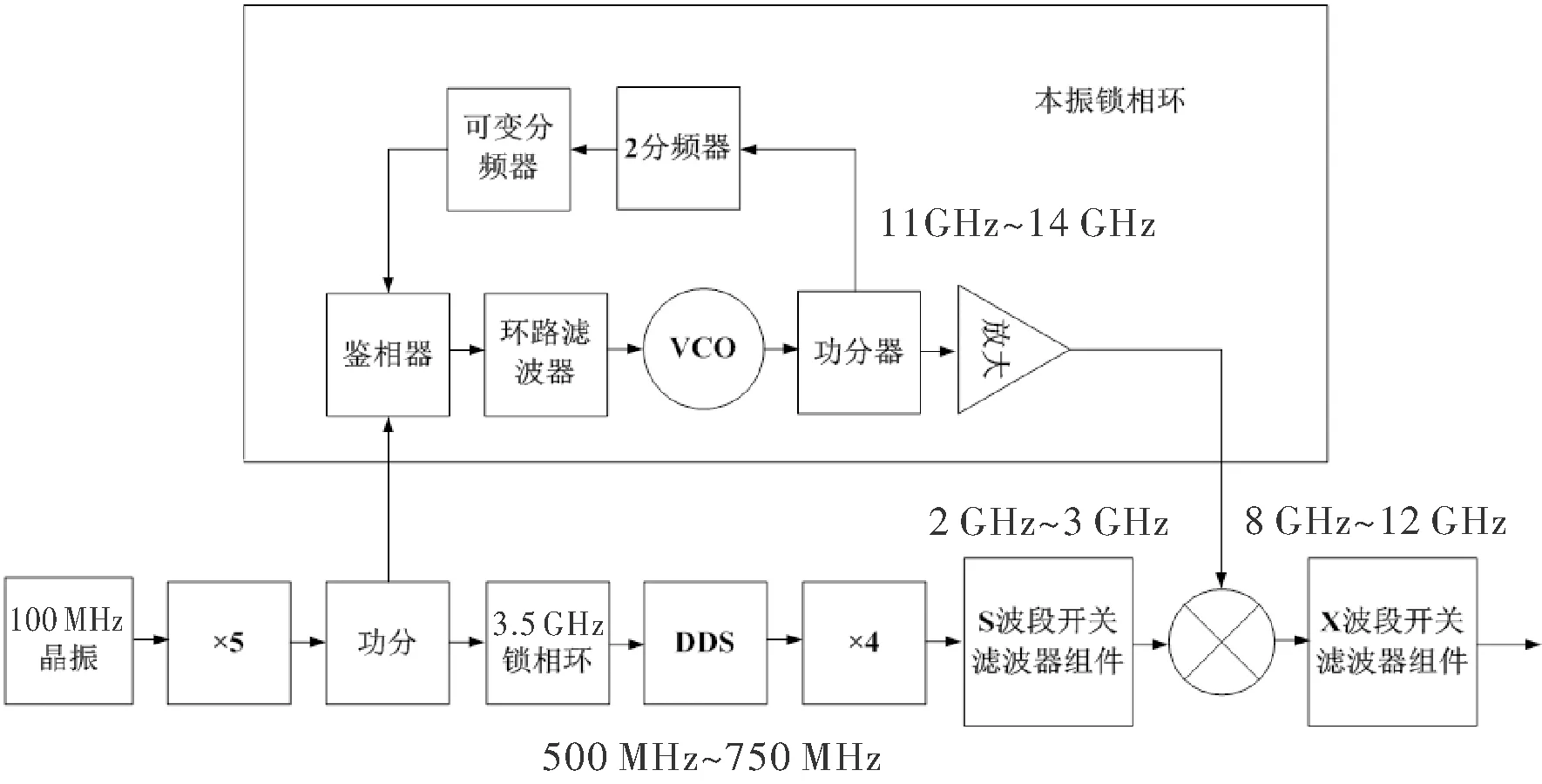

本文采用的宽带捷变频频率合成器原理框图如图1所示。

图1 频率合成方案原理框图

从图1可知,DDS倍频后输出2~3 GHz的基带信号,将其作为中频信号与锁相环电路产生的11~14 GHz的本振信号上变频,通过滤波组件取其下边带,即可实现频率覆盖8~12 GHz的信号输出。

图1中,DDS的参考时钟高达3.5 GHz。根据DDS的工作原理,将DDS的参考时钟提高,可以在扩展其输出带宽的同时提高信号的杂散抑制水平。因此,将高参考时钟的 DDS输出信号倍频后,可获得低杂散的宽带信号。

为达到扩频以及频段提升目的,将DDS倍频后的输出信号与锁相环电路输出的可变本振信号进行上变频。然而,由于锁相环电路的闭环反馈特性,存在频率切换时间长的缺陷。为实现本振信号的快捷变,将锁相环电路的参考信号提高至500 MHz。通过提高锁相环电路的参考频率,可降低环路分频比从而提升相位噪声指标,最重要的是可将宽路滤波器的环路带宽增加,使本振信号的频率切换时间大幅缩短,从而实现全频段频率捷变。

2 关键技术指标分析

2.1 频率切换时间分析

在图1的频率合成原理框图中,产生本振的锁相环电路频率间隔为1 GHz。当本振频率保持时,频率合成器在1 GHz带宽内的频率间隙由DDS输出信号填补,其频率切换时间受DDS频率控制字传送时间t1,DDS接收频率控制指令到输出信号的时间t2,S波段开关滤波组件中开关响应时间t4的影响[14]。

在本方案中,DDS采用并行控制方式,控制单元时钟为100 MHz,因此,DDS频率控制字发送时间t1=10 ns。

根据所用DDS的技术资料可知,DDS接收到频率控制指令到DDS输出信号的时间约为324个时钟周期,因DDS的参考时钟为3.5 GHz,可得计算得到t2=92.5 ns。

S波段开关滤波组件以及X波段开关滤波组件采用微波开关为固体电子开关实现通道切换,通道切换典型时间t3=60 ns。

由于微波信号传输路径上延时可以忽略不计,因此可以得到在本振频率保持不变时,输出信号的频率切换时间

thold≈max(t1+t2,t3)

(1)

由式(1)可得,thold=102.5 ns。

当频率合成器输出频率的本振信号切换时,输出信号的频率切换时间由锁相环电路的频率切换时间决定。频率合成器的环路带宽设计为2 MHz,阶数为两阶。锁相环频率切换时间可由式(2)计算得出

(2)

式中,thop表示频率切换时间;ωc表示环路滤波器的带宽;Δf表示频率间隔;α表示频率相对误差;f1表示初始频点。

由于输出信号的起始频率f1=11 GHz;最大频率间隔为Δf=3 GHz;环路带宽约为ωc=2 MHz;设定α=1×10-6,将各参数代入式(2)可得thop≈2 μs。

通过以上分析可知,方案中的频率合成器在本振频率保持不变时,频率切换时间约为102.5 ns,当本振信号改变时,频率切换时间理论值约为 2 μs。

2.2 杂散抑制分析

本方案中,信号输出杂散主要有3个来源:一是DDS自身输出杂散;二是DDS输出信号倍频后产生的谐波;三是混频过程中落入滤波器通带内的交调杂散。

首先,DDS自身杂散主要受相位截断误差,幅度截断误差,数模转换器(DAC)非线性等因数的影响[15]。其中占主导因数的是DAC的非线性效应。由于DAC非线性的存在,使得输出信号与参考信号产生互调频率分量,形成DDS自身的主要杂散。这些杂散分量可以表示为

f=mfs±nfout

式中,f表示杂散频率分量;fs表示DDS参考时钟频率;fout表示输出信号频率;m,n表示阶数。阶数m和n越大,杂散分量则越小。由于DDS倍频前输出信号频率范围为500~750 MHz,故m=1,当n分别为5,6,7时杂散分量将落入滤波器带内无法滤除。根据技术手册提供的数据预测,该杂散优于-75 dBc。

DDS输出信号倍频后,杂散恶化可由式(3)计算得到

Pspur2=Pspur1+20logN

(3)

式中,Pspur2表示倍频后的杂散抑制度;Pspur1表示倍频前的杂散抑制度;N表示倍频次数。

DDS倍频次数为4,因此,DDS输出4倍频后得到的2~3 GHz信号带内杂散抑制度优于-63 dBc。

DDS倍频后谐波行成的杂散主要由S波段开关滤波器组件进行抑制。经4倍频电路后,倍频器输出对各谐波分量的抑制度优于-15 dBc。而方案中采用的带通滤波器在各谐波分量处的抑制优于-50 dBc。因此,倍频后的信号经带通滤波器,可将DDS输出谐波形成的杂散抑制控制在-65 dBc。

最终输出的8~12 GHz信号为锁相环电路输出的本振信号L0与DDS倍频后形成的中频 上混频的下边带信号,其余交调分量将形成杂散信号。由于本振信号频率范围为11~14 GHz,而中频范围为2~3 GHz。由该频率关系可知,8~12 GHz信号的带内交调杂散主要由中频信号的3次和4次谐波分量构成,其余低阶交调分量则远离滤波器组件的通带。通过保证本振信号功率,使混频器工作于线性区域,同时降低中频信号功率,可将落入带内杂散分量降至较低水平,根据混频器的技术参数,带内杂散可控制在-65 dBc内。带外杂散主要为其余交调分量以及本振信号的泄露,通过带外抑制为-50 dBc的开关滤波组件,容易将带外杂散控制在-65 dBc内。

综上分析,输出信号的杂散抑制主要来源于DDS自身,约为-63 dBc。

3 测试数据

3.1 频率切换时间测试

根据图1的频率合成方案完成了频率合成器的研制。通过上述分析可知,由最低频点8 GHz切换至最高频点12 GHz所需的时间为频率切换最长时间。

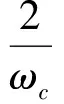

由于设备测试能力限制,无法在微波频段直接测试频率切换时间,从而采用如图2所示的测试方法进行频率切换时间测试。其主要思路是将微波信号通过混频和分频的方式降低至示波器可测试的范围,在时域进行频率切换时间的测试,图3为测试结果。

图2 本振切换时间测试方法

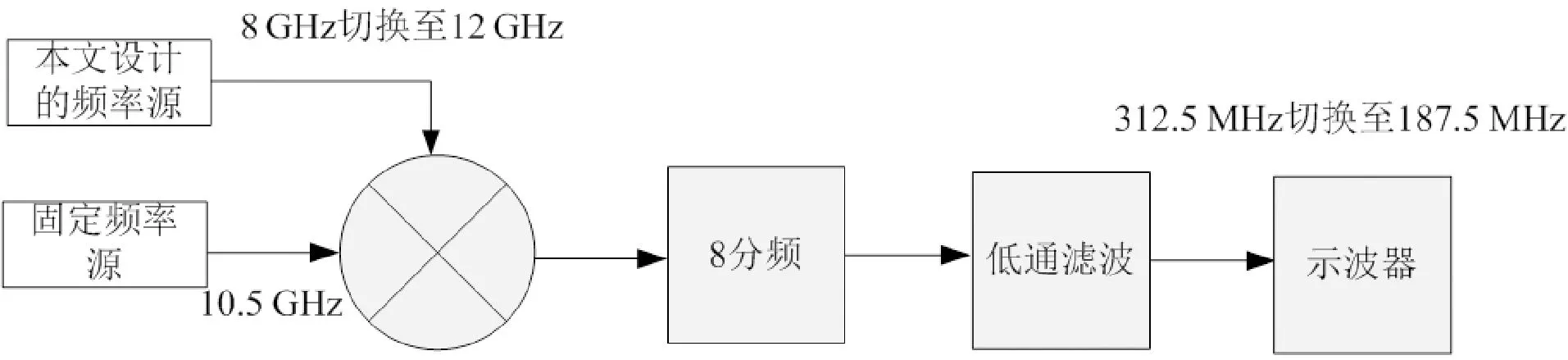

图3 本振切换时间测试结果

从图3的测试结果可知,该宽带频率合成器最长频率切换时间约为4.5 μs,与理论值存在一定的差距,这与未考虑环路滤波器运算放大器响应速度以及测试电路的延时等因素有关,但就锁相环频率切换时间而言,已达到较高水平。

3.2 相位噪声以及杂散抑制测试

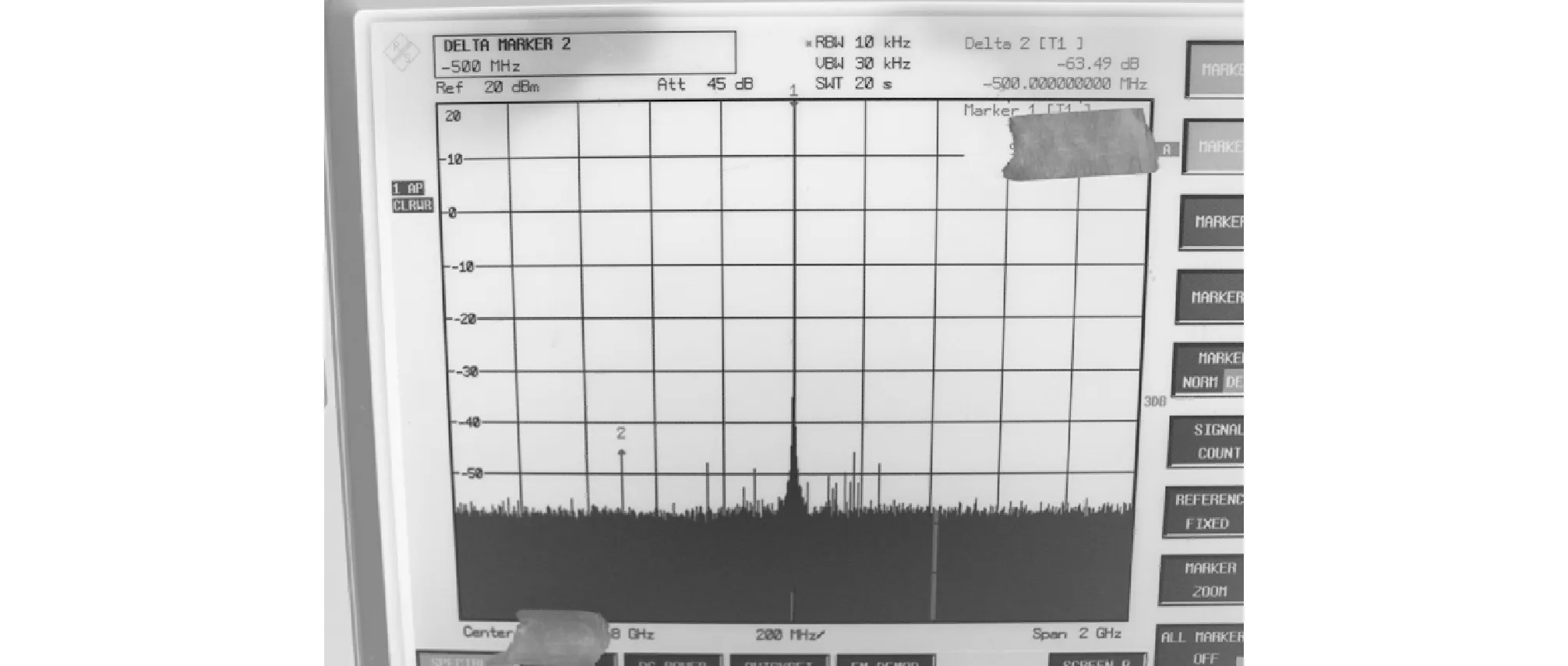

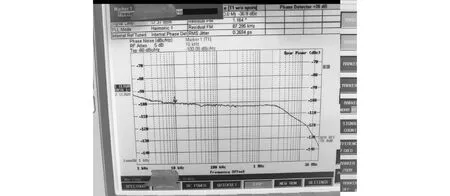

采用FSUP26信号分析仪对频率合成器的输出信号相位噪声以及杂散抑制度进行测试。其中杂散抑制的典型值如图4的测试曲线所示,相位噪声如图5的测试曲线所示。由测试曲线可知,宽带微波频率合成器相位噪声测试值约为-100 dBc/Hz@10 kHz,杂散抑制度测试值约为-63.4 dBc,达到预期设计目的。

图4 输出信号杂散抑制

图5 输出信号相位噪声

4 结束语

本文采用高参考时钟DDS与高鉴相频率、宽环路带宽锁相环电路相结合的方式,实现了频率范围覆盖8~12 GHz的宽带捷变频频率综合器,以简单的电路结构较好实现了宽带捷变频频率综合器各项核心技术指标与复杂程度间的平衡。

通过对设计方案的工程实现,并对相关参数进行了测试。该频率合成器频率切换时间小于5 μs,杂散抑制优于-63 dBc,相位噪声优于-100 dBc/Hz@10 kHz。达到了预期的设计目的,证明了该频率合成设计方案的可行性。

[1] 郝凤玉,宁娜.Ku 波段小型化低相噪捷变频频率综合器研制[J].四川兵工学报,2014,35(9):99-101.

[2] 厉家骏,张福洪,陆家明.一种捷变频锁相环设计研究[J].通信技术,2015,48(10):1192-1195.

[3] 庞遵林,郭锐.一种用于高速锁相环的整数分频器设计[J].电子科技,2015,28(6):104-107.

[4] 赖寒昱,李光灿,杜勇.基于ADS仿真的梳状谱发生器的设计与实现[J].电子科技,2014,27(7):84-86.

[5] 张雷雨田.DDS 带内杂散对比分析及优化方法[J].电子科技,2016,29(6):79-81.

[6] 张铮,胡婷.基于AD9854的多功能高精度DDS 信号源设计[J].电子科技,2017,30(3):182-184.

[7] 武志敏.DDS 激励PLL 方式的频率合成器设计[J].科技与创新,2016(11):120-121.

[8] 刘兴,杜勇.捷变频频率合成器的研究和设计[J].电子世界,2015(24):74-76.

[9] 李倩.AD9910 在雷达信号源中的应用[J].四川兵工学报,2013(7):19-21.

[10] 刘林,田进军,刘朝辉.基于DDS和直接频率合成技术的超宽带捷变频源的设计与实现[J].兵工学报,2010,31(12):1648-1652.

[11] 陈研,陈立群.基于DDS的宽带捷变频综的设计及其应用[J].中国电子科学研究院学报,2010,5(4):423-429.

[12] 段金杰,蔡婷,窦彦军,等.PLL频率合成器设计与实现[J].电子世界,2016(5):71-72.

[13] 赵秋明,肖龙,许丰灵,等.基于锁相环技术的UHF频段宽带频率源设计[J].电子器件,2016,39(4):898-902.

[14] 白居宪.低噪声频率合成[M].西安:西安交通大学出版社,1994.

[15] 白居宪.直接数字频率合成[M].西安:西安交通大学出版社,2007.

Design on Frequency-Agile Wide Band Microwave Synthesizer

DU Yong,LI Guangcan,LIAO Haiqian

(No.5 Research Room,Guizhou Aerospace Institute of Measuring and Testing Technology,Guiyang 55009,China )

Contrapose the disadvantages of complex structure and high cost in most of wideband, frequency agile synthesizer, a frequency agile synthesizer with 8~12 GHz bandwidth is proposed in the paper. The synthesizer is realized by mixing the output of a multiplier and the output of a PLL with wide loop bandwidth and high phase-detect frequency, and then filtering by a filter module. The input of the multiplier is the output of the DDS with high reference. The synthesizer has the advantages of simple structure, short frequency switching time, high frequency resolution, high suppression and miniaturization. It is shown in the test results that the frequency switching time is less than 5μs, Phnase Nosise is lower than -100 dBc/Hz@10 kHz,and the suppression is lower than -63 dBc.

frequency-agile;wide band; frequency synthesizer

2016- 04- 24

贵州省科学技术基金(黔科合J字[2014]2076)

杜勇(1986-),男,硕士,工程师。研究方向:微波频率合成技术。李光灿(1966-),男,硕士,研究员。研究方向:测试与测控技术。

10.16180/j.cnki.issn1007-7820.2017.07.037

TN74

A

1007-7820(2017)07-133-04