基于PCIe总线的多处理器数据交换技术

毕 城,元永红

(1.西安邮电大学 自动化学院,陕西 西安 710121;2.西安现代控制技术研究所,陕西 西安 710065)

基于PCIe总线的多处理器数据交换技术

毕 城1,元永红2

(1.西安邮电大学 自动化学院,陕西 西安 710121;2.西安现代控制技术研究所,陕西 西安 710065)

针对目前系统板级高速数据交换存在的数据稳定性问题,提出了一种基于PCIe总线的板级多处理器高速数据交换技术的设计方案,设计了一种以IDT公司的89HPES24NT24G2芯片为核心的PCIe总线交换器,MPC8377为处理器的多板互连系统。系统采用单片MPC8377作为PCIe总线主控制器,实现了统外部数据与内部数据的控制交换;采用10片MPC8377作为PCIe总线从控制器,实现内部数据高速分发。实际测试表明,系统可以稳定可靠实现数据传输。

系统集成;多处理器;高速数据交换;PCIe总线

现代处理器已配置了多种高速总线接口,其中PCIe总线是目前传输高速数据的主流总线,其是Intel于1997年提出的第3代I/O互连标准,是一种全新的串行总线技术。PCIe 总线具有以下特点:在数据传输模式上PCIe总线采用双通道串行传输模式,一条PCIe通道由2对差分线对组成,一对负责发送、一对负责接收;PCIe总线采用点对点技术,能够为系统内的所有设备分配独立的通道资源,充分保障设备的带宽,提高数据传输率,同时可以实现多个设备并行工作;具有很好的灵活性,一个PCIe物理连接可以根据实际需要配置成×1、×2、×4、×8等并行的数据通道,以满足不同设备之间通信带宽的要求。随着数量不断增长的PCIe处理单元和外设芯片,PCIe交换器提供协议转换能力,为多处理器系统的互连提供了便捷的解决方案。因此,本文以IDT公司的89HPES24NT24G2芯片作为PCIe总线交换器,以飞思卡尔公司的MPC8377芯片作为处理器,设计实现一种基于PCIe总线的多处理器数据交换传输系统。

1 硬件架构

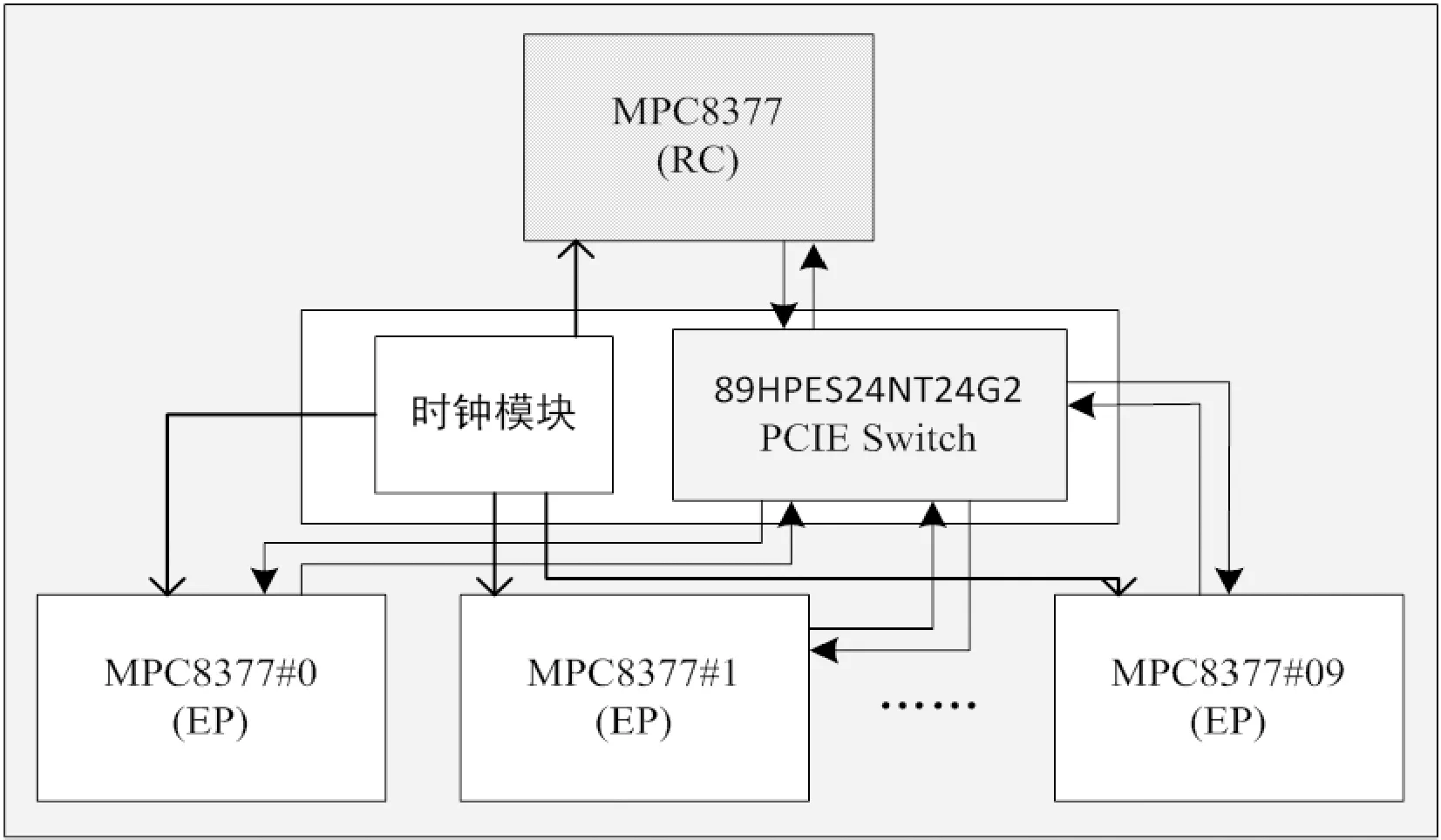

本文采用单片MPC8377作为系统的主处理器,作为PCIe交换器的RC端(Root Complex),10片MPC8377作为从处理器[1],作为PCIe交换器的EP端(End Point)。多个处理器通过PCIe交换芯片完成数据高速交换,具体设计架构如图1所示。

图1 系统架构图

MPC8377是飞思卡尔公司推出的e300内核PowerPC架构处理器,最高工作频率可达800 MHz。该处理器具有成熟的高速外设接口,包括2个三速以太网接口、4个SATA控制器、以及一个PCI Express总线控制器等[2]。MPC8377的PCIe控制器实现了CSB总线和PCIe总线的连接,其中PCIe总线最多支持×2 lane的2.5 GHz串行通信。MPC8377可以被设置为根复合体(RC)模式或端点(EP)模式。RC设备可将CPU或存储子系统与I/O设备连接,而EP设备通常表示一个外设或I/O设备。89HPES24NT24G2交换芯片实现PCIe链路的扩展。该芯片是IDT公司推出的一款兼容PCI Express 2.1规范标准的PCIe switch桥芯片。支持24 lane、24端口的PCIe switch互联,每个lane的峰值带宽可支持到5 GT/s[6]。89HPES24NT24G2支持非透明桥连接方式。非透明桥用于连接两个不同的PCIe总线域的场合,可以实现RC与RC的连接。

系统设计过程中PCIE交换器[4-6]的设计是一部分重要的工作,而作为系统通信控制的处理器设计则是本文的重点。

2 Ie交换器设计

PCIe交换芯片89HPES24NT24G2的24个端口可以组合工作,形成×1、×2、×4或×8宽度的链路。在PCIe通信系统方案中,RC和EP的PCIe链路宽度均为×1,即每片MPC8377的PCIe接口只与交换芯片的一个端口相连,共占用11个端口[7]。选用89HPES24NT24G2的端口0作为上游端口,连接作为RC的MPC8377;端口6到端口15共10个端口作为下游端口,连接作为EP的MPC8377。每个PCIe ×1链路由两对差分信号线RX和TX连接。

89HPES24NT24G2的外围电路中,时钟电路、配置电路和加载电路是关键电路。时钟的质量对芯片的工作质量影响较大,交换芯片的时钟模式可以通过其外设的配置管脚配置,本文使用的时钟模式是全局时钟模式,选择100 MHz时钟。配置电路选用串行EEPROM,通过交换芯片的Master SMBus接口连接。89HPES24NT24G2上电后可以从EEPROM中读取配置信息并设置switch的工作模式。外部I2C主机可以通过Slave SMBus接口向89HPES24NT24G2发送命令,操作实现EEPROM进行擦写。

3 器软件设计

MPC8377的硬件设计可以参考飞思卡尔官方设计,本文主要对系统中分别处于EP端和RC端的处理器软件设计进行研究。

3.1 备的驱动程序设计

处理器采用Linux操作系统,Linux应用程序要访问外部设备,必须通过设备驱动程序以文件的形式访问。作为EP的PowerPC驱动程序在逻辑上分为两部分:PCIe设备初始化和字符型设备驱动[8]。PCIe设备初始化部分主要调用Linux内核中的PCIe设备操作API,设置PCIe设备的工作模式,映射内存空间,绑定中断处理函数。字符型设备驱动部分首先初始化字符型设备,并将设备加入设备列表,最后通过访问文件系统节点的方式访问字符设备。

3.2 RC端应用程序设计

RC端应用程序是基于运行在MPC8377上的嵌入式Linux操作系统,主要完成参数与缓冲区初始化,以及对数据文件和设备的操作。

EP和RC之间的PCIe交换器在软件层面是透明的,RC可直接对EP的BAR空间进行访问。10个EP设备对应的设备名是pciecardn(n=0~9)。RC与EP的数据传输没有采用DMA的方式[9-10],所有数据交换都在EP的BAR0空间中完成。应用程序首先打开EP设备文件。在向RC发送数据时,应对相应的设备文件进行写操作;从RC读取数据时,应对相应的设备文件进行读操作。

由于没有采用DMA的传输方式,程序不能通过DMA完成中断得知读写操作已经完成。为解决这一问题,在程序设计时,约定EP设备BAR0空间的第一个字节为读写状态标识。若读写状态标识为0x00,表示没有进行BAR0空间的任何读写操作[11-12],此时可以对BAR0空间发起读或写;若读写状态标识0xff,表示对BAR0空间的写操作完成,可以将BAR0空间中的数据读取,之后读取数据的一方需要将读写状态标识重置为0x00,表示一次读写操作已经完成,可以发起下一次读写操作;若读写状态标识0xaa,表示一个完整的文件已传输完成,不需要继续发起读写。

3.3 EP端应用程序设计

EP端应用程序的主要工作是PCIe通信以及数据文件的创建和读写。EP的PCIe BAR0 inbound窗口是映射在物理地址0x0C800000的,EP端应用程序要访问该窗口,需要调用Linux系统函数mmap(),将从0x0C800000开始的4 MB空间映射至虚拟内存空间,应用程序通过这段虚拟内存就可以访问BAR0空间了[13-15]。EP端的PCIe通信操作与RC端类似,只是在RC端程序中对设备文件的读写,在EP端程序中变成了对特定内存区域的读写。

4 系统测试

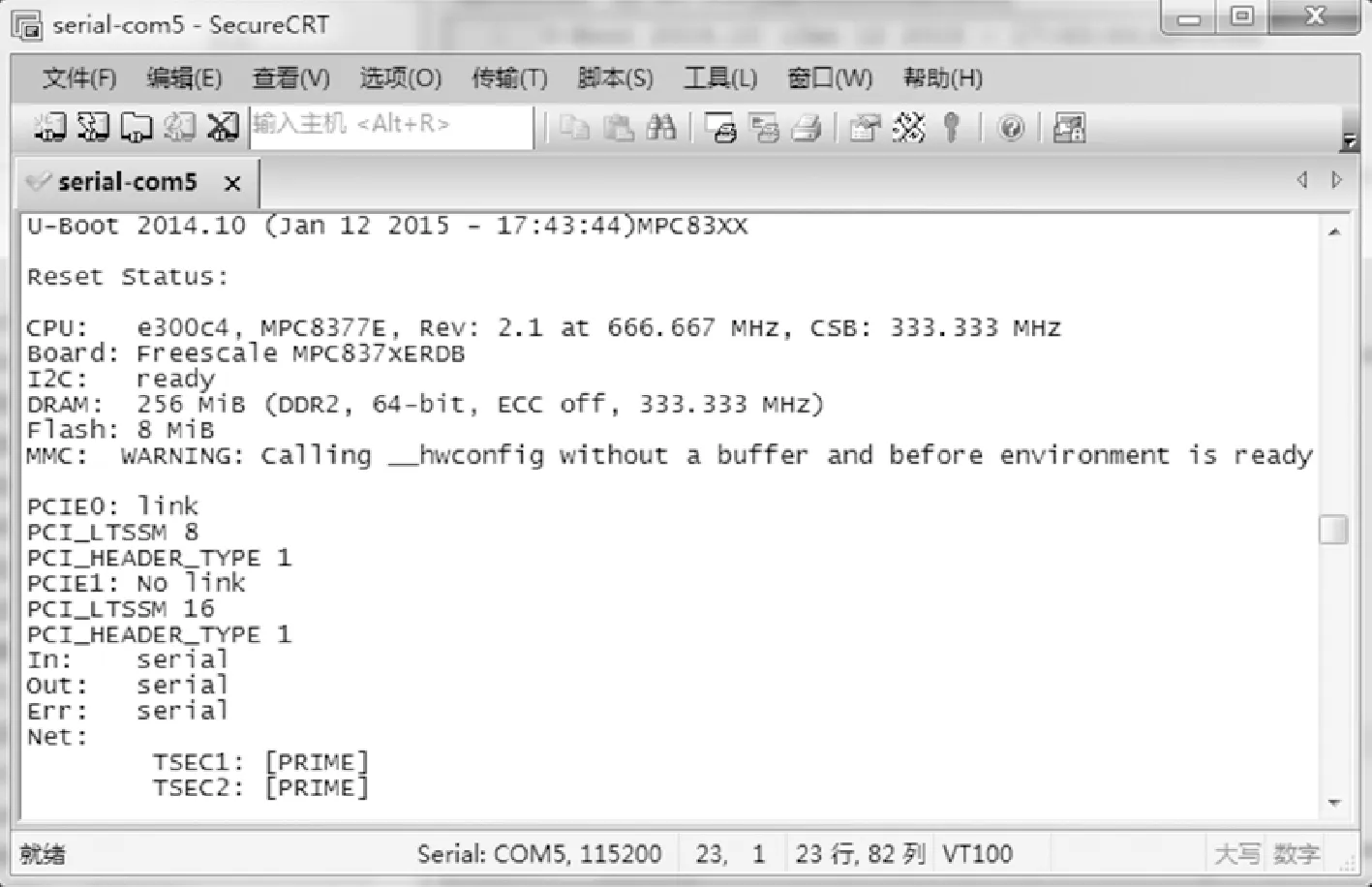

系统通过MPC8377的调试串口来显示测试信息。在RC处理器打印出的uboot启动信息如图2所示。可以看到,PCIe控制器2(PCIe1)的LTSSM状态机已经处于16(L0)状态,说明PCIe链路已经正常建立。配置头类型为type 1,设备类型为RC设备。

图2 RC端启动信息

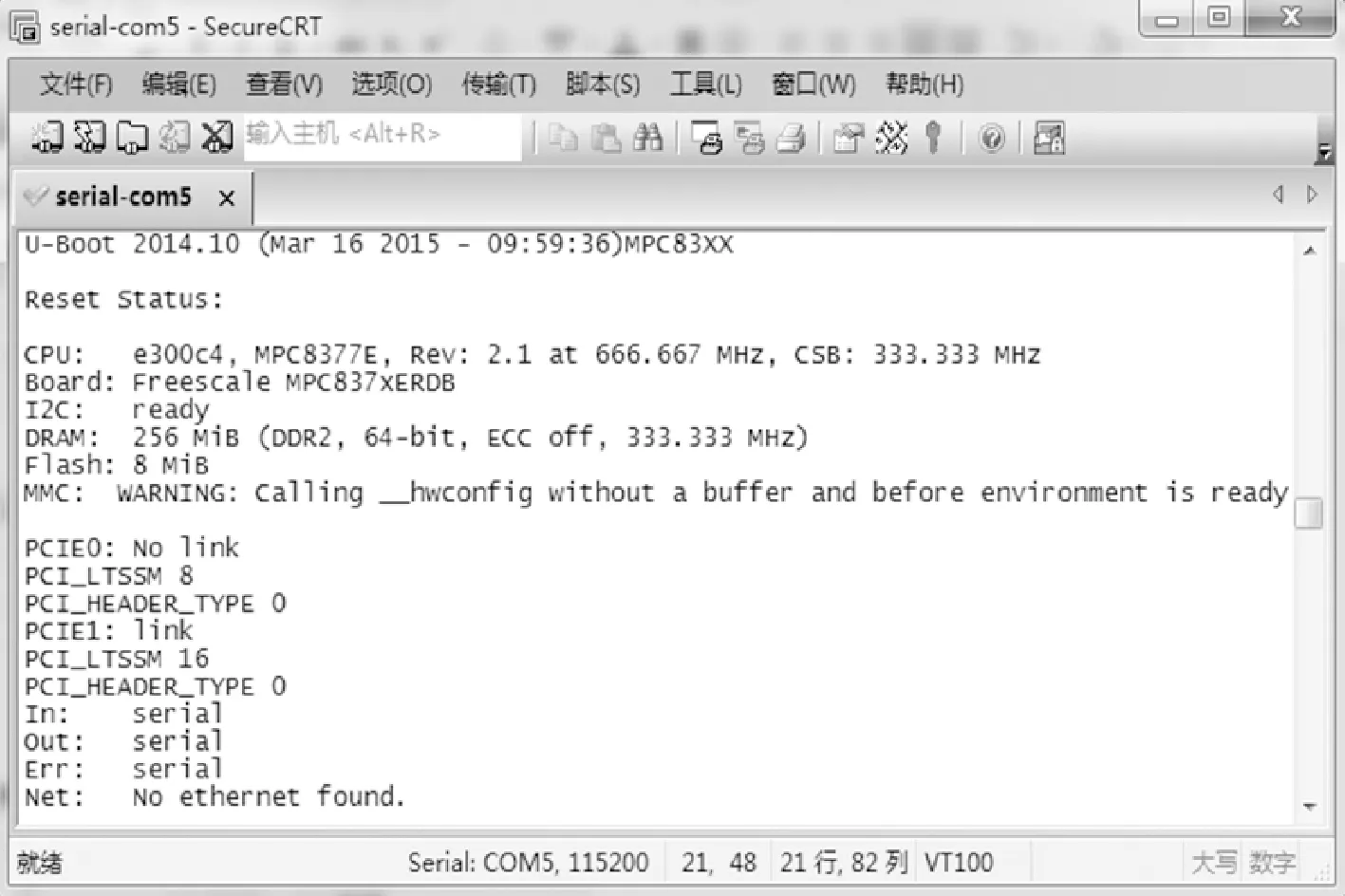

在EP处理器打印出的uboot启动信息如图3所示。可以看到,PCIe控制器2(PCIe1)的LTSSM状态机已经处于16(L0)状态,说明PCIe链路已经正常建立。配置头类型为type 0,设备类型为EP设备。

图3 EP端启动信息

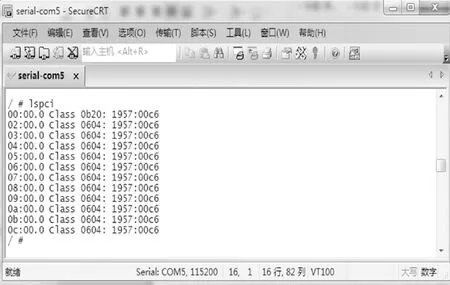

在RC端的Shell中输入lspci命令,可以看到已经与RC建立连接10个MPC8377 EP设备(列表中前两个设备为RC),设备信息如图4所示。

图4 PCIe设备列表

将编译好的驱动程序模块复制到RC端的文件系统中,用insmod命令加载。驱动程序识别到EP设备后,会自动为每个识别到的设备创建相应的设备文件节点。驱动加载完毕后,即可在文件系统的/dev目录下看到pciecard0~9设备文件节点。

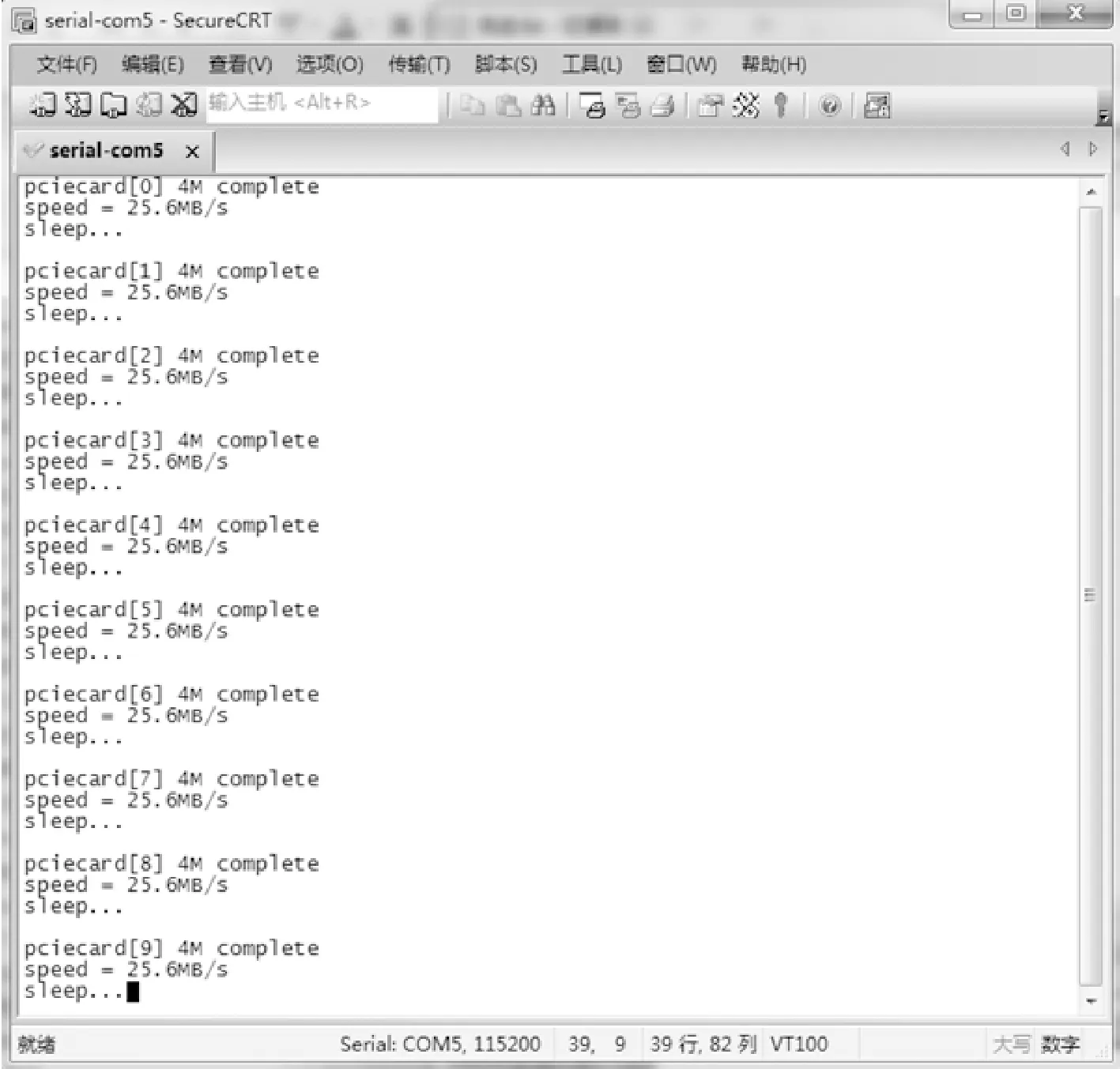

在RC处理器和EP处理器上运行各自的测试应用程序。RC端程序完成初始化工作后会进入主循环,将本地文件系统中的一段视频文件同时发送给10个EP设备。EP端测试程序则接收视频文件数据,并保存到硬盘。实际上,RC对每个EP的操作是分时轮流进行的。文件保存完毕后,可以将EP处理器挂载的硬盘取下,安装在计算机上,打开其中的视频文件检视。经实际测试,数据的平均传输速度约为25 MB/s,这主要是受到后端硬盘写入速度的限制和写入操作间隔的影响。程序运行时打印的调试信息如图5所示。

图5 PCIe通信应用程序运行情况

5 结束语

本文通过PCIe交换芯片实现多处理器高速数据互连系统,对89HPES24NT24G2设计及处理器软件设计进行了介绍。测试结果表明,基于PCIe交换的多处理器数据交换系统具有灵活的系统拓扑结构,降低了系统硬件复杂度,简化了软件开发过程。

[1] 王齐.PCI Express体系结构导读[M].北京:机械工业出版社,2010.

[2] Freescale.MPC8379E power QUICC II pro integrated host processor family reference manual[M].USA:Freescale,2009.

[3] IDT.89HPES12NT12G2 PCI express switch user manua[M].USA:IDT,2013.

[4] 李兵强,李国超,耿涛,等.基于89HPES12T3的多PCIE设备数据交换技术[J].信息与电脑:理论版, 2014(4):117-119.

[5] 张锐,曹彦荣.基于PICE交换的数据处理模块设计[J].电子技术设计与应用,2014(6):83-85.

[6] 张博,刘子逸.基于PES32NT24AG2芯片的PCIe交换器的实现[J].无线电工程,2014,44(7):73-76.

[7] 姜宁,陈建春,王沛,等.基于FPGA的PCIe接口实现[J].电子科技,2014,27(10):188-191.

[8] 梁国龙,何昕,魏仲慧,等.PCIE数据采集系统的驱动程序开发[J].计算机工程与应用,2009,45(31):63-65.

[9] 李晃,巩峰,陈彦化.基于PCIE驱动程序的数据传输卡DMA传输[J].电子科技,2014,27(1): 117-120.

[10] 刘波,库锡树,孙兆林.基于PCIE总线协议的数据采集设备驱动程序实现[J].工业控制计算机,2007,20(7): 28-29.

[11] 张森峰,甄国涌.基于PCI-Express的高速数据交换设计及应用[J].电子设计工程,2009,17(5):3-5.

[12] 马萍,唐卫华,李绪志.基于PCI Express总线高速数采卡的设计与实现[J].微计算机息,2008(25):116-118.

[13] 李涛涛.基于PCIE的高速存储系统设计[D].西安:西安电子科技大学,2014.

[14] 侯冰.FPGA实现的PCI-E高速数据采集系统[D].西安:西安电子科技大学,2012.

[15] 徐天,何道君,徐金甫.基于IP核的PIC Express接口[J].计算机工程,2009(12):239-241.

Multi-Processor Data Exchange Technology Based on PCIe Bus

BI Cheng1,YUAN Yonghong2

( 1.School of Automation, Xi’an University of Posts and Telecommunications, Xi’an 710121, China;2. Xi’an Modern Control Technology Research Institute, Xi’an 710065, China)

To improve the stability of high speed data exchange of the current system board, this paper presents a design of high-speed data bus and multi-processor board level PCIe switching technology, with the 89HPES24NT24G2 chip of IDT company as the core of the PCIe bus exchanger and MPC8377 as a processor for the multi board interconnect system. The system adopts the single chip MPC8377 as the main controller of PCIe bus for the control exchange between external data and internal data of the system, and 10 pieces of MPC8377 as the PCIe bus from the controller to realize the internal data high speed distribution. The actual test shows that the system can achieve stable and reliable data transmission.

system board; multi-processor; level high speed data exchange technology; PCIe bus

2016- 09- 06

毕城(1995-),男,本科。研究方向:智能科学技术。元永红(1967-),男,高级工程师。研究方向:微型计算机应用等。

10.16180/j.cnki.issn1007-7820.2017.07.032

TN919.3

A

1007-7820(2017)07-118-04

——35型全自动钠离子交换器运行效果评价