基于FPGA的可重配置视频缩放系统设计

罗 振,唐清善,陈 凯,黎 欢,单威武

(长沙理工大学 物理与电子科学学院,湖南 长沙 410004)

基于FPGA的可重配置视频缩放系统设计

罗 振,唐清善,陈 凯,黎 欢,单威武

(长沙理工大学 物理与电子科学学院,湖南 长沙 410004)

针对目前视频图像缩放领域对实时性以及可重配置功能的需求,提出并设计了一种基于FPGA的可重配置视频缩放系统。设计采用双线性插值算法,以及时钟动态重配置技术,能够满足1 080 p分辨率高清视频的实时缩放,并能通过串口实现时钟的动态配置,达到实时切换输出分辨率的目的。

双线性插值;高清视频;动态重配置;实时切换分辨率

目前视频缩放技术的研究方向主要包括图像缩放算法和图像缩放的硬件实现上[1]。在图像缩放算法方面主要是对双线性插值[2]算法与双立方插值[3]算法以及各自衍生算法的研究,虽然双立方插值算法实现效果好,但算法复杂度高,不易于硬件实现。在硬件实现上,虽然市场上有大量的数字视频后处理芯片,但应用在单纯进行图像缩放的场合,则显得浪费[4],而FPGA能够实现特定功能的定制,并具有较强的可编程能力与并行处理能力[5],所以FPGA常被用于这类系统的解决方案中[6]。

不同的应用场合以及对分辨率的不同需求导致了目前视频缩放系统必须具有多种分辨率的重配置功能,并且在特定的应用场合还必须具有很高的重配置实时性。但目前大多数视频缩放系统不能实现重配置功能。基于以上背景,设计一种基于FPGA的采用双线性插值算法,能实现任意比例缩放,并能动态重配置多种分辨率显示的实时视频缩放系统。

1 算法原理与实现

1.1 算法原理

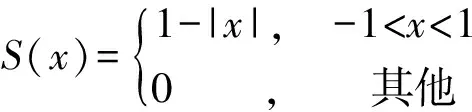

使用线性插值可以改善缩放图像视频质量[7],双线性插值算法就是指二阶拉格朗日插值算法,该算法考虑了图像的连续变化,也就是目标像素点与原像素点具有线性关系[8]。其插值基函数为

(1)

在图像插值算法中,x值表示原像素与目标像素之间的距离;S(x)为计算权值。

1.2 算法实现

双线性插值算法的实现是采用一个2×2的邻域,在垂直方向上进行两次插值,然后在水平方向上进行一次插值,从而得到所要的新插值点,即根据待采样点与相邻点的距离确定相应的权值计算出待采样点的灰度值[9],如图1所示。

图1 双线性插值算法

令相邻4个原像素点的距离为单位长度1,4个像素点的对应像素值分别为p1,p2,p3和p4,其坐标分别为p(x,y),p(x+1,y),p(x,y+1)和p(x+1,y+1),目标像素点对应于原坐标系坐标像素值为Q(x+dx,y+dy),其中,dx和dy分别为邻近左上方原像素点与目标像素点在原坐标系中水平与垂直方向上的增量。

双线性是指分垂直与水平方向分别做线性插值计算,令垂直方向插值计算临时像素点的值分别为Q1、Q2,则

Q1=(1-dy)P1+dyP3

(2)

Q2=(1-dy)P2+dyP4

(3)

利用垂直方向插值计算得到的两个临时像素点的值就可以通过水平方向插值计算得到最终目标像素点的值,则

Q(x+dx,y+dy)=(1-dx)Q1+dxQ2

(4)

2 系统及软件方案设计

2.1 系统方案设计

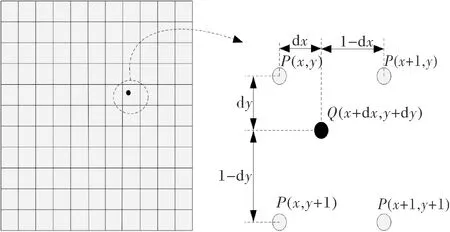

系统整体方案设计如图2所示,视频流从视频源发出后经过DVI接口,到FPGA内通过控制外部缓存SDRAM,先将视频数据缓存入SDRAM,然后根据需要从SDRAM中取出像素数据进行缩放处理,处理后的数据再通过DVI接口在LCD显示屏上显示。

图2 系统整体方案设计

FPGA内部使用及输出时钟由两个本地晶振提供,分别为125 MHz和74.25 MHz。由于该系统缩放的视频分辨率最低为800×600,最高为1 920×1 080,帧率为60 Hz,则输入视频像素时钟频率为40~148.5 MHz,只要数据读出速度高于写入速度,就不会使图像产生突变现象,从而达到实时处理的目的[10],所以将125 MHz本地时钟配置为150 MHz的系统时钟,用于提供给缩放系统和SDRAM使用;74.25 MHz时钟用于配置像素输出时钟。该设计的可重配置系统用USB转串口,通过USB实现串口收发功能,实现输出像素时钟和输出分辨率的重配置,达到对系统实时控制的要求。

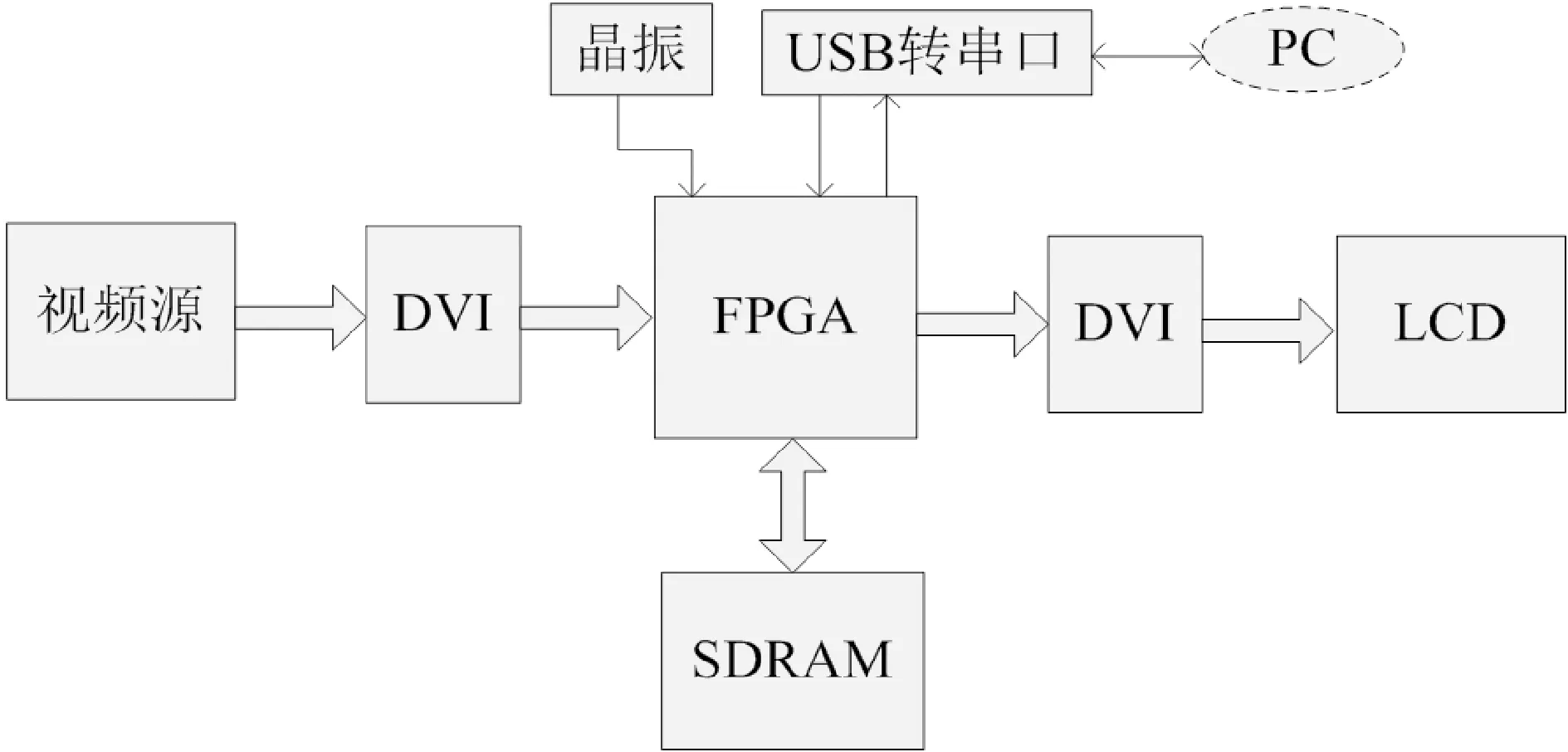

2.2 软件方案设计

软件方案设计就是指FPGA内部工作方案的设计,软件方案设计如图3所示。一般情况下,图像缩放系统的输入输出视频图像的分辨率不同,若要保证帧率相同,则输入输出时钟频率是不同的,则至少需要2个时钟域[11]。而该软件方案设计分为3个时钟域,分别为输入时钟域、内部时钟域、输出时钟域。其中输入时钟域时钟由输入视频源提供,时钟范围为40~148.5 MHz;内部时钟是由外部125 MHz晶振所产生的本地时钟通过PLL_BASE配置产生的150 MHz时钟;输出时钟是由外部74.25 MHz晶振所产生的本地时钟通过PLL_ADV配置产生的40~148.5 MHz时钟。

为实现不同时钟域之间的工作协同,需要进行跨时钟域处理,跨时钟域处理是通过两个异步FIFO实现的,如图3所示,利用FIFO0实现输入时钟域与内部时钟域的跨时钟域处理,利用FIFO2实现内部时钟域与输出时钟域的跨时钟域处理。

图3 软件方案设计

FPGA系统工作流程:(1)RGB数据以DE信号为写FIFO0允许信号,以视频源时钟实时的将数据写入FIFO0中;(2)通过SDRAM控制器,FIFO0内数据>512个时为写请求信号,以FIFO1内数据少于512个时为读请求信号,实现SDRAM对FIFO0和FIFO1的读写控制;(3)FIFO1内的数据根据后端缩放需要乒乓写入行缓存BRAM0和BRAM1;(4)缩放系统从BRAM0和BRAM1取出相邻的2×2像素数据先进行列缩放,再进行行缩放,若BRAM内数据需要更新,则通过控制从FIFO1读取更新BRAM内的像素数据;(5)经过缩放后的数据先缓存入FIFO2,然后在输出时序控制下,将数据从FPGA输出到下级芯片进行处理再显示。

3 系统关键部分设计及调试

FPGA关键部分设计包括缩放控制器的设计、SDRAM控制器设计,以及输出分辨率动态重配置设计。其中缩放控制器用于控制整个系统缩放工作,包括缩放计算以及缩放时序控制等功能;SDRAM控制器用于整个系统的帧缓存,为后续缩放工作提供像素数据;输出分辨率动态重配置设计用于产生输出时钟频率,配置相应的输出分辨率。

3.1 缩放控制器设计

缩放控制器包括两个状态机控制部分,分别为写缓存控制状态机,缩放控制状态机,其中写缓存状态机用于从FIFO1中写入像素数据到BRAM0和BRAM1中,缩放控制状态机用于整个缩放过程的控制。缩放控制器部分工作在150 MHz时钟频率下。

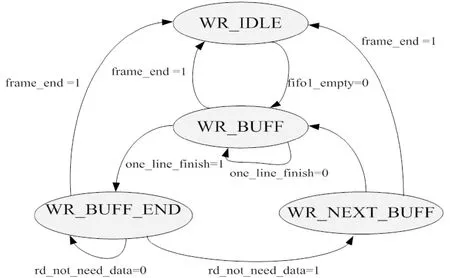

图4 写缓存控制状态机

当帧结束信号frame_end=1时,写缓存状态机wr_state处于空闲状态WR_IDLE,当fifo1的空标志信号fifo1_empty=0,即fifo1不空时,wr_state进入写缓存状态WR_BUFF,若写完一行数据,则one_line_finish=1,wr_state进入写缓存结束状态WR_BUFF_END,反之则仍然处于WR_BUFF状态,在WR_BUFF_END状态时,若行缓存内的数据已被后续缩放计算部分利用完毕,不需再重复利用时rd_not_need_data=1,进入写下一行缓存状态WR_NEXT_BUFF,然后直接进入WR_BUFF状态。

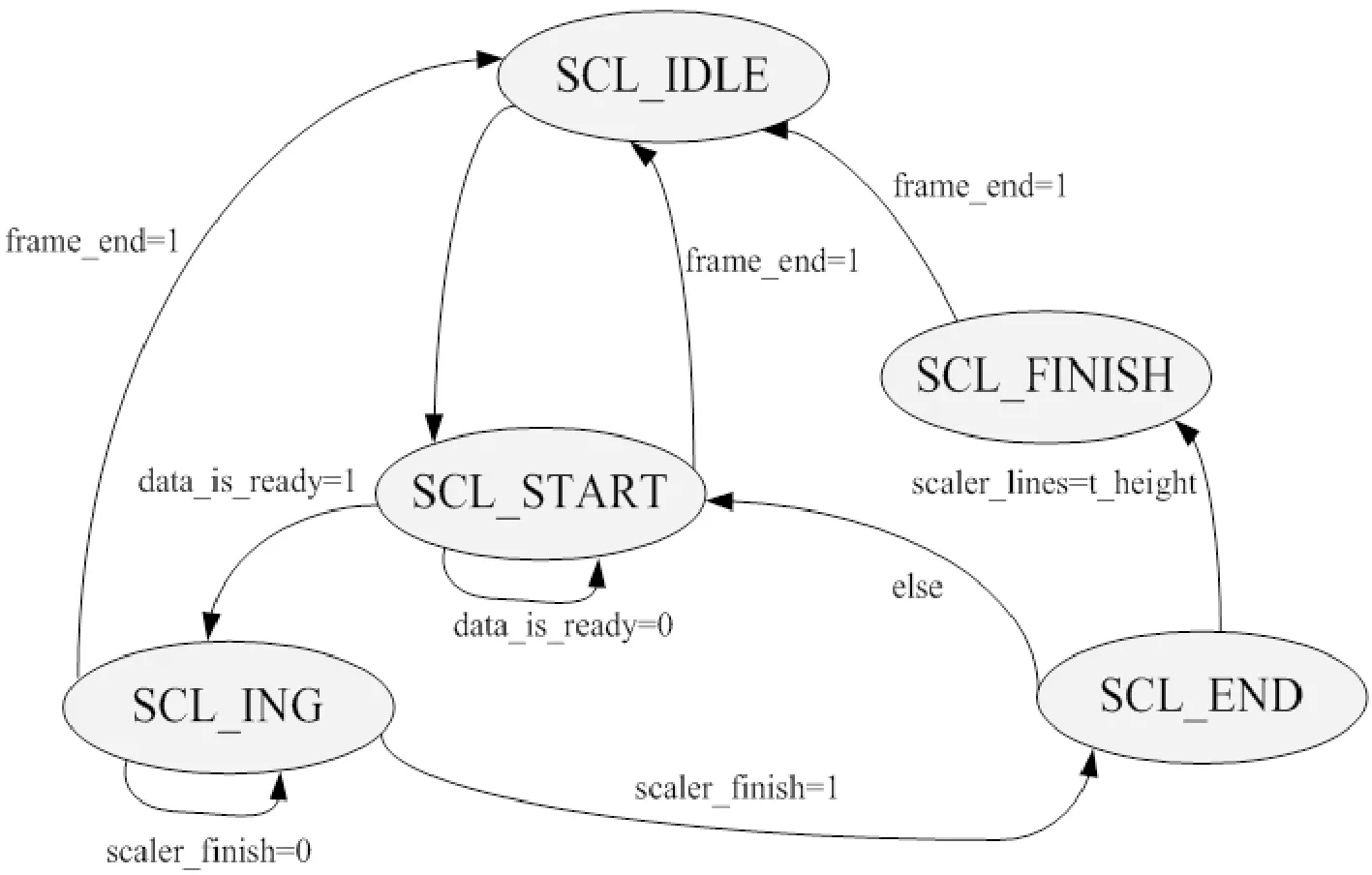

图5 缩放控制状态机

当帧结束信号frame_end=1时,缩放控制状态机scaler_state处于空闲状态SCL_IDLE,若frame_end不等于1,则进入缩放准备状态SCL_START。若参加缩放的两行数据已准备好,则data_is_ready=1,scaler_state进入缩放状态SCL_ING,此时进行缩放计算。若缩放得到一行所需数据,即scaler_finish=1,进入缩放结束状态SCL_END。若缩放得到的行数等于目标视频的行数,即scaler_lines=t_height,则缩放完成,进入SCL_FINISH状态。若没有完成则进入缩放准备状态SCL_START,准备进行下一行的缩放。

3.2 SDRAM控制器设计

该系统使用SDRAM以帧为单位来缓存视频数据,通过FPGA设计具有高可靠性的SDRAM控制方案[12]。设计采用三星64 Mbit SDRAM存储器,SDRAM工作在150 时钟下。该SDRAM数据位宽为32 bit,而RGB数据有24 bit,普遍采用的一种方法是将24 bit的RGB数据转换成16 bit的YUV422[13]数据,然后将两个16 bit像素合并,进行SDRAM的读写,能充分利用32 bit的带宽。然而在验证该系统时,直接使用24 bit的RGB像素数据,此时是舍弃了SDRAM数据线的高8 bit。

SDRAM从FIFO0读取像素数据并将数据进行存储,然后根据需要读取出所存储的数据写入FIFO1。当FIFO0内的数据计数器rd_data_count的值>512时,发出写请求命令,当FIFO1内的数据计数器wr_data_count的值<512时,发出读请求命令,当写入和读取请求命令发生冲突时,写入命令具有被响应的高优先级,从而保证数据不会丢失。SDRAM突发方式采用页突发方式,因为所采用的SDRAM有8根列地址线,所以一次页突发能连续读写256个数据。

3.3 输出分辨率动态重配置设计

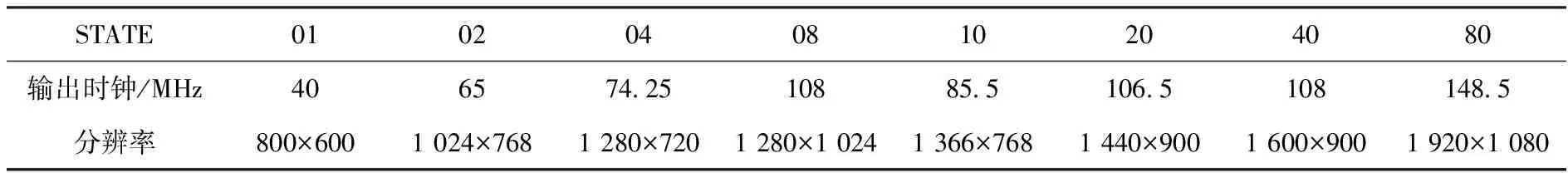

不同分辨率的图像,其像素时钟一般不同[14],输出分辨率动态重配置是基于时钟动态重配置[15]技术实现的,通过给动态配置单元发送特定的16进制状态码,从而输出约定的时钟频率以及配置相应的输出视频分辨率。输入时钟由外部74.25 MHz晶振产生,通过内部PLL_ADV的动态配置,预配置了8种不同频率的输出时钟,每一种时钟频率对应一种分辨率,各种分辨率视频的行宽场高各有不同。16进制状态码STATE与输出时钟及其对应分辨率的关系如表1所示,输出分辨率动态配置仿真如图6所示。

表1 状态码与输出时钟及分辨率的关系

4 实验结果

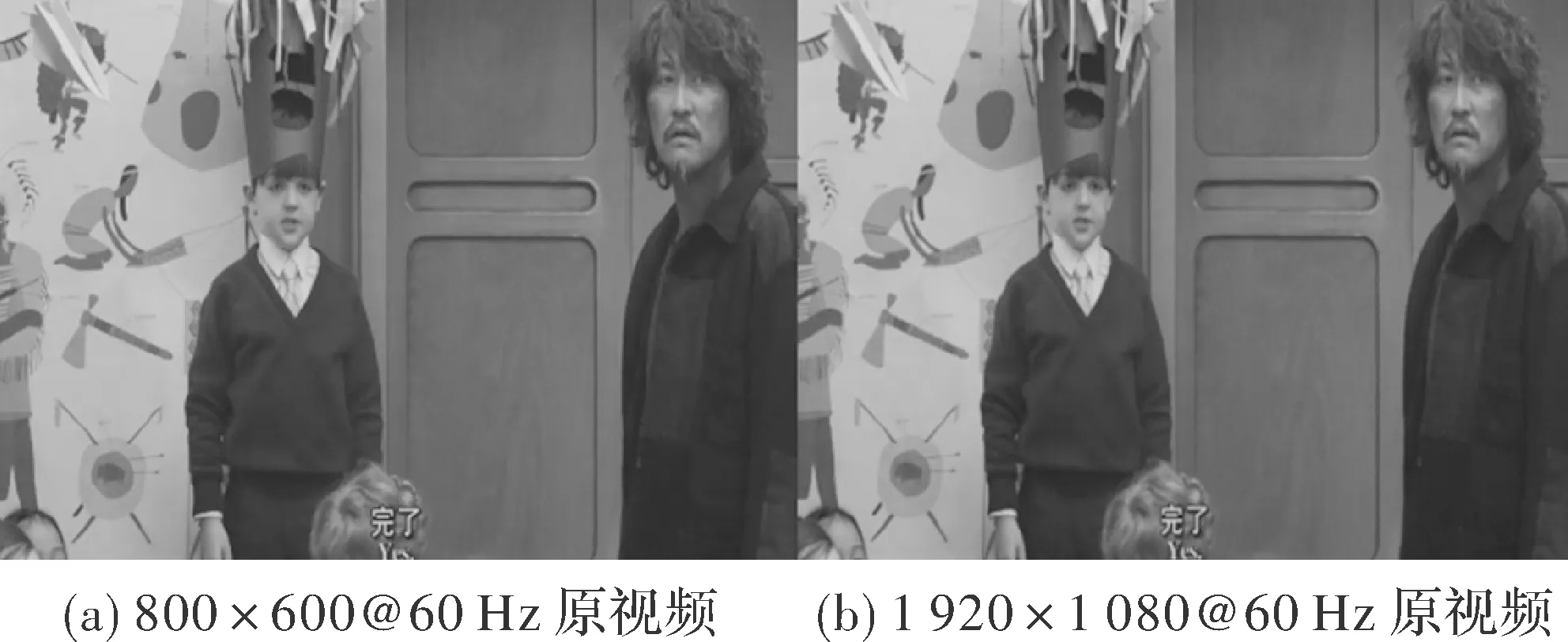

为验证该系统的实时放大功能,在原视频分辨率为800×600@60 Hz时通过串口助手,发送十六进制状态码80,将800×600@60 Hz分辨率视频放大到1 920×1 080@60 Hz,如图7所示;为验证该系统的实时缩小功能,在原视频分辨率为1 280×720@60 Hz时通过串口助手,发送状态码01,将1 280×720@60 Hz缩小至800×600@60 Hz,如图8所示。

图7 实时放大功能

图8 实时缩小功能

5 结束语

系统实现了视频缩放系统设计,实时视频SDRAM帧缓存设计以及时钟动态重配置设计。视频缩放系统能实现最高1 080 p高清视频的实时缩放,并能够达到60 Hz的帧率;SDRAM缓存能实现高清视频的帧缓存,在芯片可运行最高频率为166 MHz,设计工作频率150 MHz;时钟动态重配置设计,预设了8种不同的主流分辨率,并能够通过串口实时的切换输出频率,以达到匹配不同分辨率的作用,并具有良好的实时性,系统运行稳定。

[1] 莫迪涵.基于线性插值法图像缩放的设计与FPGA实现[J].西安邮电大学学报,2013(3):52-55.

[2] Parker J A,Kenyon R V,Troxel D E.Comparison of interpolation methods for image resampling[J].IEEE Transactions on Medical Imaging,1983,2(1):31-39.

[3] Hou H S, Andrews H C. Cubic alpines for image interpolation and digital filtering [J].IEEE Transactions on Signal Processing,1978,26(6):508-517.

[4] 孙红进. FPGA实现的视频图像缩放显示[J].液晶与显示,2010(1):130-133.

[5] 录文静.基于FPGA的视频缩放算法的研究与实现[D].武汉:武汉理工大学,2013.

[6] 刘强,晋兆虎.基于FPGA的任意比例图像缩放算法[J].数字技术与应用,2011(12):126-127.

[7] Keith Jack.视频技术手册[M].5版.杨征,译.北京:人民邮电出版社,2009.

[8] 苏延平.视频图像缩放的FPGA设计与实现[D].西安:西安电子科技大学,2014.

[9] 严利民,田锋,顾裕灿.图像缩放算法的研究及FPGA实现[J].仪表技术,2012(7):1-4.

[10] 赵贝.基于FPGA的视频图像处理算法的研究与实现[J].电子科技,2014,27(4):143-145,150.

[11] 王翔.数字图像缩放及图像质量评价关键技术研究[D].杭州:浙江大学,2012.

[12] 朱文斌.基于FPGA的高可靠性SDRAM控制器设计与实现[J].电讯技术,2011,51(10):113-116.

[13] 苏磊,张登福,刘涛.基于FPGA的RGB到YUV422的数字视频转换[J].电视技术,2009(S2):105-106,115.

[14] 曾鹏飞,唐清善.基于FPGA图像传输终端像素时钟恢复设计[J].电子科技,2013,26(12):114-117.

[15] Karl Kurbjun C R. PLL dynamic reconfiguration[J].Encyclopedia of Parallel Computing,2010,81(5):101-107.

Design of Reconfigurable Video Scaling Systems Based on FPGA

LUO Zhen,TANG Qingshan,CHEN Kai,LI Huan,SHAN Weiwu

(School of Physics and Electronic Science, Changsha University of Science and Technology, Changsha 410004, China)

In view of the demand for real-time and reconfiguration function in current video image scaling, we propose and design a reconfiguration video scaling system based on FPGA. The bilinear interpolation algorithm and clock dynamic reconfiguration technology are employed to achieve the real-time scaling of 1 080p video and real-time switch of output resolution by serial clock dynamic configuration.

bilinear interpolation; HD video; dynamic reconfiguration; real-time resolution switching

2016- 07- 18

罗振(1990-),男,硕士研究生。研究方向:数字视频处理。唐清善(1977-),男,博士。研究方向:数字信号处理,无线通信。

10.16180/j.cnki.issn1007-7820.2017.07.023

TN919.8

A

1007-7820(2017)07-083-04