一种Sigma Delta调制的SATA3扩频时钟发生器

王 希,邵 刚,吕俊盛,田 泽

(西安航空计算技术研究所 集成电路与微系统设计航空科技重点实验室,陕西 西安 710076)

一种Sigma Delta调制的SATA3扩频时钟发生器

王 希,邵 刚,吕俊盛,田 泽

(西安航空计算技术研究所 集成电路与微系统设计航空科技重点实验室,陕西 西安 710076)

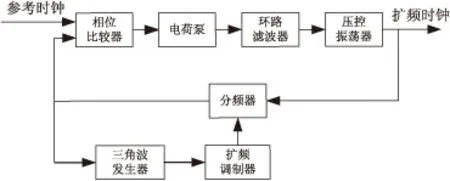

文中设计了一款符合SATA3协议、具有Sigma Delta调制特性的扩频时钟发生器。该电路基于小数分频锁相环,由相位比较器、电荷泵、环路滤波器、压控振荡器、分频器、三角波发生器和扩频调制器组成。通过三角波发生器产生固定频率的三角波,经过Sigma Delta调制器对三角波进行处理,实现对锁相环环路分频比的调制,进而使电路的环路特性满足SATA3协议的要求。该扩频时钟发生器的输入时钟为100 MHz,时钟输出以31.25 kHz的调制频率由6 GHz向下扩频5 000 ppm,得到的功率相比于未使用向下扩频时减小了21.58 dB。文中所设计的电路采用65 nm CMOS工艺,所用的电源电压为1.2 V,功耗大小约为43 mW。该结构受到工艺参数变化的影响较小,电路结构相对简单,性能稳定,便于集成。

SATA3;锁相环;扩频时钟;三角波调制

1 概 述

近年来,芯片的接口速度越来越高,往往达到5 Gbps以上,由此产生了更为严重的EMI问题,对电子产品性能造成了恶劣影响。在高速接口电路中,传统抑制电测干扰的办法是使用屏蔽线和同轴线,但这会大大增加产品成本。相比之下,扩频时钟技术易于实现,适合在芯片设计中使用,可显著降低系统设计开销[1]。

图1是时钟向下扩频的示意图。

以三角波调制为例,扩频调制后的时钟频率在fnormal与(1-δ)fnormal之间以fm为周期变化。其中,δ是扩频调制系数,fnormal是非扩频时的时钟频率,fm是调制频率。在SATA3协议中,fnormal为6GHz,δ不超过5 000ppm,采取三角波调制且调制频率fm为30~33kHz[2]。扩频后的时钟频谱在功率峰值上将比原来未扩频时有所下降,从而一定程度上抑制了电磁干扰。

2 系统设计

扩频时钟的产生,一般采取向锁相环中注入调制信号的方式来调制环路参数,达到扩频的目的。其主要的调制方式可根据对锁相环调制位置的不同而分为以下三种。

图1 时钟向下扩频的示意图

第一种方法是调制锁相环的输入参考时钟。这种方法会引入较大的数字噪声,恶化时钟信号的噪声和抖动,影响扩频的性能,不适合于片上实现。

第二种方法是调制压控振荡器的控制电压。这种方式能直接控制输出频率,但是受限于模拟调制方式,易受工艺偏差影响,调制精度不高。

文中采用第三种方法,在锁相环的反馈回路分频器处进行调制。相比于调制参考时钟、调制压控振荡器控制电压等方式,受工艺参数变化影响小,性能稳定,电路结构简单,便于集成,适合于SATA3等有时钟扩频要求的高速数据传输应用[3]。

所设计的扩频时钟产生电路结构如图2所示,由相位比较器、电荷泵、环路滤波器、压控振荡器、分频器、三角波发生器和扩频调制器组成[4]。

图2 系统结构图

根据SATA3协议要求,输出时钟的目标频率为6GHz,并需要以30~33kHz的频率为周期进行向下5 000ppm的扩频调制。三角波发生器产生周期为31.25kHz的三角波,对调制器的输出进行控制。调制器对分频器进行SigmaDelta调制,并控制分频比呈三角波形式变化,利用环路的跟踪特性使振荡器的输出时钟频率向下扩展,达到抑制电磁干扰的目的。

3 电路设计

3.1 电荷泵

电流转向电荷泵的电路结构如图3所示。

图3 电荷泵

该电路在输出点引入一个单位增益运放作为缓冲器,使电荷泵的输出端跟踪单位增益缓冲器的输出端电位。在开关管打开与关闭的过程中,上下电流源器件的漏端始终与电荷泵输出或单位增益缓冲器的输出相连,减小了开关管源极向衬底电容的充放电。而且因为电流源总是处于导通状态,虽然会增加一定的静态功耗,但电荷泵的开关速度得到了大幅提高。

电流源采用共源共栅结构,增大了其输出阻抗,提高充放电时电流的大小匹配,代价是缩小了输出电压的线性范围。开关管为对管形式,减小了电荷的沟道注入和时钟馈通效应的影响。该电路的最显著特点是电流失配小,可低至1%,工作速度快,适用于参考时钟频率较高的系统中[5-6]。

3.2 振荡器

振荡器采用电感电容结构的压控振荡器,见图4。

图4 压控振荡器

相比于环形振荡器,电感电容振荡器具有低功耗和低噪声的优点。

图中电流镜处的RC低通滤波能显著改善电路的低频噪声性能。振荡器顶部的电容和底部的电感则可以很好地抑制二次谐波[7]。

振荡器由片上稳压器供电,能充分隔离数字模块耦合到电源上的各种噪声[8],提高了电路的噪声性能。

谐振电路采用宽带调谐结构。谐振电容由固定电容阵列和变容管组成。该电路将输出频率范围分为若干个子带,由固定电容阵列控制。在各个子带内部,由振荡器的输入控制电压Vtune对可变电容进行连续调节。

振荡器之所以采用宽带结构,一方面是考虑到需要在一定范围内对工艺温度和寄生等因素造成的频率偏差进行及时修正,另一方面是为了进一步兼容其他协议的指标要求,以提高设计的可重用性[9-11]。

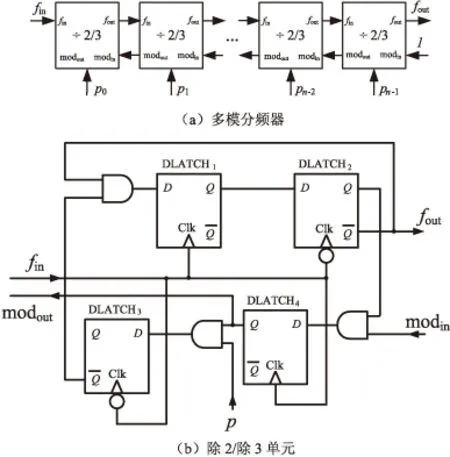

3.3 多模分频器

多模分频器的电路如图5(a)所示。它由若干除2/除3单元级联而成,每级相互独立。随着频率降低,后级除2/除3单元的功耗和晶体管尺寸可以相应减小。图5(b)为除2/除3单元的内部电路结构。当modin为0,电路为二分频;当modin为1,电路为三分频[12]。

图5 多模分频器和除2/除3单元

多模分频器电路的分频比N可表示为:

N=2n+2n-1pn-1+2n-2pn-2+…+2p1+p0

(1)

按照工作频率的大小,一般可将多模分频器分为前和后两部分。前端电路的工作频率高,将振荡器的高频信号分频到较低的频率,然后再由后半部分的可编程分频器进一步分频,把信号的频率降低到目标频率。

图5(b)中的DLATCH可以采用CML或TSPC两种结构。CML结构的工作频率高,可以产生全差分输出,能有效抑制共模干扰,缺点是存在直流功耗,频率越高功耗越大,且电路中晶体管堆叠,给低电压下的设计带来一定难度。而在TSPC结构中,电路的节点电容通过存储和泄放电荷来保存逻辑值。

随着特征尺寸的减小,尤其在90nm以后,TSPC电路的工作上限频率逐渐增大,受工艺偏差和温度变化的影响较小。相比之下,由于电源电压不断降低,CML结构的设计难度增大,其应用会进一步受限。在功耗方面,CML结构存在直流偏置,相比之下,TSPC属于动态逻辑,功耗较小[13-14]。

根据CML与TSPC结构的各自特点,文中的多模分频器在工作频率高的部分使用CML结构,低频率部分使用TSPC结构,达到了优化电路功耗的目的。

3.4 三角波发生器

三角波发生器是用来实现30~33 kHz,5 000 ppm的向下扩频功能的主要模块之一。通过控制分频器的分频比在小范围内呈周期性三角形波动,利用环路特性,进而使振荡器的频率随之改变[4]。

该部分由分频器、计数器、判决器组成。分频器将反馈时钟的频率降低到计数器的工作频率。计数器可以分别向上或向下计数,计数值作为调制控制输出。假设计数器向上计数,当计数值达到某一高点时,判决器翻转,使计数器开始向下计数,达到低点时则向上累加,周而复始,从而实现对分频比的三角波调制。

3.5 扩频调制器

扩频调制器的作用是控制分频器,使其产生与Fractional-N Sigma-Delta锁相环相类似的小数分频比。分频比的小数部分由三角波发生器确定,从而使振荡器的输出频率也呈三角波形式变化,而由此产生的量化噪声则被推到高频,最终被环路滤除。调制器采用MASH1-1-1结构[4]。

4 仿真结果

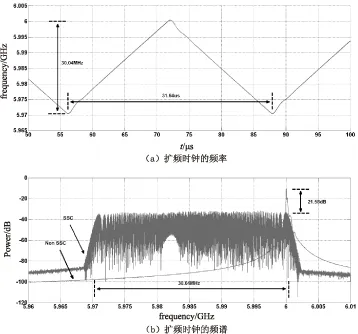

输入参考时钟频率为100 MHz,环路的分频比为60,考虑到兼顾其他协议的频率要求,Sigma-Delta调制器的位宽设计为16 bit。为生成31.25 kHz的三角波,将三角波发生器中分频器的分频比设为25,使得判决器工作在4 MHz频率下,计数下限为216·(1-60·0.005)=45 875,上限为65 535。

整个设计采用65 nm CMOS工艺,电源电压1.2 V,功耗43 mW。频谱仿真结果如图6所示。

从图中可见,当环路稳定后,扩频时钟输出时钟由6.001 GHz向下扩展到5.971 GHz,调制周期为31.6 kHz,相比未扩频的时钟,功率减小21.58 dB,实现了时钟扩展功能。

图6 频谱仿真结果

5 结束语

文中完成了一款支持SATA3的可扩频时钟发生器的设计。采用Sigma-Delta调制器对环路的分频器进行三角波调制,进而利用锁定状态下的环路特性,使得振荡器输出频率被固定频率三角波所调制,达到抑制系统时钟电磁干扰的目的。

[1] Uppala R.使用扩频时钟产生器降低峰值EMI辐射[J].今日电子,2014(2):37-38.

[2] Cheng K,Hung C,Chang C.A 0.77ps RMS jitter 6-GHz spread-spectrum clock generator using a compensated phase-rotating technique[J].IEEE Journal of Solid-State Circuits,2011,46(5):1198-1213.

[3] Pareschi F,Setti G,Rovatti R.A 3-GHz serial ATA spread-spectrum clock generator employing a chaotic PAM modulation[J].IEEE Transactions on Circuits and Systems I:Regular Papers,2010,57(10):2577-2587.

[4] Chen W T, Hsu J C,Lune H W,et al. A spread spectrum clock generator for SATA-II[C]//Proc of IEEE international symposium on circuits and systems.[s.l.]:IEEE,2005:2643-2646.

[5] Rhee W.Design of high-performance CMOS charge pumps in phase-locked loops[C]//Proc of IEEE international symposium on circuits and systems.Orlando,FL:IEEE,1999:545-548.

[6] Cheng S,Tong H,Silva-Martinez J,et al.Design and analysis of an ultrahigh-speed glitch-free fully differential charge pump with minimum output current variation and accurate matching[J].IEEE Transactions on Circuits and Systems II:Express Briefs,2006,53(9):843-847.

[7] Andreani P,Sjöland H.Tail current noise suppression in RF CMOS VCOs[J].IEEE Journal of Solid-State Circuits,2002,37(3):342-348.

[8] Wang X,Bakkaloglu B.Systematic design of supply regulated LC-tank voltage - controlled oscillators[J].IEEE Transactions on Circuits and Systems I:Regular Papers I,2008,55(7):1834-1844.

[9] Berny A D,Niknejad A M,Meyer R G.A 1.8-GHz LCVCO with 1.3GHz tuning range and digital amplitude calibration[J].IEEE Journal of Solid-State Circuits,2005,40(4):909-917.

[10] 洪 丽,王小松,李志强,等.适用于RoF的2.35GHz频率综合器[J].半导体技术,2013,38(7):492-496.

[11] 尹喜珍,马成炎,叶甜春,等.高灵敏度GNSS接收机频率合成器设计[J].浙江大学学报:工学版,2013,47(1):70-76.

[12] Vaucher C S,Ferencic I,Locher M,et al.A family of low-power truly modular programmable dividers in standard 0.35-μm CMOS technology[J].IEEE Journal of Solid-State Circuits,2000,20(7):1039-1045.

[13] Nonis R,Palumbo E,Palestri P,et al.A design methodology for MOS current-mode logic frequency dividers[J].IEEE Transactions on Circuits and Systems I:Regular Papers I,2007,54(2):245-254.

[14] Pihl J.Design automation with the TSPC circuit technique:a high-performance wave digital filter[J].IEEE Transactions on VLSI Systems,2000,8(4):456-460.

A Spread Spectrum Clock Generator for SATA3 Based on Sigma Delta

WANG Xi,SHAO Gang,LÜ Jun-sheng,TIAN Ze

(Key Laboratory for Aeronautics IC & Microsystem Design,China Aeronautics Computing Technique Research Institute,Xi’An 710076,China)

A spread spectrum clock generator for SATA3 with Sigma Delta modulation is proposed.The design is based on a fractional-N PLL,including phase detector,charge pump,loop filter,voltage-controlled oscillator,divider and triangular waveform modulator.The output waveform with constant frequency produced by the triangular waveform generator is transformed by a sigma delta modulator and controls the loop frequency divider to get compliance to SATA3.The circuit generates a 6 GHz clock with a 5000 ppm down spread spectrum modulated by a triangular waveform at 31.25 kHz with a 100 MHz reference clock.The power obtained is reduced 21.58 dB compared with not using spread spectrum.The circuit adopts 65 nm CMOS with a supply of 1.2 V,consuming 43 mW.The structure affected by process parameters change is small,and the circuit structure is relatively simple,with stable performance,easy to integration.

SATA3;PLL;spread spectrum clock;triangular waveform modulation

2015-06-16

2015-09-22

时间:2016-04-00

航空科学基金(2015ZC51036);中国航空工业集团创新基金(2010BD63111)

王 希(1988-),男,硕士,研究方向为高速数模混合集成电路设计;田 泽,博士,研究员,中航首席技术专家,研究方向为SoC设计、嵌入式系统设计、VLSI设计。

http://www.cnki.net/kcms/detail/61.1450.TP.20160322.1517.002.html

TP39

A

1673-629X(2016)04-0144-04

10.3969/j.issn.1673-629X.2016.04.032