低电压低功耗音频Σ-Δ ADC 调制器设计

张涛,何鹏,刘劲

(武汉科技大学信息科学与工程学院,湖北武汉 400080)

随着数字多媒体技术的迅猛发展,现代数字技术被广泛应用于大量的音频设备中.现代数字电路的时钟越来越高且供电电压越来越低,这就给与之对应的模拟电路的设计提出了更高要求.低电压下,虽然电路功耗会降低,但是许多传统的电路结构在低电压下无法工作,因此必须要设计在低电压下能较好工作的电路[1].音频设备中核心电路就是ADC电路,高品质的音频设备对ADC 的精度和功耗要求较高.在主流的ADC 拓扑结构中,Σ-Δ ADC 的精度最高.Σ-Δ ADC 利用过采样和噪声整形技术将信号的处理转移到数字域上,极大降低了模拟电路的复杂度,减少了Σ-Δ ADC 的功耗.因此Σ-Δ ADC 相较于其他ADC 结构有更高的精度、更好的功耗特性和鲁棒性[2].Σ-Δ ADC 主要由模拟调制器和数字滤波器组成,模拟调制器是Σ-Δ ADC 的核心电路[3].因此针对Σ-Δ ADC 中调制器的设计,提出了一款低电压、低功耗、高精度的Σ-Δ ADC 调制器.本文通过改进调制器结构和系数来优化环路滤波器的传递函数,解决了传统调制器中输入信号范围限制问题,提高了电路的稳定性.同时对调制器中的放大器和比较器电路进行优化设计,降低了调制器电路设计的复杂性和功耗.在1.2 V 低电压和SMIC0.11 μm 工艺下,该调制器的有效位达到16 位以上,电路功耗仅1.17 mW 左右,版图面积为0.122 mm2左右.

1 调制器系统设计

1.1 结构设计

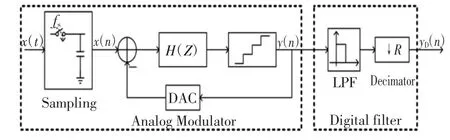

Σ-Δ ADC 的结构图如图1 所示,主要由模拟调制器和数字滤波器组成.

图1 Σ-Δ ADC 结构图Fig.1 Σ-Δ ADC structure diagram

针对图1 中调制器的结构,文献[4]提出了一款应用于音频设备的低电压调制器,并对调制器的量化器进行了较大改进.把一个二阶前馈噪声整形环路与多速率噪声整形量化器结合在一起,构成一种新的调制器结构.该结构降低了量化器输入幅值,避免因量化器过载导致系统不稳定,解决了前馈结构中输入信号范围被限制的问题.虽然文献[4]提出的结构解决了输入信号范围问题,提高了环路的响应速度,但是多速率的上采样需要多个采样时钟,增加了电路的复杂度.采用多个有源加法器、微分器和积分器增加了电路的功耗和版图面积.

文献[5]提出了一种单环双状态的指数增长式Σ-Δ ADC 结构,该结构有两个状态阶段,即线性阶段和指数累积阶段[5].该结构将线性阶段中对热噪声和非线性影响的高抑制能力及指数累积阶段中迅速提升信噪比的能力有效结合起来,极大提升了Σ-Δ ADC 的性能.但是文献[5]提出的ADC 结构设计较为复杂,该ADC 包括两个阶段,需要设计控制时序来控制两个阶段的交替工作.同时量化器的位数设计较高,对DWA 算法的要求较高,而在指数累积阶段,DWA 算法的有效性降低,因此要设计更为可靠的DWA 算法.

文献[6]提出了一款低电压前馈结构调制器,通过对子电路的功耗进行优化,降低调制器的整体功耗.但是,文献[6]提出的调制器的稳定性受输入信号幅值影响较大,量化器和积分器容易发生过载而导致调制器不稳定,影响调制器精度.

本文参考文献[4-6]中的结构,提出一种新的调制器结构.该结构克服了文献[4-6]中结构功耗过大、电路结构复杂和输入信号幅值受限问题,保证了调制器的精度和稳定性,有效降低了电路设计的复杂性,减少了调制器的功耗.利用对放大器和比较器的优化,降低了对DWA 算法的要求,减小了非线性失真.本文提出的调制器结构图如图2 所示,该结构由积分器、加法器、量化器、DWA 算法及反馈DAC 构成.

图2 调制器结构图Fig.2 Modulator structure diagram

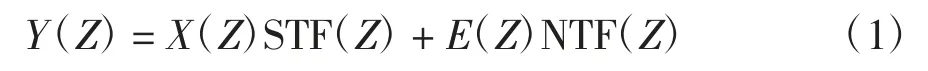

由调制器的结构图和线性分析方法,可以得到调制器的Z 域传递函数如式(1)所示.

式中:STF(Z)为信号传递函数,NTF(Z)为噪声传递函数;X(Z)、Y(Z)分别为输入与输出信号;E(Z)为噪声.其中,STF(Z)如式(2)所示.

式中:a1、a2、a3为调制器中积分器的级间增益系数;b1、b2、b3为调制器的前馈系数.

由式(2)可知,本文通过对调制器结构进行改进,使STF(Z)呈现低通特性.相对传统的全通特性来说,对输入信号进行低通滤波,对输入信号中耦合的输入噪声进行了一定程度的抑制.同时该结构减少了输入到加法器的前馈支路,降低了加法器输出信号的幅值,使得量化器不会因输入信号幅值过大而发生过载,既解决了输入信号范围限制的问题,也优化了调制器的整体功耗.

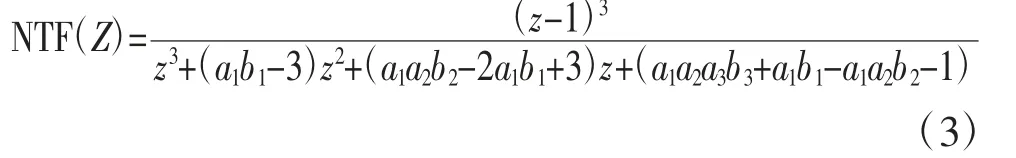

NTF(Z)为噪声传递函数,对调制器噪声进行处理,其式如(3)所示:

对于噪声传递函数,本文利用MATLAB 设计式(3)噪声传递函数中的系数,保证噪声传递函数呈高通特性,实现调制器的噪声整形功能.

1.2 MATLAB 建模设计

衡量调制器噪声性能的常用参数为信噪比,调制器信噪比大小由式(4)表示:

式中:n 为量化位数;L 为调制器阶数;OSR 为过采样比.

为了使ADC 达到要求的16 bit 精度,本文利用Simulink 对调制器结构进行建模,确定结构参数,Simulink 的模型如图3 所示.

图3 调制器Simulink 图Fig.3 The modulator Simulink diagram

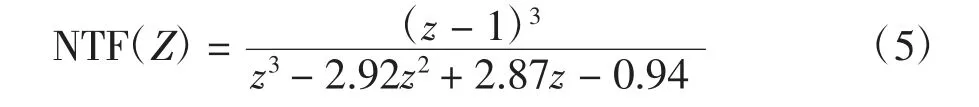

经过对调制器Simulink 建模仿真,为了使调制器达到精度要求,式(4)中参数L 和n 设为3,为实际电路设计留足裕量.过高的采样频率会导致高数字功耗,不利于ADC 的功耗优化,取OSR 为128.对于调制器传递函数系数设计,利用MATLAB 对调制器系数进行建模,在保证调制器的高性能条件下,对调制器的系数进行设计.通过式(2)可以直观看到调制器结构的信号传递函数呈现低通特性,满足了此次的设计要求.因此主要对噪声传递函数NTF(Z)进行系数设计,令噪声传递函数NTF(Z)呈现高通特性,将系统中的量化噪声进行整形.利用MATALB设计一个三阶的高通巴特沃斯滤波器,利用高通巴特沃斯滤波器的函数设计噪声传递函数的系数.高通巴特沃斯滤波器的通带内有最大的幅度平坦特性,滤波器的系数有较大的容差,而且对电路参数不敏感,受输入信号的影响较小[7].根据所设计的滤波器系数得到本文噪声传递函数的Z 域形式如式(5)所示.

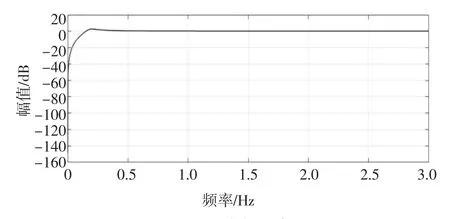

经过系数设计后,式(5)的噪声传递函数对应的频谱图如图4 所示.

由图4 的噪声传递函数频谱图可知,本次设计的NTF(Z)函数的频谱呈现高通特性,能够较好地将量化噪声调制到高频阶段.根据设计的调制器系数a1=1/13,a2=1/3,a3=1/5,b1=1,b2=1,b3=1,得到调制器信号传递函数STF(Z)如式(6)所示:

图4 NTF(Z)频谱图Fig.4 NTF(Z)spectrum

由调制器结构图可以得到,当信号进入三级级联的积分器后输出信号幅值如式(7)所示:

式中:Vin为三级积分器的输入信号;Vout为经过三级积分器处理后的输出信号.

经过系数设计后,使得增益系数a1、a2、a3均小于1,因此调制器中的三级积分器会将输入信号幅值逐级减小,使得输入信号经过积分器后进入加法器,以及求和后进入量化器时都不会发生过载.进一步解决了输入信号幅值被限制的问题,拓宽了线性范围.最终得到设计的调制器的主体电路如图5 所示.

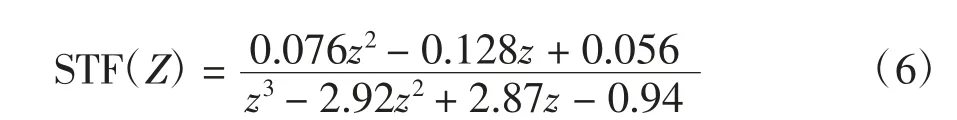

图5 调制器电路Fig.5 Modulator circuit

由图5 可知,改进的调制器结构解决了因输入信号幅值过大导致的过载问题,拓宽了调制器的输入范围,降低了调制器的复杂性和整体功耗.该调制器主要由开关电容积分器、无源加法器、量化器及反馈DAC 组成.而放大器和比较器是调制器中积分器和量化器的核心电路,因此对放大器和比较器的优化也是保证调制器性能的关键之一.

2 调制器子电路设计

2.1 OTA 放大器电路

OTA 放大器是系统环路滤波器的重要组成部分,是主要的功耗产生模块,因此提高放大器的性能,优化放大器的功耗是保证ADC 良好性能的关键.目前,大多数ADC 中的OTA 放大器都采用折叠式共源共栅放大器结构或套筒式共源共栅放大器结构作为主体结构.套筒式共源共栅放大器结构虽然能获得高增益和高带宽,但是限制了输出信号摆幅.该结构由于采用了叠层的共源共栅结构,使放大器对供电电压要求较高,因此该结构不适合低电压供电环境.虽然折叠式共源共栅放大器结构解决了输出摆幅的问题,可以在低供电电压环境下较好的工作,放大器增益和带宽均达到设计要求,但是该结构由于增加了支路,使得电路功耗较大,不利于放大器的低功耗设计[8-9].

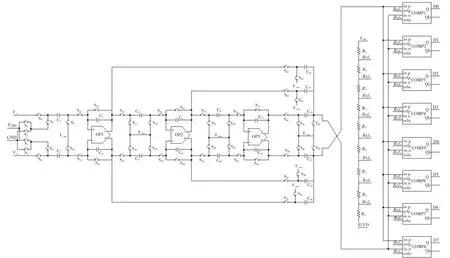

综上所述,本文提出了一款低电压、低功耗的OTA 放大器,在保证高增益和高带宽的条件下,既解决了输出摆幅的问题,又降低了放大器的功耗.采用全差分的结构抑制输入1/f 噪声,减少调制器的噪声成分.本文设计的OTA 放大器的电路结构如图6所示,图中VDD为电源电压,GND 为电源接地端.

图6 OTA 放大器Fig.6 OTA amplifier

由图6 所可知,在输入级中加入了M4、M5、M6管,此时OTA 放大器的跨导如式(8)所示:

式中:gm2和gm4分别为M2管和M4管的跨导.

OTA 放大器的输出阻抗如式(9)所示:

式中:gm9和gm11分别为M9管和M11管的跨导;ro2、ro4、ro7、ro9、ro11、ro13分别为对应编码MOS 管的等效阻抗.

联立式(8)(9),得到OTA 放大器的增益Av如式(10)所示:

根据式(8)(9)(10)可知,当IM4、IM5的电流增加,IM13、IM14的电流减少时,放大器的整体跨导和输出阻抗都迅速增大,因此放大器的增益得到极大提高.可以通过对M13和M5管所在支路电流的分配,来控制OTA 放大器的增益和带宽.该结构在保证高增益和带宽的条件下,既解决了输出电压摆幅的问题,也减小了流入M13和M14管所在支路的电流,降低了OTA放大器的功耗.

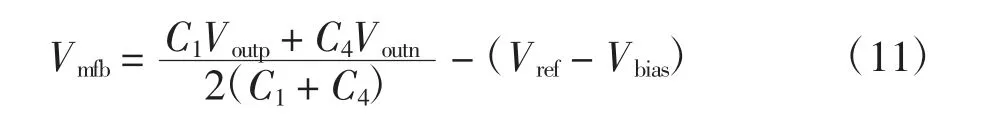

设计开关电容共模负反馈作为放大器的共模稳定电路,共模输出如式(11)所示:

式中:Voutp和Voutn均为放大器的差分输出信号;Vref为参考电压;Vbias为偏置电压.若电容C1=C4,则式(11)可用式(12)表示

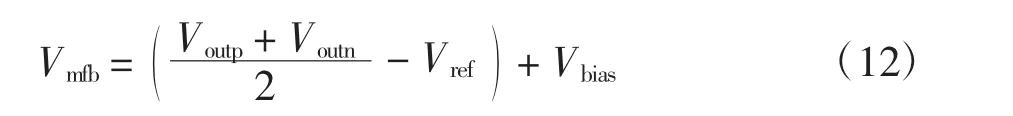

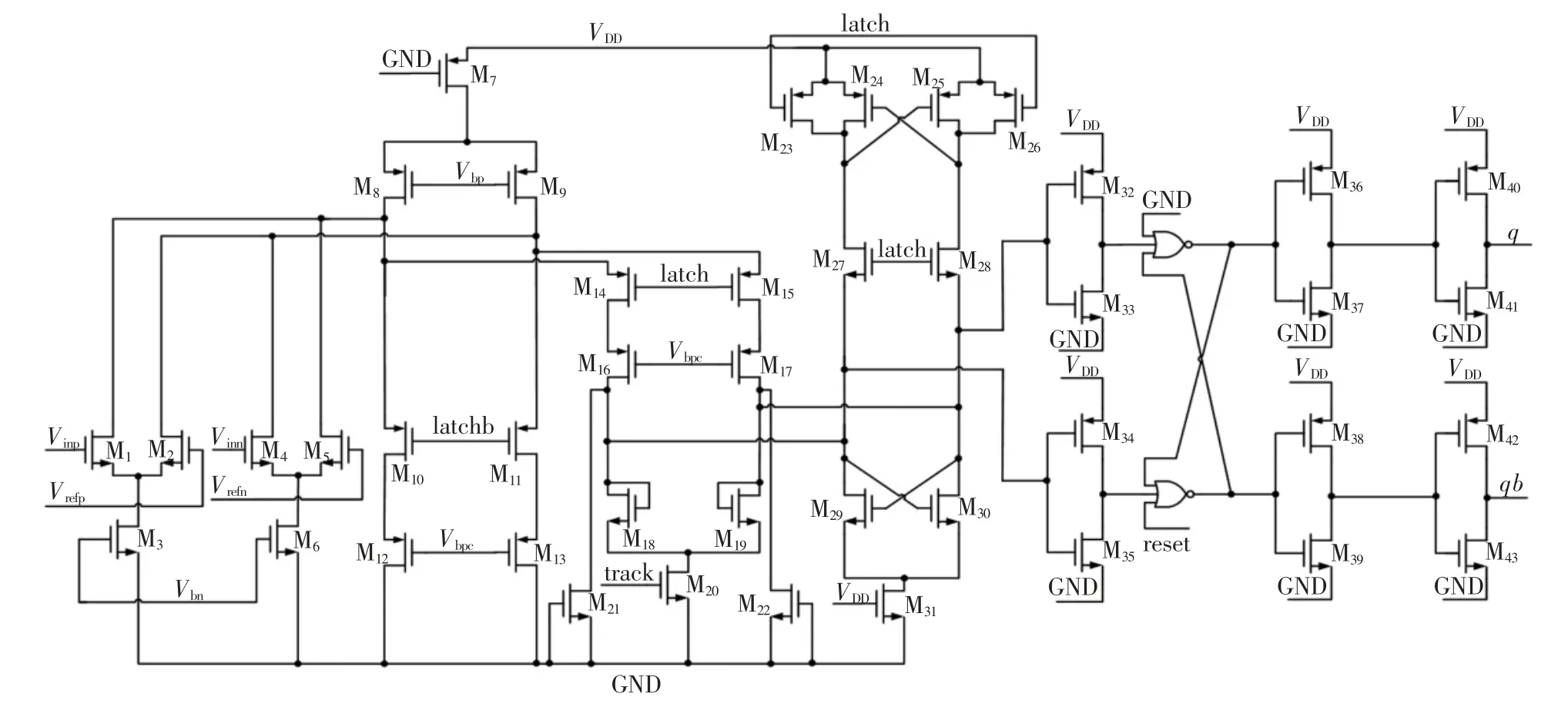

由式(12)可知,开关电容共模负反馈实现了放大器对共模负反馈的全部要求.相较于传统开关电容共模负反馈来说,简化了电路结构,电容数量减少了一半,减少了版图面积,动态开关电容功耗极小,对放大器的功耗进行了优化.本文设计的放大器与文献中放大器指标对比如表1 所示.

表1 放大器性能指标Tab.1 Amplifier performance indicators

从表1 可以看出,本文改进后的放大器在增益和带宽满足设计要求的情况下,相较其他文献的比较器来说,功耗有较大优化.

2.2 比较器电路

目前,在大多数调制器中采用全动态比较器,文献[10]提出了对全动态比较器改进的电荷分享型动态比较器.虽然这些比较器的响应速度较快,功耗较低,但是纯动态比较器没有明确的工作点,该比较器的噪声比较复杂,且对工艺和寄生效应都较为敏感[11-12].

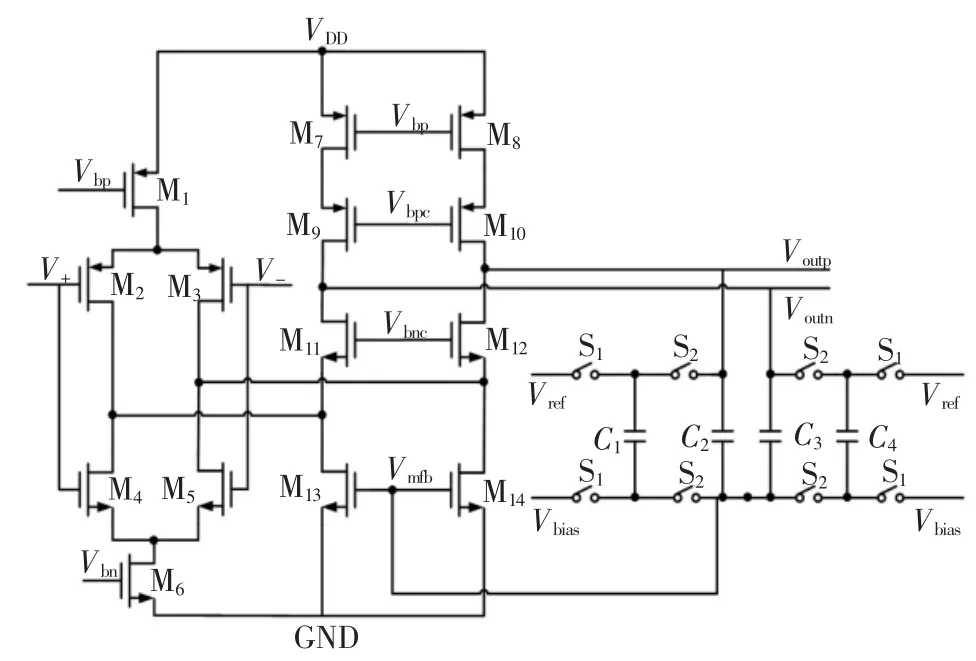

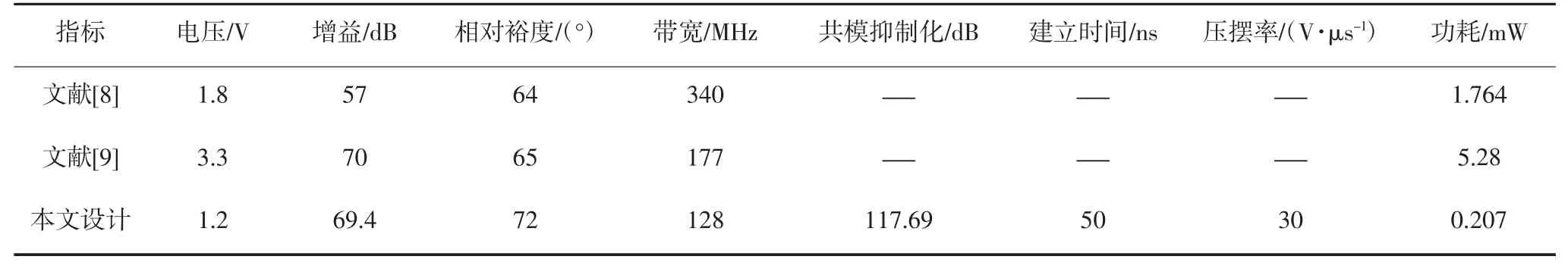

本文提出了一种改进的比较器结构,在比较器中加入中间级,既克服了纯动态比较器中噪声和寄生效应的影响,又保证了比较器的响应速度和低功耗特性.比较器电路如图7 所示.

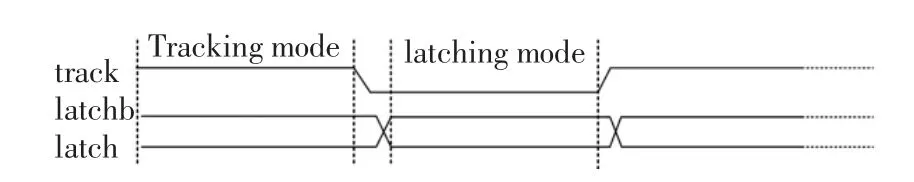

从图7 可以看出,比较器电路主要由预放大级、比较级和输出缓冲级构成.同时考虑比较器前级积分器为全差分输出,因此动态比较器采用4 路的输入结构.其中时钟track、latchb、latch 来控制比较器的工作模式,时钟图如图8 所示.

图7 比较器电路Fig.7 Comparator circuit

图8 控制时钟Fig.8 Control of the clock

由图7 和图8 可知,比较器的工作包括两个阶段,即跟随阶段和锁存比较阶段.当比较器处于跟随阶段即时钟中的Tracking mode 段时,预放大级中的M10、M11截止且M14、M15导通,比较级中M27、M28截止.比较级的输出恒定为高电平,比较器跟随预放大级输出.预放大级开始对输入信号进行放大,将输入信号(Vinp-Vinn)-(Vrefp-Vrefn)放大至比较级能识别的大小.当比较器处于锁存比较阶段即时钟中的latching mode 段时,预放大级的M10、M11导通且M14、M15截止,比较级的M27、M28导通.比较级形成正反馈将预放大级的输出迅速拉至逻辑电平对应的电压大小,完成对输入信号的比较.同时由于M14和M15截止,使得比较级中的回踢噪声无法传回预放大级,减少了比较器中的回踢噪声.由于该比较器只在预放大期间即Tracking mode 段消耗功耗,因此整个比较器的功耗极低.该比较器指标与其他文献对比如表2所示.

由表2 可知,本文设计的比较器相较于文献[10]和文献[11],在功耗和精度上有很大程度的改善,尤其在功耗上有较大优化.

表2 比较器性能指标Tab.2 Comparator performance indicators

3 调制器的测试结果

调制器设计是基于SMIC0.11 μm 的器件工艺,在调制器电路完成后,对调制器电路进行版图设计.并在版图完成后对版图进行设计规则验证(Design Rules Check,DRC)和版图与电路匹配性验证(Layout Versus Schematic,LVS),保证版图的准确性和可靠性.在DRC 和LVS 验证完成后,得到调制器电路的最终版图如图9 所示,版图面积为0.122 mm2左右.

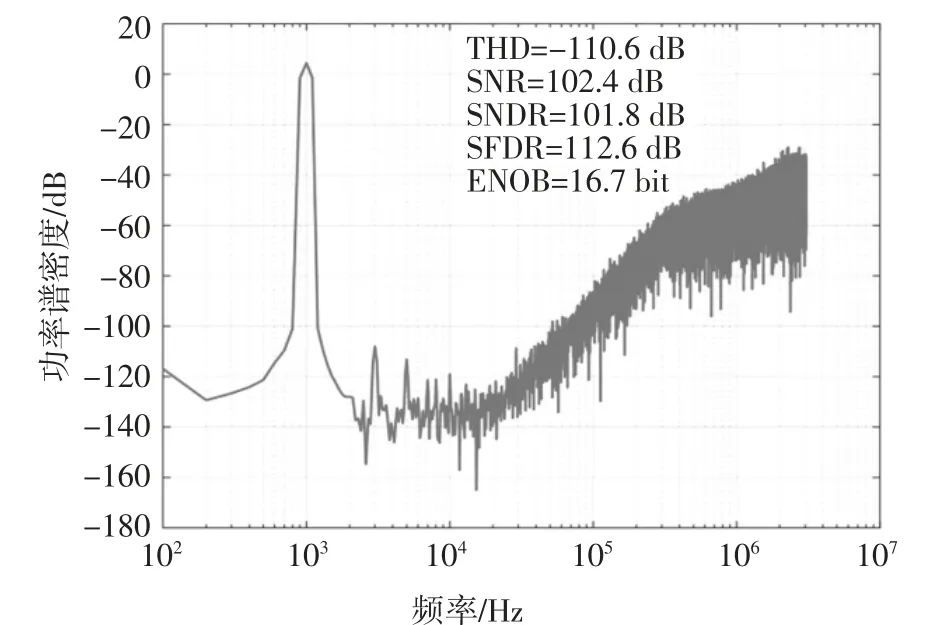

在完成版图设计和后端设计后,对芯片进行流片.在电源电压为1.2 V,采样频率为6.144 MHz,过采样比为128,输入信号幅值为1 V,频率为1 kHz的正弦信号的测试条件下,对芯片中的Σ-Δ ADC 调制器进行测试.经过测试得到调制器的功耗仅为1.17 mW 左右.将调制器的输出结果导入MATLAB进行FFT 分析,计算调制器的信噪比.经过FFT 分析后,可以得到调制器的功率谱图如图10 所示.

图10 功率谱图Fig.10 Power spectraldensity

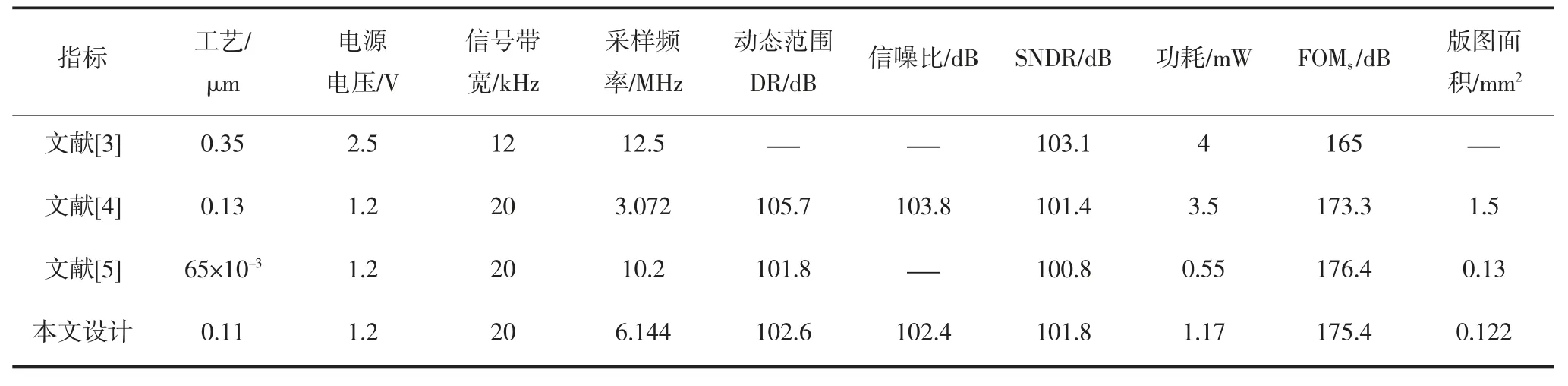

由图10 可知,调制器中产生的量化噪声成功地被调制到了高频段,达到了噪声整形和过采样对噪声的处理效果.被调制到高频段的量化噪声最终将被Σ-Δ ADC 后级的数字滤波器滤除,极大地提高了ADC 的噪声性能.经过计算得到调制器的信噪比达到102.4 dB,有效位达到16.7 位,满足了音频应用领域对调制器精度的设计要求.该调制器与其他文献中调制器的性能指标的对比如表3 所示.

其中,表3 中品质因数(FOMs)如式(13)所示:

式中:SNDR 为信噪失真比;BW 为信号带宽;power为功耗.

由表3 可知,本文提出的调制器指标相比其他文献中的调制器指标来说,在信噪比和FOMs值接近的情况下,功耗和版图都有较大优化,在1.2 V 的低电压下能较好的工作.

表3 调制器指标对比Tab.3 Modulator index comparison

4 结论

本文基于SMIC0.11 μm 工艺,设计了一款改进的单环三阶三位量化的Σ-Δ ADC 调制器,能够较好地应用于音频领域.通过对调制器结构和系数的优化,解决了大多数调制器结构中因过载导致的系统不稳定问题,拓宽了输入信号的范围,进一步提高了调制器的噪声性能.同时改进了比较器和OTA 放大器,极大程度降低了调制器的功耗,提高了调制器的响应速度.芯片的成测结果表明,该调制器在电源电压为1.2 V,采样频率为6.144 MHz,过采样比为128的条件下,调制器的信噪比达到102.4 dB,有效位达到16 位以上,而调制器的功耗仅为1.17 mW 左右,版图面积为0.122 mm2,实现了高精度、低功耗和低电压的设计目标.