高电压输入双管反激辅助电源驱动研究

胡亮灯 赵治华 孙 驰 艾 胜

(海军工程大学舰船综合电力技术国防科技重点实验室 武汉 430033)

1 引言

中高压、大容量电力电子装置在电路结构、空间布局及控制功能上往往都存在较明显的分布特征,非常适合采用分布式辅助电源为装置二次回路供电,实现整个变流装置从模块到子系统都具有真正可插拔的标准化和模块化特征,从而提高系统的冗余性和可靠性[1]。分布式辅助电源供电是通过在装置中每个变流模块均设置单独辅助电源为其供电来实现,辅助电源输入为变流模块母线电容电压,而辅助电源输出直接为变流模块驱动或控制电路供电。采用分布式辅助电源为系统二次回路供电方式可以简化装置中内外二次线路连接,降低线路本身的绝缘及防电磁干扰要求,避免了传统的电力电子装置功率电源和控制电源严格的上电和断电次序问题,甚至可取消柜体内UPS 等装置。由于辅助电源电位与相应的变流模块电位一致,降低了多电平串联拓扑结构下传统集中供电要求驱动或控制电路高压隔离问题。为确保装置安全可靠运行,分布式供电方式要求辅助电源能在高电压宽电压输入范围内工作。双管反激拓扑结构的辅助电源其主开关电压应力仅为输入电压,漏感能量能回馈到输入侧,无需吸收电路,效率高,其非常适合中高压变流系统辅助电源宽范围、高电压输入要求[2,3]。图1为宽范围、高电压输入双管反激辅助电源示意图,辅助电源主电路由MOS 管VT1、VT2,二极管VD1、VD2及变压器构成,开关管VT1、VT2由PWM 芯片经高隔离双管同步驱动器控制。

图1 高电压输入双管反激辅助电源示意图Fig.1 The sketch of high voltage input double-transistor flyback auxiliary power supply

从图1 可以看出,对于高电压输入的双管反激辅助电源,其关键技术之一是具有安全、可靠的隔离型的双管同步驱动器。因为高性能的开关管驱动技术不但是实现开关管正常开通和关断的基础,也是保证开关管安全运行的基础,开关管的关键电气性能都与其密切相关,是影响整个辅助电源可靠性的一个非常重要的因素。基于双管反激或正激拓扑结构的辅助电源上下开关管驱动信号是分别基于浮地和参考地,因此驱动信号必须隔离,此外,为了防止辅助电源上下开关管电压不均,要求驱动信号具有较高的同步性等。

高电压输入双管反激辅助电源驱动具有高电压隔离、高频率、低延时和无外接电源等特点,传统的光耦芯片隔离驱动方案耐压不够、延时大,需外接驱动电源;光纤隔离驱动方案可以满足耐压要求,但需配高隔离的驱动电源,上述两方案均不适合应用于简单、经济的自激辅助电源中。基于此,本文对高电压输入双管反激辅助电源驱动展开研究。

目前,关于双管驱动的相关文献如下:文献[4]指出高压自举驱动芯片常用来直接驱动处于高电位的开关管,外部器件少,但芯片内部的电平转移电路、隔离电路在高频下发热严重,且当前自举驱动芯片最高耐压为1 200V,不适合于更高电压应用场合。文献[5]采用两个相同的低耐压驱动芯片实现高低电位开关管有效控制。两驱动芯片之间通过一个耦合电容隔离驱动信号及提供电源,但该驱动方案难以实现高低电位开关管开通关断同步。文献[6,7]针对两管串联变换器,提出一种低电位开关管采用PWM 芯片控制,而高电位开关管采用浮地自供电方式进行驱动的方案,此方案简单,但存在上、下管驱动信号不同步,上管开通关断性能难以保证等缺点。瑞士Concept 公司设计了一款型号为2SD106A的双路驱动器,该驱动器通过变压器实现对驱动信号及驱动电源进行隔离,目前该驱动器工作电压仅为1 200V,体积大,价格昂贵。北京落木源公司设计了一款基于变压器隔离的型号为TX-KD202 双路驱动器,该驱动器采用了分时自供电技术,无需外接电源,直接实现了对高低电位开关管驱动控制,大大简化外部电路,但该驱动器对输入脉冲有最小宽度限制,目前,该驱动器工作电压为1 700V,无法应用于更高电压场合。

综上,双管驱动方法主要有:自举芯片驱动、电容隔离驱动、浮地自供电驱动、变压器隔离驱动等,此外还有光耦隔离驱动、光纤隔离驱动等方案[1-8],而变压器隔离驱动由于其简单、经济为非常有效的方法[9-11]。文献[9]在变压器一次侧采用一个简单的PWM 控制芯片,变压器二次侧采用稳压管进行钳位驱动,文中没对其他变压器驱动方案进行对比分析。文献[10]提出一种驱动延时小且关断有负压偏置的开关管驱动方案,但是电路比较复杂。文献[11]提出一个简单、超紧凑、隔离型开关管驱动电路,该驱动电路开通关断迅速,关断有负压偏置,但要求双极性驱动脉冲。

文献[9-11]研究的变压器隔离驱动方案均不适合双管反激拓片开关管驱动,基于此,对几种适合双管反激拓扑变压器隔离驱动电路进行分析,如图2 所示,进而确定采用的辅助电源驱动方案[12-16]。

图2 变压器隔离双管驱动电路Fig.2 Isolated double-transistor drive circuit with transformer

图2a~图2d 均为适合于双管反激拓扑的变压器隔离驱动电路。图2a 方案用比较简单方式对驱动功率进行了放大,缺点是三极管发热,驱动变压器存在饱和的风险,关断没有负压,关断速度及抗干扰能力不能保证。图2b 方案优点是开关管关断时,开关管栅极电容放电电流被限制在最小的环路中,进而栅极得以保护,通过三极管Q1关断开关管,避免了栅极闭环电感、线路感应电阻和驱动输出阻抗对关断的影响,但由于三极管Q1存在集电极结导致开关管栅-源极电压不能下拉到 0;开关暂态高的dv/dt 下,开关管存在自导通的风险。图2c 通过三极管组成的推挽式电路对PWM 芯片输出脉冲进行了放大,简单、经济,但推挽电路存在交越失真,防止变压器饱和,在变压器一次侧设置了耦合电容C1,但导致开关管栅-源极驱动电压幅值受控制占空比影响,大占空比下MOS 管栅-源极正压将过低,负压将过大,利用稳压管 VD6、VD7虽钳位了栅-源极关断负压,但由伏秒平衡知该稳压管同时也限制了开关管栅-源极开通正压,图2c 方案应用场合为控制占空比小于50%。对于控制占空比大于50%场合时,可采用图2d 所示电路,其通过变压器一次侧、二次侧均设置耦合电容,实现一次侧驱动电压复原,但该方案在开关管关断时,一次侧电容长时间与变压器一次绕组相连,可能导致变压器饱和,此时变压器二次侧电容相当于直接作用于开关管栅-源极,存在开关管失控的风险,利用驱动芯片对PWM 芯片输出驱动信号进行放大,简单,但驱动芯片费用高。

上述几种变压器隔离双管驱动电路均存在一定的安全隐患,不能直接用于双管反激拓扑开关管驱动,需对上述驱动电路进行改进研究。

本文首先综述了几种双管辅助电源驱动方案,针对高电压输入双管反激辅助电源驱动具有高电压隔离、高频率、低延时和无外接电源等特点,从而确定了变压器隔离的双管驱动方案,并设计了相应的驱动电路。在此基础上,调整驱动变压器绕组比,确保了所驱动开关管在各种条件下的充分导通。为提高双管反激辅助电源上、下开关管驱动信号的同步性,在驱动器输出增加了驱动信号耦合电感。此外,根据驱动脉冲上升、平顶、下降三个阶段,给出了驱动器相应的等效电路,推导了相关公式,理清了驱动器主要参数对驱动性能的影响。最后,相关实验验证了上述结论正确。

2 采用的双管隔离驱动电路分析

基于高电压输入双管反激辅助电源要求开关管驱动简单、可靠、经济原则,据图2 所示变压器隔离双管驱动电路的优缺点,确定了本文所研究的变压器隔离双管驱动电路[12-16]。由于辅助电源采用的PWM 控制芯片驱动能力高,而需驱动的开关管VT1、VT2栅极输入电容小,经计算可直接用于开关管驱动,此外,辅助电源控制占空比小于50%,故本文采用了如图3 所示驱动方案。

图3 所采用的驱动电路Fig.3 The adopted drive circuit

图中VD2为关断加速二极管,防止开关管过电流、减少开关管损耗;VD0、VD1为肖特基二极管,为开关管开通和关断过程中可能存在振荡提供回路;VD4、VD5为开关管栅-源极钳位稳压管,以防止驱动脉冲顶端电压跌落过大;C1为变压器一次侧耦合电容,用于隔断驱动脉冲的直流分量,以防止变压器饱和,为开关管关断提供负压,加速开关管关断过程;CBLAS为PWM 芯片电源旁路电容,用于降低开通关断过程中大电流峰值影响;R2为开关管栅极驱动电阻,一般设置在变压器一次侧,用于阻尼开关过程中电感LP和电容C1可能存在的谐振;R3为开关管栅极下拉电阻,作用是确保上电前开关管栅-源极电荷已充分释放。

3 驱动变压器研究

由上节分析,驱动变压器是图3 所示双管驱动电路的核心,故拟对驱动变压器进行设计、改进和研究,并在此基础上,对所设计的双管驱动器分不同驱动阶段进行等效简化。

3.1 驱动变压器设计

由于圆形磁环有连续的磁路径,漏感小,采用该类磁心能实现最好的驱动性能[13]。理想的磁心材料为高磁导率(AL>1 400nH/N2)的铁氧体磁心,磁心材料能够额定运行于MHz 区域。故本文选用EPCOS 公司铁氧体磁环,该磁环磁心截面积 Ae=73.51mm2,电感系数AL=5 400nH/N2。对于驱动变压器,减少绕组匝数,可以减少电感和漏感,但增加匝数可以减少励磁电流,两者综合考虑,一般使用少的匝数实现减少漏感,此外合适的绕线方式也可进一步降低漏感[14]。

一般驱动变压器工作频率 fSW为 50kHz~100kHz 时,设计驱动变压器一次电感LP为2.0mH~4.0mH。本文所研究电源工作频率为50kHz,一次电感LP取2.0mH。

绕组匝数N

为防止磁心饱和,绕组匝数N 需满足

式中,B为磁通密度(T),对于铁氧体磁心,为防止其饱和,一般取 B=0.2T,变压器一次电压 VT为(1-D)VCC,开关管最大导通时间,ton为Dmax/fSW约10μs,这里驱动变压器一次输入和两个二次输出绕组匝数均取N=24,绕组比为1∶1∶1。

对于环形变压器,绕组绕线方式主要有分开绕制和多绕组并绕[13],如图4 所示。

图4 驱动变压器绕线方式Fig.4 Drive transformer winding wire-wound mode

绕组分开绕制优点是绕组间能较好地实现高压隔离,但漏感大,实物图如图4a 所示。电桥测试其一次电感、漏感分别LP=3.04mH、漏感Llk=32μF。三线并绕优点是漏感小,但绕组间隔离需注意。可根据工作电压范围,采用相应等级的高压线来实现绕组间隔离。实物图如图4b 所示。同样的绕组数情况下,其一次电感、漏感分别为 LP=3.028mH、Llk=622nH。

3.2 驱动变压器改进

3.2.1 调整驱动变压器绕组比

双管反激辅助电源PWM 芯片UC3844 启动电压VCC=16V,最小工作电压VCC=11.5V,芯片最小、最大占空比Dmin、Dmax分别为0 和0.48。若UC3844在最大输出占空比下,以最小电压工作时,驱动变压器输出电压(1-Dmax)VCC约6V,此时开关管不能充分导通,通过将驱动变压器输入输出绕组比由1∶1∶1 调整到1∶1.35∶1.35 后,则同样条件下,驱动变压器输出电压将升至约8V,此时开关管已饱和导通(MOS 管驱动电压8~10V 可饱和导通)。考虑到所设计的辅助电源VCC电压为24V,当UC3844芯片以最小输出占空比工作时,则驱动变压器输出电压(1-Dmin)VCC约为24V,超过了开关管栅-源极承受的最大电压,故开关管栅-源极并10V 稳压管进行钳位,采用10V 稳压管可确保在不同占空比或电压VCC时,开关管驱动电压基本稳定。

驱动变压器绕组比调整后,VCC为24V 时,芯片在最大输出占空比,开关频率为50kHz 情况下驱动波形如图5a 所示,图5b为对应的驱动变压器电路。从图 5a 中可看出驱动 PWM 脉冲幅值约为+/-10V,确保了开关管充分导通和可靠关断。

图5 驱动变压器Fig.5 Drive transformer

3.2.2 增加栅极信号耦合电感

由于控制电路、驱动电路延迟和传输线路延迟上的差异及所驱动开关管本身差异,双管反激辅助电源上、下开关管VT1、VT2的栅-源极驱动信号往往存在不同程度的不同步现象。如果栅-源极驱动信号不同步严重,则将导致上、下开关管电压不均严重。为此,在驱动变压器二次侧采用栅极信号耦合电感(同步变压器),以提高上、下管驱动信号的同步性[17]。

引入耦合电感不会明显增大驱动电路损耗,也不影响装置的开关频率。耦合电感Lm

式中,ΔT为两驱动信号时间差;Ugs+、Ugs-分别为开关管开通电压、关断电压,Ugs1、Ugs2为通过耦合电感后上下管驱动电压;CISS为开关管栅极输入电容。

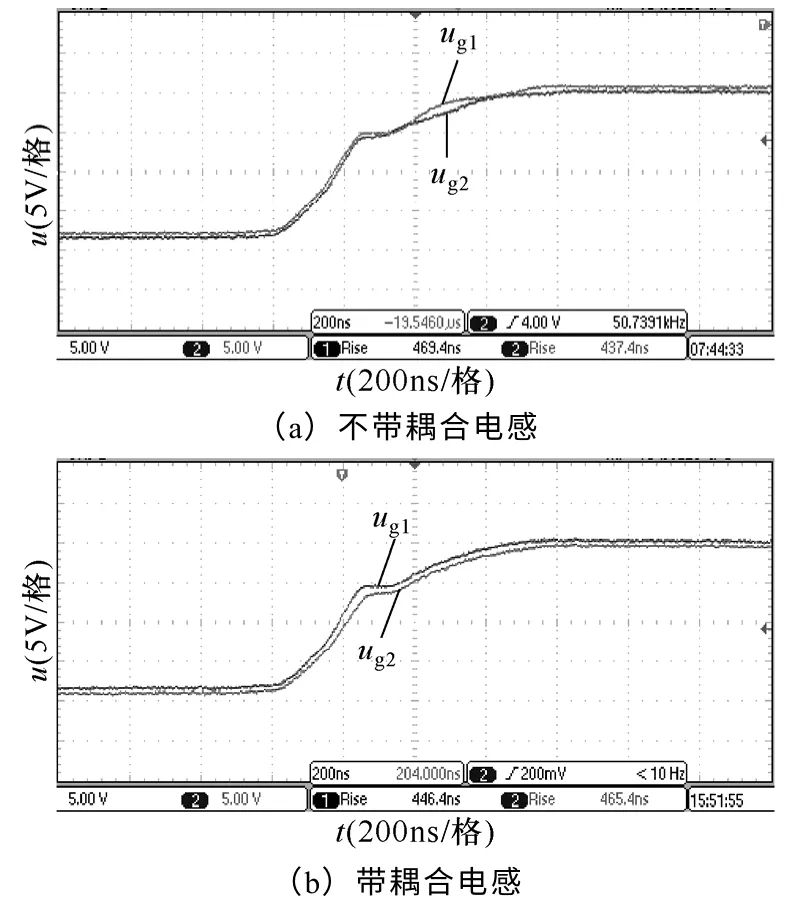

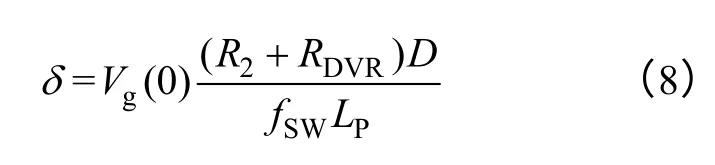

为验证上述方案的正确性,利用磁环将驱动变压器输出反向并绕方式制作了耦合电感,电感值为0.8mH,在此基础上,对不带耦合电感及带耦合电感的驱动变压器输出波形进行了对比实验,不带耦合电感驱动变压器输出波形上升沿如图6a 所示,带耦合电感驱动变压器输出波形上升沿如图6b 所示,两者对比知,图6b 波形ug1和ug2几乎完全重合,表明带耦合电感的驱动变压器同步性能明显要好。

图6 脉冲上升过程Fig.6 Drive voltage rise process

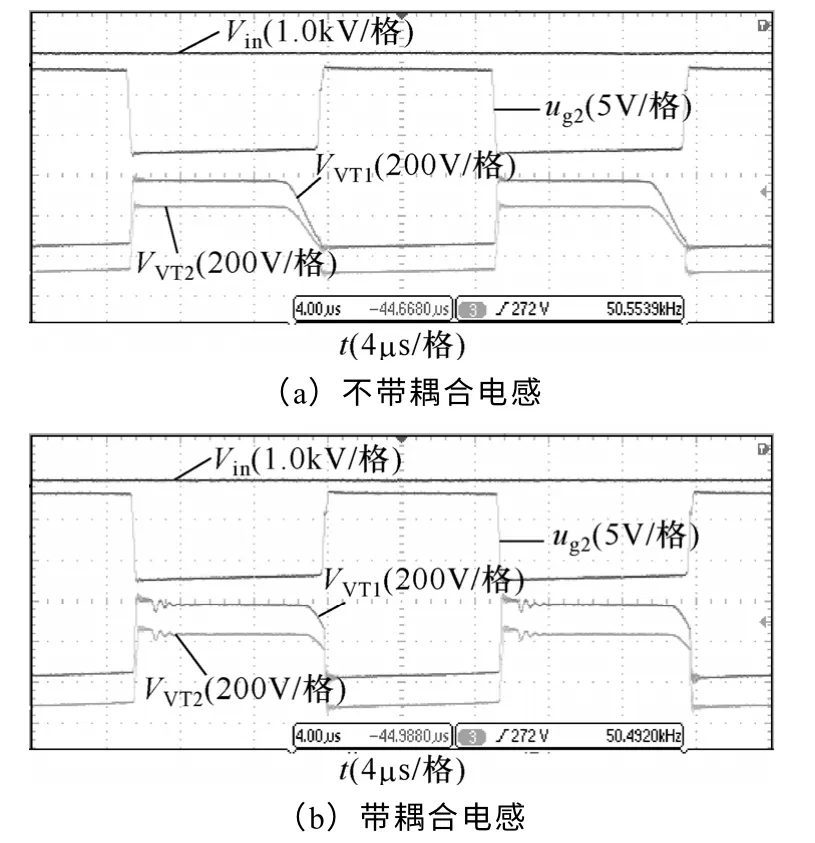

进一步验证上述结论的正确性,对不带耦合电感及带耦合电感的驱动变压器在双管反激辅助电源上进行了实验验证,其中不带耦合电感辅助电源波形如图7a 所示,带耦合电感辅助电源波形如图7b所示。

图7 辅助电源波形Fig.7 APS waveforms

图7 中,Vin为辅助电源输入电压,VVT1为辅助电源上管VT1漏-源极电压波形,VVT2、ug2分别为辅助电源下管VT2漏-源极、栅-源极电压波形。由图7a、图7b 开关管VT1、VT2电压波形VVT1、VVT2下降沿对比知,图7b 波形VVT1、VVT2下降沿吻合要好,进一步验证了变压器输出串入驱动信号耦合电感,可提高辅助电源上下开关管的同步性。

3.3 驱动器不同驱动阶段分析

为了从原理上分析图3 所示变压器隔离驱动电路相关参数对驱动性能的影响,据驱动脉冲上升、平顶和下降三个不同阶段,搭建分别如图8 左边所示电路。通过将驱动变压器二次侧绕组折算到变压器一次侧,则电路可进一步等效为图8 右边所示电路。

图8 驱动器不同驱动阶段等效电路Fig.8 Equivalent circuits of different stage drivers

下面基于图8 驱动器不同阶段等效电路,分析如下。

3.3.1 驱动脉冲上升过程

开关管开通过程,即栅-源极驱动电压上升较快部分,该阶段与稳态分析中的高频区相对应,此时励磁电感LP感抗大,其支路可近似为开路(2πfSWLP>>RG,I)。

脉冲上升栅-源极电压Vg(t):

脉冲上升时间Tr1(0.1Vg~0.9Vg):

从式(6)知Vg(t) 上升时间Tr1随着开关管栅极输入电容CISS、电阻RG或漏感Llk的增加而增加,即栅-源极电压上升速度将减缓。此外,据式(5)知耦合电容C1也影响驱动脉冲上升时间。

3.3.2 驱动脉冲平顶过程

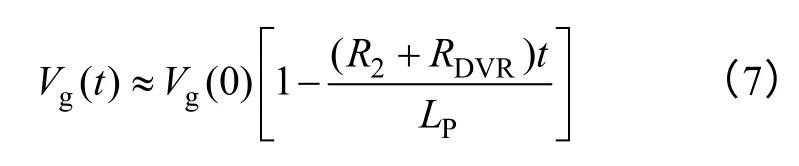

驱动电压的平顶部分与稳态分析中的低频区相对应,此时,耦合电容C1电压近似不变为DVCC。

脉冲平顶栅-源极电压Vg(t)

式中,Vg(0)为栅-源极电容初始电压(1-D)VCC,时间t为驱动脉冲高电平持续时间。

栅-源极电压平顶降落δ

由式(8)知,栅-源极电压平顶降落δ随着D、R2、RDVR的增加或LP的减少而增加。

3.3.3 驱动脉冲下降过程

开关管关断过程,即栅-源极驱动电压下降较快部分,该阶段与稳态分析中的高频区相对应,此外由于漏感Llk能量此前已释放,而电容C1>>CISS,则脉冲下降短暂过程主要是电容CISS放电,此阶段可认为电容C1电压DVCC近似不变。电容CISS放电完毕后,电感Llk、电容CISS和电阻RDVR、RGI将RLC阻尼振荡,振荡周期T 计算公式如式(9)所示。

脉冲下降栅-源极电压Vg(t)

脉冲下降时间Tf(0.9Vg~0.1Vg)

式中,Vg为栅极电压,考虑到Vg≈(1-d)VCC,则式(11)可简化为

4 仿真和实验分析驱动器参数对驱动性能的影响

为了进一步分析驱动器参数对驱动性能的影响,在不同一次电感LP、漏感Llk、耦合电容C1、栅极电阻R2及栅极输入电容CISS情况下对所采用驱动电路驱动性能进行对比仿真和实验验证[18,19]。下述实验波形为开关管没通电流情况下测得,而仿真波形是开关管通正常电流基于PSPICE 仿真软件获得。依据图序,仿真参数与实验参数详见下表。

表 驱动变压器相关参数Tab. Drive transformer relevant parameters

下述实验或仿真图中PWM 波形为PWM 芯片输出波形,也即驱动器输入波形,ug1、ug2波形为驱动器输出波形,也即开关管VT1、VT2驱动电压波形。

4.1 驱动器参考实验波形及分析

从图9 中PWM、ug1、ug2波形对比知,变压器隔离驱动方案延时较小。图9a 栅极电阻偏小,导致上升过程有点小超调,驱动变压器漏感或引线电感导致了关断过程有轻微的振铃。驱动变压器输入、输出线分别交叉绕制及栅极电阻R2由10Ω 调整为20Ω 后驱动器波形如图9b 所示,调整后的驱动器驱动波形有平坦的底部和顶部,陡峭上升、下降沿。

图9 参考实验波形Fig.9 Reference experimental waveforms

4.2 漏感变大时,驱动器波形及分析

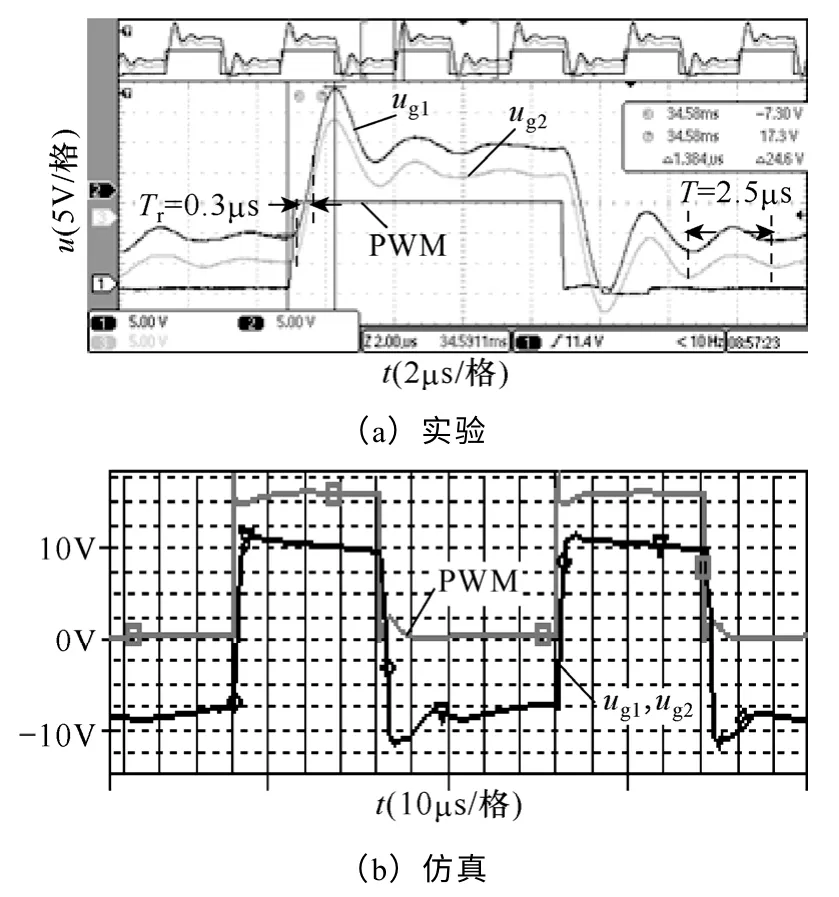

从图10a 可知大的漏感导致驱动脉冲大的延时及较高的振荡,振荡尖峰电压达10V,上升时间Tr1为0.3μs。据式(6)和表中相关数据计算知,上升时间约为0.32μs 与实测值相近。过大的漏感造成大量的低频振荡,据式(9)知振荡周期T为2.36μs与图10a 实测振荡周期为2.5μs 相仿。由于振荡使开关管运行于线性区域,它不能通过增加阻尼电阻来调整。因为此时将需要太大的电阻,而且振荡和下降沿将会太慢。只有重新设计变压器降低过大的漏感才能解决这个问题。图10b为对应的仿真波形。

图10 大漏感波形Fig.10 Large Llkwaveforms

4.3 一次电感变小时,驱动器波形及分析

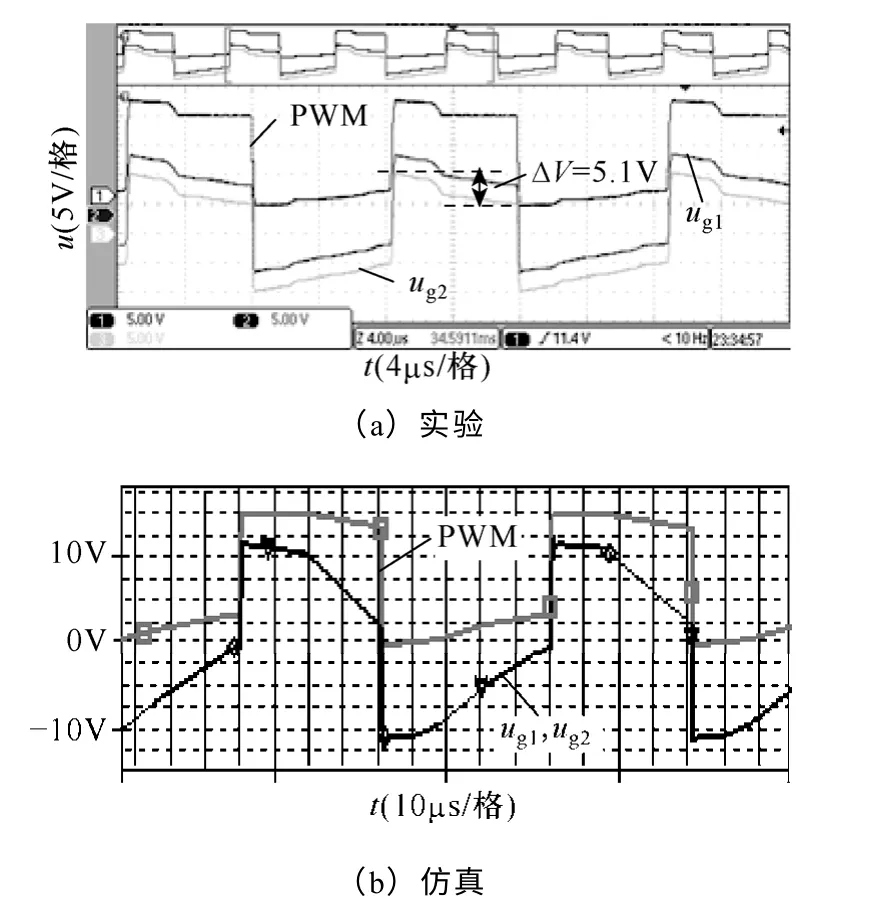

从实验图11a 或仿真图11b 波形均可以看出,过小的一次电感将导致驱动脉冲顶部和底部严重下垂,下垂幅值达5.1V,与式(8)计算的栅-源极电压平顶降落δ为5.26V 基本相符,由(8)也知增加一次电感可以解决该问题。

图11 小电感波形Fig.11 Small Lpwaveforms

4.4 栅极电容变大时,驱动器波形及分析

从实验图12a 或仿真图12b 波形均可以看出大的栅极电容下,驱动脉冲上升延很缓慢。缓慢的上升沿使开关管长时间处于放大阶段,导致开关管快速过热。此外,过大的栅极电容也要求驱动变压器更大的驱动能力。从式(5)亦知:CISS增加时,栅-源极电压上升时间Tr1增加。增加PWM 芯片驱动能力可解决该问题。

图12 大栅极电容波形Fig.12 Large CISSwaveforms

4.5 栅极电阻变大时,驱动器波形及分析

从实验图13a 或仿真图13b 波形均可以看出,由于太大的栅极电阻R2导致边缘脉冲弯曲,慢的上升下降沿使开关管长时间处于放大阶段,导致开关管快速过热,从式(6)知栅-源极电压上升时间Tr1随着R2增加而增加。减少栅极电阻可解决该问题。关断存在振荡,振荡周期约为0.3μs,如图13a 所示。实验值与计算值0.32μs 基本吻合。

图13 大栅极电阻波形Fig.13 Large R2waveforms

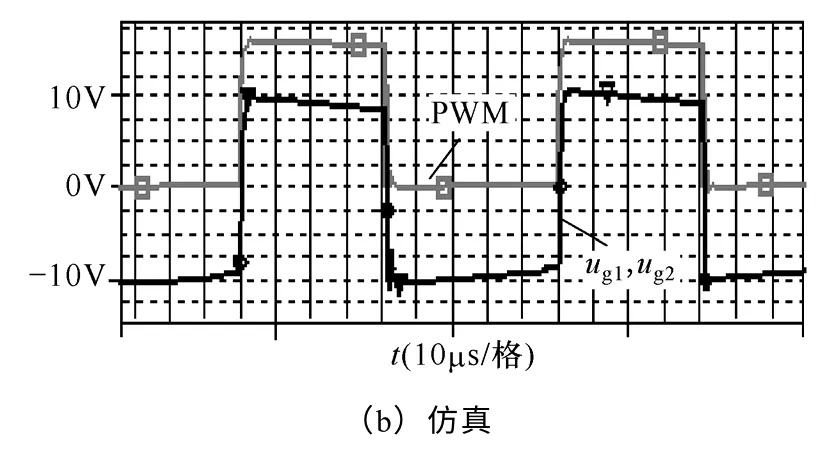

4.6 耦合电容变大时,驱动器波形及分析

驱动器耦合电容C1为2μF,波形如图14 所示,平顶压降为2.6V。图9 电容C1为1μF,平顶压降为2.4V。两者对比知,耦合电容C1增加,平顶压降增加。由于栅-源极电压建立时间随着耦合电容的增加而增加,进而根据式(7)可知顶部栅极电压随着驱动脉冲持续的时间增加而降低。

图14 大耦合电容波形Fig.14 Large C1waveforms

5 变压器隔离的双管驱动器实验验证

为验证设计的带耦合电感的变压器隔离双管驱动器的可行性、正确性,在300V~2 500V 输入24V输出双管反激辅助电源中进行了进一步实验验证。双管反激辅助电源样机实物图如图15 所示。

图15 辅助电源样机实物Fig.15 Entity of APS prototype

当输入电压为2.49kV,开关频率50kHz,负载30W 时,双管反激辅助电源驱动相关波形如图16所示。

图16 输入电压为2.49kV 时,辅助电源波形Fig.16 APS waveforms of input voltage 2.49kV

图16 中,Vin为辅助电源输入电压,VVT1为辅助电源上管VT1漏-源极电压波形,VVT2、ug2分别为辅助电源下管VT2漏-源极、栅-源极电压波形。从ug2波形可以看出其上升下降延时小,关断有负压。开关管VT2导通延迟时间td(on)约80ns,下降时间tf约80ns,关断延迟时间td(off)约135ns,上升时间tr约135ns。实验结果表明设计的带耦合电感的变压器隔离的双管驱动器驱动脉冲上升下降延时小,开通关断迅速,能满足高频高电压输入辅助电源双管驱动要求。

6 结论

(1)针对高电压输入双管反激辅助电源驱动具有高电压隔离、高频率、低延时和无外接电源等特点,对比分析几种可行的变压器隔离双管驱动方案,确定了本文所研究的高电压输入双管辅助电源的驱动电路。

(2)设计了变压器隔离的双管驱动器,通过调整驱动变压器绕组比,确保了开关管在各种控制脉冲下的充分导通,通过增加栅极信号耦合电感,提高了开关管驱动信号的同步性,并实验验证了其正确性。

(3)根据驱动脉冲的不同阶段,将驱动器电路等效为脉冲上升、脉冲平顶和脉冲下降三个阶段,给出相应的等效电路,并推导出各阶段驱动相关公式,分析了驱动主要参数对驱动器性能的影响,并基于Pspice 仿真和实验验证了其正确性。

(4)最后在300V~2 500V 输入24V 输出的双管反激辅助电源样机上进一步验证了所设计的带耦合电感变压器隔离的双管驱动器。

[1]孙驰,张成,艾胜.一种实用的大容量电力电子系统高速光纤环网拓扑及其协议[J].中国电机工程学报,2012,32(15):63-73.Sun Chi,Zhang Cheng,Ai Sheng.Topology and protocol of practical high-speed fiber ring net for large-capacity power electronic systems[J].Proceedings of the CSEE,2012,32(15):63-73.

[2]Murthy Bellur D,Kazimierczuk M K.Two-switch flyback PWM DC-DC converter in discontinuousconduction mode[J].International Journal of Circuit Theory and Applications,2011,39(11):849-864.

[3]Murthy Bellur D,Kazimierczuk M K.Two-switch flyback PWM DC-DC converter in continuousconduction mode[J].International Journal of Circuit Theory and Applications,2011,39(11):1145-1160.

[4]Application Note AN-978.HV Floating MOS-Gate Driver ICs.International Rectifier,Rev D,2007.

[5]Yan Yin,Regan Zane.Dual low-voltage IC design for high-voltage floating gate drives[J].IEEE Transactions on Circuits and Systems—I:Regular Papers,2008,55(6):1751-1758.

[6]Petar J Grbovic.Loss-free balancing circuit for series connection of electrolytic capacitors using an auxiliary switch-mode power supply[J].IEEE Transactions on Power Electronics,2009,24(1):221-231.

[7]Petar J,Grbovi C.High-voltage auxiliary power supply using series-connected MOSFETs and floating selfdriving technique[J].IEEE Transactions on Industrial Electronics,2009,56(5):1446-1455.

[8]Shihong P,Jahns T M.A self-boost charge pump topology for a gate drive high-side power supply[C].18th Annual IEEE Applied Power Electronics Conference and Exposition,2003:126-131.

[9]Chen Baoxing.Isolated half-bridge gate driver with integrated high-side supply[C].PESC IEEE,2008:3615-3618.

[10]G Hunte.A reliable,low cost IGBT gate drive circuit[C].Power Engineering Conference,AUPEC '08.Australasian Universities,2008:1-4.

[11]Van Nguyen,Crebier J C,Jeannin P.Compact,isolated and simple to implement gate driver using high frequency transformer[C].26th Annual IEEE Applied Power Electronics Conference and Exposition,2011,1092-1098.

[12]L Balogh.Design and application guide for high speed MOSFET gate drive circuits[C].Texas Instruments Power Supply Design Seminar 2001,SEM-1400.

[13]http://wiki.4hv.org/index.php/Gate_drive_transformer.

[14]Patrick Scoggins.A guide to designing gate-drive transformers[J].Power Electronics Technology,2007:32-36.

[15]Ray Ridley.Gate drive design tips[J].Power Systems Design Europe,2006:14-18.

[16]D Bortis,G Ortiz,J W Kolar,et al.Design procedure for compact pulse transformers with rectangular pulse shape and fast rise times[J].IEEE Transactions on Dielectrics and Electrical Insulation,2011,18(4):1171-1180.

[17]同向前,宁大龙,夏伟,等.串联IGBT 的一种复合均压方法[J].电工技术学报,2012,27(3):153-158.Tong Xiangqian,Ning Dalong,Xia Wei,et al.A hybrid voltage-balancing method for igbts connected in series[J].Transactions of china electr otechnical society,2012,27(3):153-158.

[18]http://www.richieburnett.co.uk/temp/gdt/gdt2.html.

[19]Wang Daizhuang,Dai Haifeng,Sun Zechang.Design and simulation of gate driver circuit using pulse transformer[J].International Journal of Computer Science Issues,2013,10(2):305-310.