鱼雷光纤线导总线数据传输的FPGA实现方法

李子龙, 王 中, 高 卓, 朱云周, 朱建国

(1. 中国船舶重工集团公司 第705研究所, 陕西 西安, 710075; 2. 水下信息与控制重点实验室, 陕西 西安, 710075)

鱼雷光纤线导总线数据传输的FPGA实现方法

李子龙1,2,王中1,高卓1,2,朱云周1,朱建国1

(1. 中国船舶重工集团公司 第705研究所, 陕西 西安, 710075; 2. 水下信息与控制重点实验室, 陕西 西安, 710075)

根据光纤线导数据传输的特点, 提出了一种基于现场可编程门阵列(FPGA)实现鱼雷光纤线导总线数据传输的方法, 采用自定义的成帧格式与8B/10B编解码相结合的方式, 可以简化系统结构, 仅用单片FPGA就可实现, 具有组成简单、传输延迟低、传输可靠性高等优点。仿真结果表明, 在光纤数据的有效传输速率达到 100 Mb/s条件下, 误码率小于10-6, 该方法可实现光纤线导以太网总线数据的可靠传输。

鱼雷; 光纤线导; 以太网; 现场可编程门阵列

0 引言

光纤通信技术的发展为鱼雷的远程线导开辟了广阔前景, 是鱼雷线导技术的发展方向, 成为各国竞相发展的鱼雷专项技术, 并且不断地提高传输距离与信息的传输速率。而实现发控平台与鱼雷之间的信息融合处理, 增强鱼雷的远程导引和反对抗能力, 高速实时的光纤线导数据可靠传输是其核心技术[1]。

随着电子技术和计算机技术的不断发展, 各种先进处理算法和控制策略层出不穷, 总线技术在民用与军用技术领域中得到广泛应用, 特别是实时以太网技术, 以其接入方便、高成熟度和大通信容量得到了广泛选用。随着鱼雷信息化程度的提高, 以及水声对抗环境的日益复杂, 利用光纤线导技术实现雷艇信息的高速实时融合传输,提高鱼雷作战性能和对抗能力, 是各国鱼雷重点研究的方向。

总线技术是实现光纤线导数据高速可靠传输的有效技术途径。传统的线导遥控遥测信息量小、速率低, 数据传输处理主要采用数字信号处理(digital signal processing, DSP)器实现。但是随着光纤线导技术的应用, 线导系统的数据传输速率达到上百兆比特, 如果采用DSP进行数据处理,需要DSP具有极高的工作频率和强大的实时处理能力, 同时软件编程复杂, 相应的数据传输可靠性会显著下降。

目前在光纤通信领域数据处理大都采用现场可编程门阵列(field-programmable gate array, FPGA)实现, 相比于DSP芯片, FPGA规模大、集成度高、处理速度快, 能完成复杂的时序逻辑设计, 且编程灵活、方便简单, 适用于高速数据处理, 在性能、成本、灵活性和功耗等方面均具有优势[2]。因此, 采用FPGA技术实现光纤线导高速传输数据的组帧处理是其最适宜的实现途径。

文中提出了一种采用FPGA实现光纤线导数据传输的方法, 既能满足线导遥测遥控数据的高速可靠传输要求并可实现鱼雷与发射平台之间的数据融合, 又降低了光纤线导高速数据传输带来的数据处理难度, 且易于实现。

1 光纤线导数据通信方法

1.1光纤线导数据通信的特点

鱼雷光纤线导数据通信是采用1根大长度细径高强光纤把发射载体(水面舰艇、潜艇)和鱼雷连接起来, 将发射载体上的火控设备、鱼雷上的线导装置组成线导回路, 以完成发射载体、鱼雷之间的通信。光纤线导数据通信采用全双工模式,利用串行传输的方式将遥控遥测数据在鱼雷与发射载体之间进行传输。该系统主要由发射载体火控系统、发射载体数据收发模块、雷上数据收发模块及雷上信息处理系统四部分组成, 系统框图如图1所示。

图 1 光纤线导数据通信系统Fig. 1 Data transmission system of optical fiber wireguided communication

电磁导线线导鱼雷系统由于受信道的限制,只能传输少量的遥测遥控信息(如: 航深、偏航角、航速、目标方位角及目标距离等参数)[3], 其数据传输的特点是速率低, 传输协议简单。随着光纤线导技术的应用, 鱼雷和发射载体之间实现了高速数据传输, 传输速率是金属导线线导的105倍以上, 具备了鱼雷和发射载体之间高速信息融合的能力。光纤线导数据传输中既有传输速率较低的传统的遥控遥测信息, 也有雷上和艇上各种传感器的高速数据, 光纤线导通道也向着多用户数据传输方向发展。因此, 在雷艇信息融合的基础上, 在一定实时性、可靠性的保证下实现光纤线导高速数据融合传输, 是光纤线导技术的核心问题。

1.2光纤线导以太网总线数据传输的FPGA实现方法

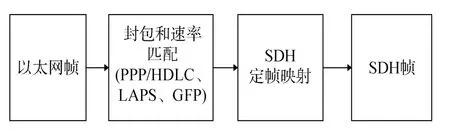

目前商业通信领域主导的技术分为2种: 用于内部网络通信的以太网技术和用于远距传输的SONET/SDH(synchronous digital hierarchy)光纤通信技术, 为节省成本, 提高现有网络的利用率, 商业通信主流的以太网光纤传输技术是Ethernet Over SONET/SDH[4], 该技术采用帧映射技术实现将以太网帧映射到SDH帧中, 从而实现突发不定长的以太网帧与要求严格同步的SDH帧之间速率匹配, 帧映射方式主要包括: PPP/HDLC(point to point protocol/high-level data link control)、LAPS(link access procedure-SDH)和GFP(generic framing procedure), 其示意图如图2所示。

图2 以太网帧映射主要方式Fig. 2 Main way of Ethernet frame mapping

Ethernet Over SONET/SDH将以太网的2层交换灵活性和资源优化能力与现有的 SDH光网络的大容量、高带宽效率和低协议开销相结合,从而得到一种高速、经济的数据接入解决方案。但是由于该技术是为了节省早期投资, 在现有光纤通信系统上进行适应的协议改造, 而不是完全为以太网光纤传输全新设计的技术, 因此存在协议复杂、开销较大、转发延迟较高等缺点。

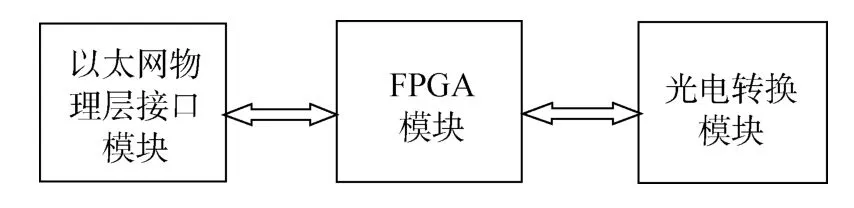

文中提出了一种简化的以太网光纤传输方法,采用自定义的成帧格式与8B/10B编解码相结合的方式, 可以简化系统结构, 仅用单片FPGA就可实现, 具有组成简单、传输延迟低、传输可靠性高等优点。光纤数据收发模块的硬件组成包括:以太网物理层接口芯片、FPGA模块和光电转换模块三部分, 模块组成如图3所示。

图3 数据收发模块Fig. 3 Module of data receiver-transceiver

FPGA模块通过MII(media independent interface)接口与外部以太网物理层接口芯片通信, 完成以太网数据收发的物理层功能。光电转换模块通过高速串行差分接口与FPGA模块通信, 主要完成电信号和光信号的相互转换。FPGA模块完成以太网数据的光纤传输处理, 实现高速的数据转发。

在鱼雷光纤线导遥控遥测数据传输中要求数据通信的延迟小、通信可靠度高。传统的基于通信处理器(DSP、CPU和ARM等)的光纤通信系统的灵活度高、协议复杂等优势难以体现, 而采用FPGA易于实现高速大容量数据传输, 降低硬件资源的使用, 简化软件编程, 提高传输可靠性。

针对光纤线导系统数据传输特点高低速率数据融合传输, 可以在FPGA设计中增加端口来实现, 将不同端口发送来的数据进行以太网数据封包后, 采用以太网总线方式进行传输。因此, 针对以太网数据在鱼雷光纤线导中的传输, 可采用FPGA实现以太网总线数据的收发处理。系统中的FPGA模块主要完成4位数据和8位数据的相互转换、MAC(medium access control)帧控制缓存、数据的组帧和恢复、编解码、时钟的恢复以及串并数据的转换。

FPGA模块对以太网数据的处理又分为发送端和接收端两部分, 当需要发送数据时FPGA模块将以太网物理层接口输入的以太网数据进行一系列处理后, 将数据送至光电转换模块进行电/光转换, 进而通过光纤将数据发送。而当需要接收数据时, 首先光电转换模块将光纤发送过来的数据进行光/电转换, 然后FPGA模块将光电转换模块送来的电信号经过处理后送至以太网物理层接口。

2 数据收发的FPGA模块设计

2.1发送端设计

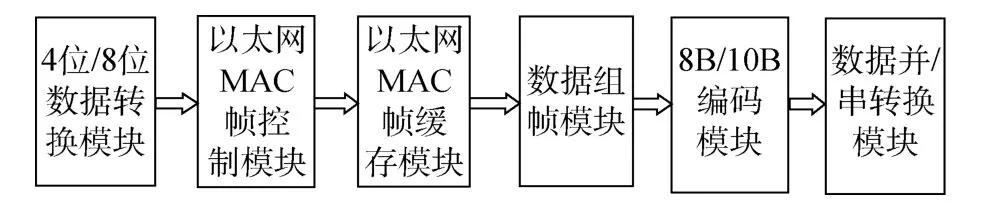

FPGA模块中的发送端部分由4位/8位数据转换模块、以太网MAC帧控制模块、以太网MAC帧缓存模块、数据组帧模块、8B/10B编码模块、数据并/串转换模块组成, 其构成如图4所示。

图4 FPGA模块数据发送端Fig. 4 Transceiver of FPGA module data

图中, 4位/8位数据转换模块完成数据位的转换, 而以太网MAC帧控制模块可以由以太网IP核实现, 以太网MAC帧缓存模块即是以太网MAC帧缓存FIFO。数据组帧模块负责将要发送的数据添加由特殊字符组成的帧头标识(K29.7)和帧尾标识(K28.7+K23.7), 当没有数据指令发送时要不断发送特殊字符和指定数据构成的空闲帧标识(K30.7+D15.2), 以保证帧发送的连续性。其逻辑流程图如图5所示。

图5 组帧模块逻辑流程图Fig. 5 Logic flow chart of framing module

在8 B/10 B编码中, 共有12种特殊字符编码分别为: K28.0~K28.7以及K23.7, K27.7, K29.7, K30.7。其中, 特殊字符K29.7即为8 B数据111_11101, 在8 B/10 B编码中将8位数据分成高3位和低5位分别编码, 低5位对应的十进制数即为29, 高3位对应的十进制数为7, 如果是特殊字符编码则表示成K29.7, 如果是一般数据编码则表示成D29.7, 而二者对应的10 B编码值是不一样的。同样K28.7, K23.7, K30.7也是如此, 而D15.2则为一般的数据字符。这样就保证了在解码时根据编码值的不同区分出帧头帧尾标识和空闲帧。

为保证光纤传输, 发送数据必须保证“0”和“1”的均衡, 一般通过信道编解码来实现。大多数高速串行标准都采用8 B/10 B或者64 B/65 B编码方案, 而64 B/65 B编码方案由于开销较小,在10 G以上高速以太网协议中常用[5]。8 B/10 B编解码具备一定的检错能力, 当发现重要的控制数据存在误码时, 可以进行重发, 从而保证遥控遥测数据传输的可靠性, 且逻辑编程处理相对简单。因此在该设计中, 编码模块采用8 B/10 B的编码方法, 数据并/串转换模块负责将10位编码后的并行数据转换为串行数据。

2.2接收端数据处理设计

FPGA模块的接收端部分主要由数据时钟恢复模块、串/并转换模块、10 B/8 B解码模块、数据帧恢复模块、以太网MAC帧缓存模块、以太网MAC帧控制模块、8位/4位数据转换模块7部分构成。数据时钟恢复模块将光/电转换后的串行数据恢复出数据和时钟, 并将恢复出的数据进行串/并转换, 转换后的10位数据经10 B/8 B解码模块恢复为8位数据, 再由数据帧恢复模块去除帧头和帧尾标识, 进而经以太网MAC帧缓存模块对数据进行缓存, 再经以太网MAC帧控制模块, 最后将数据经过8位/4位数据转换模块将8位数据转换为4位数据送至以太网MII接口模块, 框图如图6所示。

事实上, 由图4可知接收过程就是发送过程的逆过程, 接收端只需要按照发射过程一步步反向处理即可恢复以太网数据。但想要实现数据同步接收, 数据和时钟的恢复是关键, 所以数据时钟恢复模块是接收端的关键部分。

图6 FPGA模块数据接收端Fig. 6 Receiver of FPGA module data

2.3数据时钟恢复功能设计

数据时钟恢复部分为数据接收端的重要组成部分, 由于光纤信道传送的是数据和时钟组成的单一信号, 所以在数据接收端进行数据后续处理之前必须要把信号进行处理以恢复数据时钟。该设计采用了基于时间的过采样的方法, 通过边沿检测电路、倍频电路和时钟恢复电路即可对时钟进行提取[6], 具体原理如图7所示。

图7 时钟恢复原理Fig. 7 Principle of clock recovery

如图7所示, 倍频电路产生8倍频的作为采样时钟以及时钟生成电路的驱动时钟, 边沿检测电路的输出信号作为时钟生成电路计数器的复位信号。而边沿检测电路则采用了2个D触发器串联, 高频采样时钟作为2个触发器的触发时钟,而后输入信号和第2个触发器的输出信号相与非作为时钟生成电路的计数器复位信号, 电路框图如图8所示。

图8 同步边沿检测电路Fig. 8 Circuit of synchronous edge detection

在FPGA内部, 外部输入时钟经过DCM(digital clock manager)时钟管理模块倍频后, 生成高频时钟提供给边沿检测模块和同步时钟生成模块。边沿检测模块检测输入数据的跳变沿, 并将检测结果送同步时钟生成模块。同步时钟生成模块对输入高频时钟进行计数, 在输入数据边沿处(由边沿检测模块提供)开始计数, 到达指定计数后反转输出, 即为恢复的同步时钟。在同步时钟下, 对输入数据进行重采样, 输出即为恢复的同步数据。

3 FPGA模块的仿真与试验验证

对于FPGA模块的仿真验证, 主要是对代码的功能进行验证, 以便后面进行板级测试。通过功能仿真不仅可以验证代码功能, 还能对代码进行进一步优化。而对于该设计, 根据现有的硬件平台及硬件描述语言Verilog HDL, 基于Xilinx-ISE软件完成了相应的代码的编写, 并利用modelsim仿真软件对FPGA模块主要子模块进行了功能仿真测试。

3.1FPGA模块发送端modelsim仿真

在对FPGA模块的发送端进行仿真时, 要验证的是数据的转换、组帧及编解码等功能。仿真时首先编写一组数据由发送端将以太网数据报文发送,经一系列处理后, 检查数据输出端的输出值, 即可验证发送端的功能正确与否。对应仿真图见图9。

图9 发送端仿真Fig. 9 Simulation of transceiver

图中, data_4b为MII接口4位以太网数据, data_8b为转化后的数据, data_10b为8B/10B编码后的数据, data_out为编码后并转串输出数据。

3.2数据时钟恢复modelsim仿真

对于数据时钟恢复电路, 倍频电路输入时钟的频率与发送的时钟频率相同, 产生的8倍频时钟作为采样时钟以及时钟生成电路的驱动时钟,其仿真图如图10所示。

图中, cdr_datain为光电转换后的数据信号,而cdr_dataout为恢复出的数据, cdr_clockout为提取的系统时钟。其中倍频电路利用FPGA内部的锁相环以及DCM时钟管理模块实现, 且边沿检测电路的输出脉冲作为时钟生成电路计数器的复位信号。后续的解码等操作均利用提取的时钟作为驱动时钟。

3.3FPGA模块接收端modelsim仿真

对于FPGA模块的数据接收端的仿真, 在验证了发送端功能正确之后, 为了简化仿真过程,直接将发送端的输出串行数据作为接收端的输入信号。其对应的仿真图如图11所示。

图11 接收端仿真Fig. 11 Simulation of receiver

图中, data_in为提取的串行数据, data_10b为串/并转换后的10位数据, 当然这个过程需要对帧头进行定位。而data_out_8b为10B/8B解码后输出的8位并行数据, data_out_4b为8位转4位后输出的数据。通过对比发送和接收的数据可知接收端可以将发射端发送的数据完整恢复, 从而验证了功能的实现。

3.4试验验证

该设计在基于Xilinx的Spartan 3A DSP系列的XC3SD3400A的硬件平台上进行了模拟光纤线导数据传输的测试试验。按照图12所示的方法进行光纤线导数据传输可靠性测试, 其中光纤信道模拟器模拟光纤线导传输信道, 使得试验测试与光纤线导实际数据传输效果接近。

图中, 各验证平台均为实际的光纤线导数据收发模块, 光纤信道模拟器模拟实际光纤信道的衰减, 保证了测试的环境更接近于实际的线导鱼雷。测试试验结果表明, 在光纤数据的有效传输速率达到100 Mb/s条件下, 误码率小于10–6, 该FPGA以太网光纤总线数据传输方案可行, 且具有较高的传输可靠性。

图12 光纤线导信道模拟示意图Fig. 12 Schematic of channel simulation for optical fiber wire-guided communication

4 结束语

文中设计针对光纤线导中的数据通信, 利用FPGA数据处理技术实现光纤线导高速数据传输,经过了功能仿真和模拟系统数据传输试验测试,验证了该方法能够实现以太网总线数据在光纤线导系统中的可靠传输, 且具有扩展和提升传输速率的灵活性, 具有应用推广价值。

[1] 刘雪辰, 胡鹏, 赵岩. 鱼雷光纤线导光传输技术研究[J].鱼雷技术, 2013, 21(2): 37-38.

Liu Xue-chen, Hu Peng, Zhao Yan. An Optical Transmission Technique for Fiber Wire-guided Torpedo[J]. Torpedo Technology, 2013, 21(2): 37-38.

[2] 杨海钢, 孙嘉斌, 王慰. FPGA器件设计技术发展综述[J]. 电子与信息学报, 2010, 32(3): 714-715.

Yang Hai-gang, Sun Jia-bin, Wang Wei. An Overview to FPGA Device Design Technologies[J]. Journal of Electronics & Information Technology, 2010, 32(3): 714-715.

[3] 魏玉华, 王凯帅. 线导鱼导引方法的组合使用策略研究[J]. 鱼雷技术, 2014, 22(3): 210-211.

Wei Yu-hua, Wang Kai-shuai. Combination Strategy of Guidance Methods for Wire-guided Torpedo[J]. Torpedo Technology, 2014, 22(3): 210-211.

[4] 刘方楠, 孙力军, 白瑶晨. EoS的原理及其关键技术[J].通信技术, 2007, 7(40): 19-21.

[5] 陈曦, 邱志成, 张鹏, 等. 基于Verilog HDL的通信系统设计[M]. 北京: 中国水利水电出版社, 2009.

[6] 苏红. 利用FPGA内部DLL实现数字时钟恢复[J]. 科学技术与工程, 2007, 18(7): 4721-4722.

(责任编辑: 杨力军)

A FPGA Implementation Method of Data Transmission through Optical Fiber Bus for Wire-Guided Torpedo

LI Zi-long1,2,WANG Zhong1,GAO Zhuo1,2,ZHU Yun-zhou1,ZHU Jian-guo1

(1. The 705 Research Institute, China Shipbuilding Industry Corporation, Xi′an 710075, China; 2. Science and Technology on Underwater Information and Control Laboratory, Xi′an 710075, China)

According to the characteristics of optical fiber data transmission, this paper proposes a data transmission method through the optical fiber bus of a wire-guided torpedo based on field-programmable gate array(FPGA).The method combines the custom framing format with the 8B/10B coding and decoding, and can be achieved only by a single FPGA. It simplifies the system structure, and has the advantages such as simple composition, small transmission delay and high transmission reliability. Simulation result shows that the bit error rate is less than 10-6as the effective optical fiber transmission rate is 100 Mb/s. This method can realize reliable data transmission through Ethernet bus for optical fiber wire-guided communication.

torpedo; optical fiber wire-guided; Ethernet; field-programmable gate array(FPGA)

TJ631.4

A

1673-1948(2015)06-0433-06

10.11993/j.issn.1673-1948.2015.06.008

2015-07-15;

2015-10-12.

李子龙(1989-), 男, 在读硕士, 主要研究领域为线导鱼雷制导技术.