QFN封装元件组装及质量控制工艺

史建卫

(中兴通讯股份有限公司,广东深圳518057)

近几年来,由于QFN(方形扁平无引脚)封装具有良好的电热性能、体积小且质量轻,其应用正在快速增长。采用微型引线框架(Micro Lead Frame)的QFN 封装和CSP(Chip Size Package)封装有些相似,但元件底部没有焊球,与PCB 的电气和机械连接是通过PCB 焊盘上印刷焊膏,经过回流焊形成的焊点来实现的。QFN 封装对工艺提出了新的要求,本文将系统的对其组装及质量控制工艺进行探讨。

1 QFN 封装器件特点

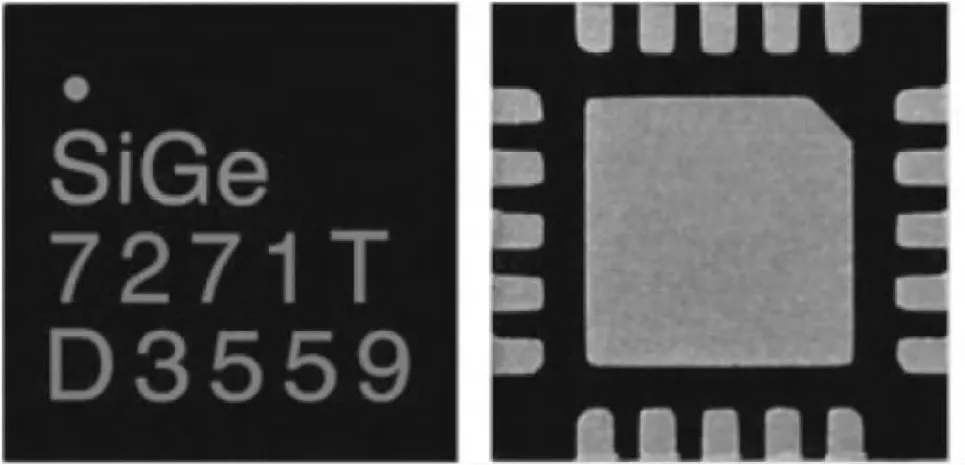

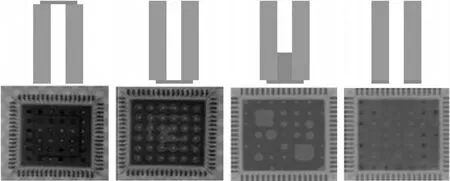

QFN 封装是一种无引脚封装,呈正方形或矩形,封装底部具有与底面水平的焊盘,在中央有一个面积焊盘裸露用来导热,围绕大焊盘的封装外围有实现电气连接的导电焊盘,如图1所示。

图1 QFN 封装元件上下平面图

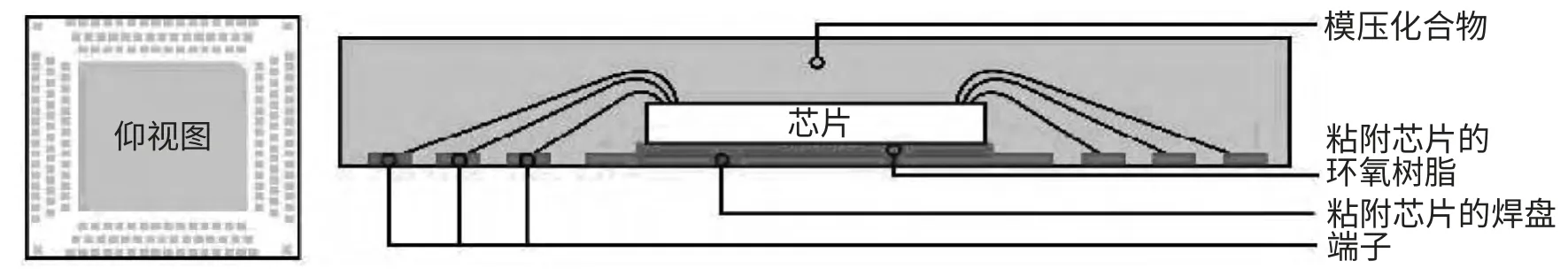

从结构看,QFN 封装不像传统的SOIC 与TSOP 封装那样具有鸥翼型引线,内部引脚与焊盘之间的导电路径短(如图2所示),自感系数以及封装体内布线电阻很低,所以能提供卓越的电性能。此外,通过外露的引线框架焊盘提供了出色的散热性能,该焊盘具有直接散热通道,用于释放封装内的热量。所以,QFN 封装特别适合任何一个对尺寸、质量和性能都有要求的应用。

QFN 封装常见尺寸有3 mm×3 mm、4 mm×4 mm、5 mm×5 mm 及6 mm×6 mm,常见引脚间距有0.65 mm、0.5 mm 和0.4 mm。与传统的28引脚PLCC 封装相比,32 引脚QFN 封装的面积(5 mm×5 mm)缩小了84%,厚度(0.9 mm)降低了80%,质量(0.06 g)减轻了95%,电子封装寄生效应降低了50%,所以非常适合应用在手机、数码相机、PDA 及其他便携电子设备的高密度PCB 上。

图2 QFN 封装内外部结构示意图

2 QFN 封装器件组装工艺

2.1 PCB 焊盘设计

QFN 封装焊盘设计主要包含以下三方面:周边引脚的焊盘设计、中间热焊盘及过孔设计和对PCB 阻焊层结构的考虑。

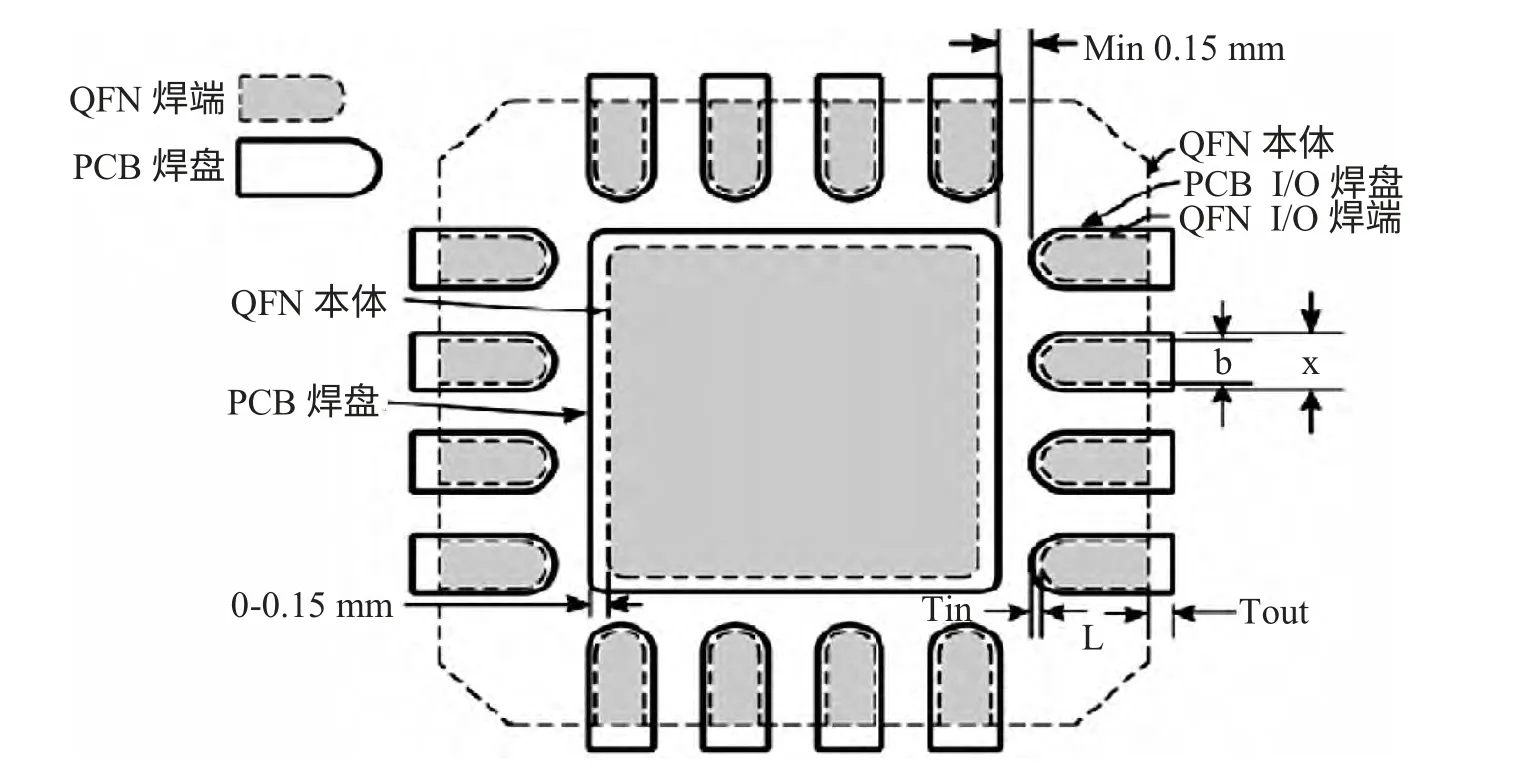

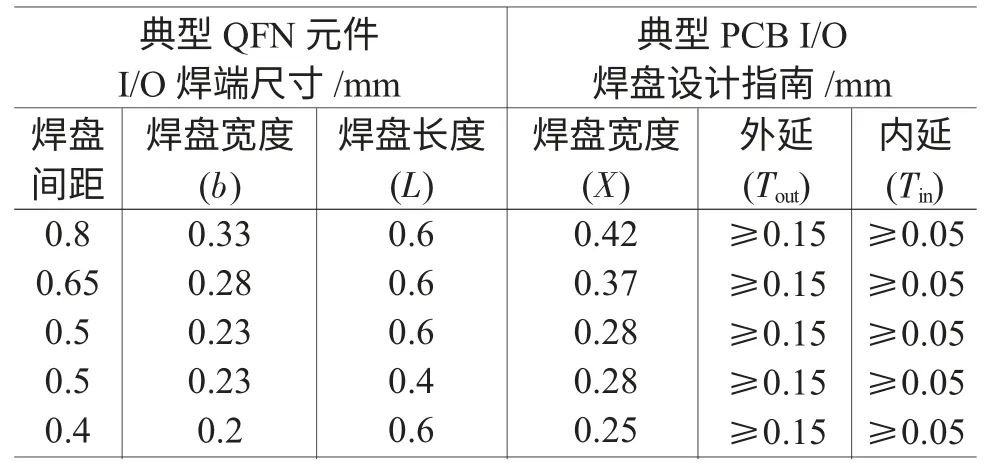

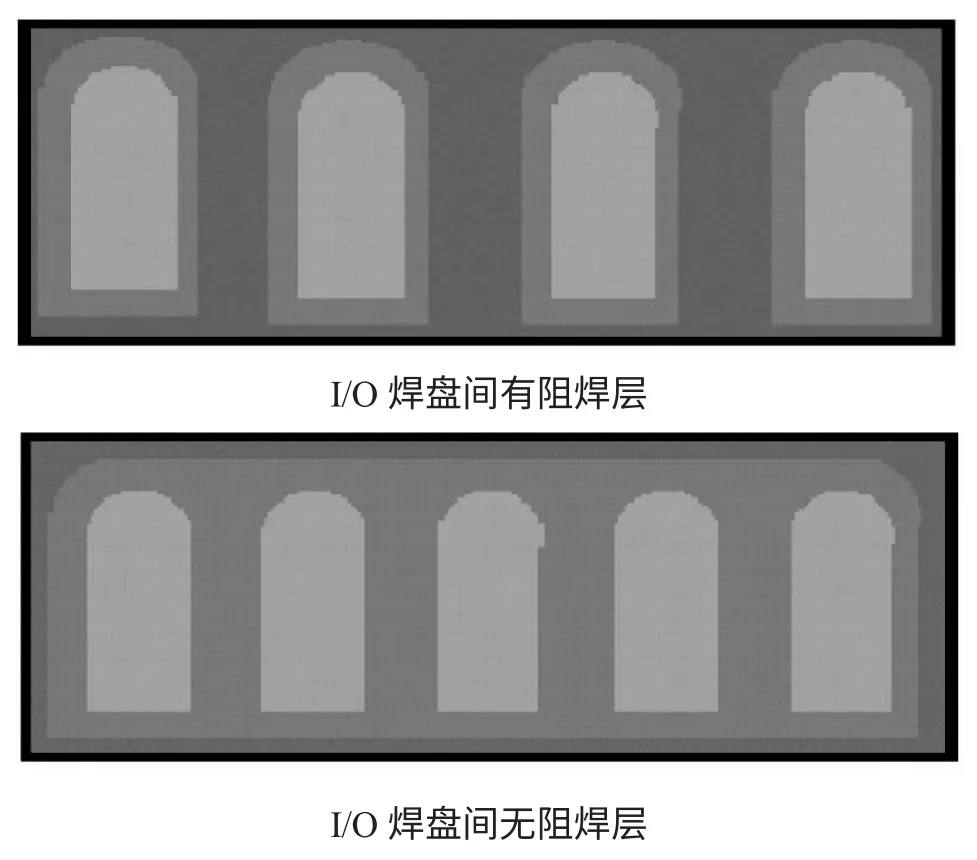

2.1.1 周边I/O 引脚焊盘设计

PCB I/O 引脚焊盘的设计应该比QFN I/O 焊端稍大一点,焊盘宽度范围一般在0.25~0.5 mm,焊盘长度范围一般在0.6~0.96 mm,焊盘内侧应设计成圆形以配合焊端的形状,具体设计如图3和表1所示。如果PCB 有设计空间,I/O 焊盘的外延长度>0.15 mm 可明显改善外侧焊点成型,提高焊点可靠性,不干涉时可外延0.3~0.5 mm(手工焊时建议延长0.5~1.0 mm);如果内延长度>0.05 mm,则必须考虑与中央散热焊盘之间保留至少0.25 mm的间隙以免引起桥连。

图3 QFN 封装PCB 引脚焊盘设计

表1 QFN I/O 引脚焊盘设计尺寸

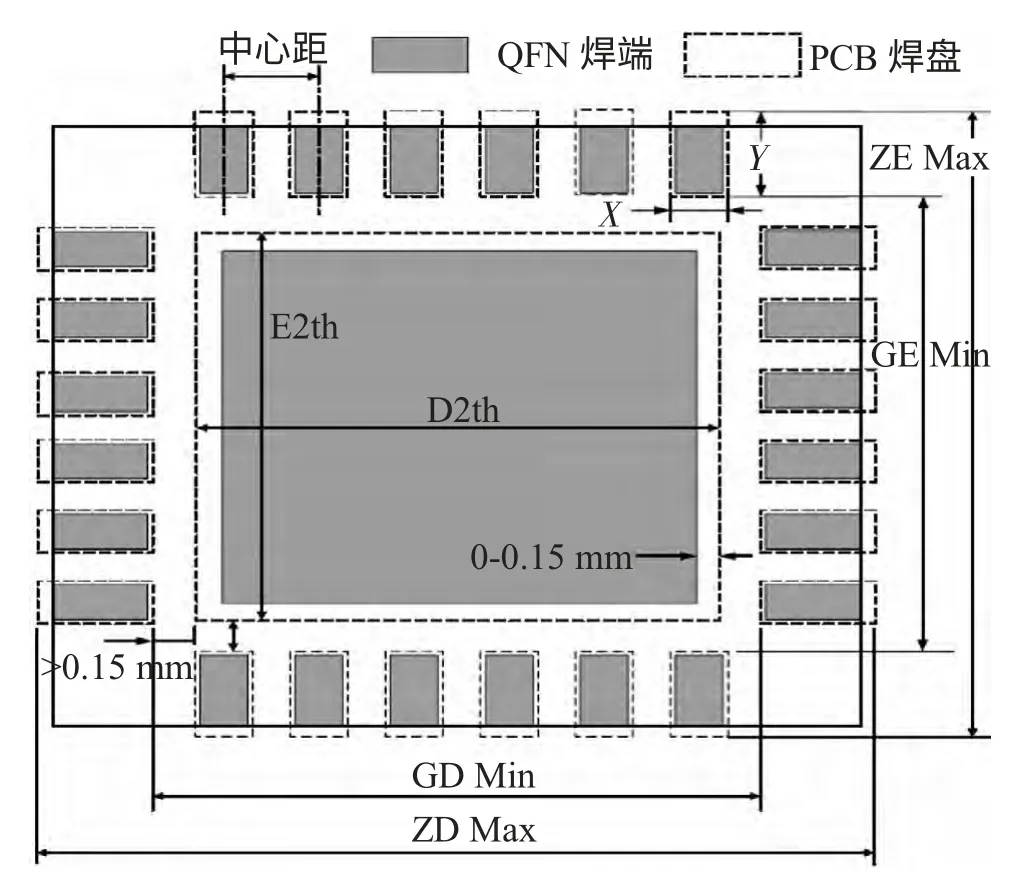

有时PCB I/O 引脚焊盘可采用与QFN I/O 封装引脚一样的设计,其设计尺寸可参考图4和表2所示。图中尺寸Zmax为焊盘引脚外侧最大尺寸,Gmin为焊盘引脚内侧最小尺寸,D2t 为散热焊盘尺寸,X、Y 是焊盘的宽度和长度。

图4 QFN 封装焊盘设计要求

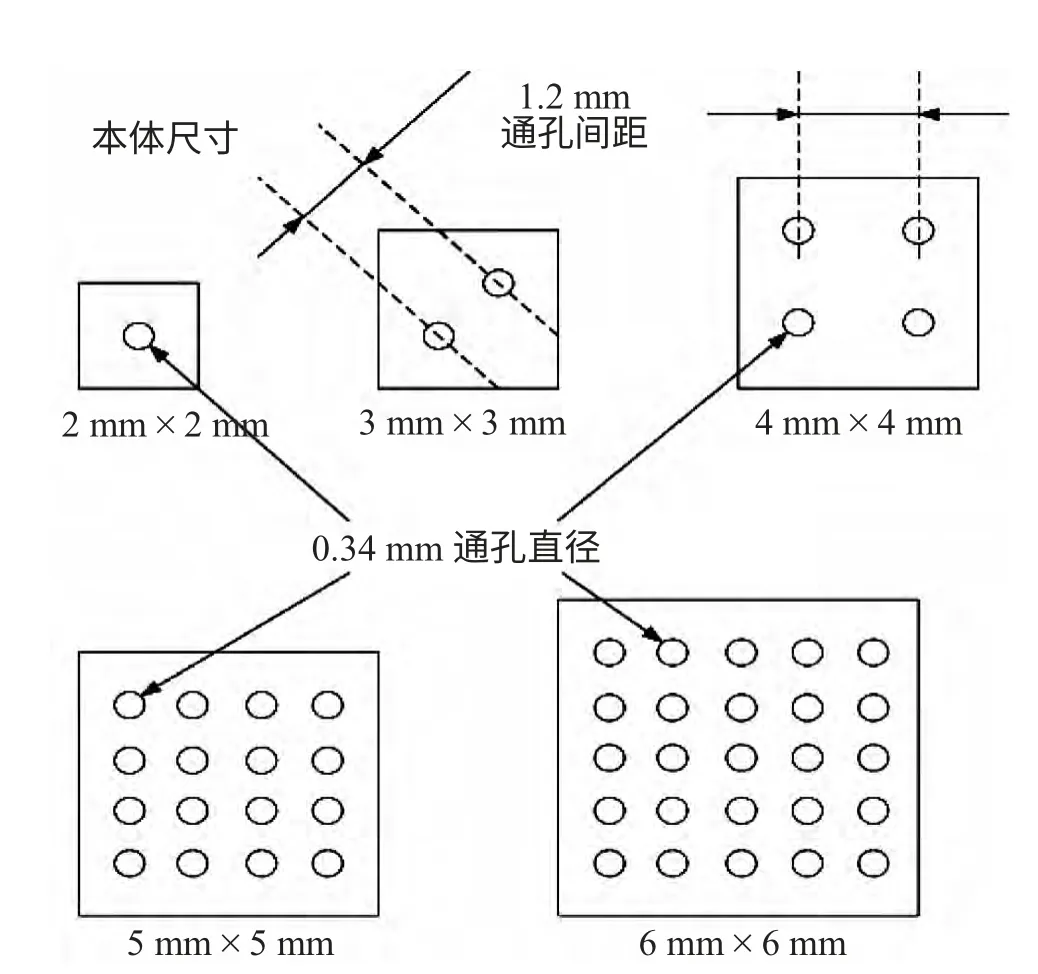

表2 QFN 封装典型PCB 焊盘设计尺寸

2.1.2 中央散热焊盘和散热过孔设计

QFN 封装具有优异的热性能,主要是因为封装底部有大面积的散热焊盘,为了能有效地将热量从芯片传导到PCB,PCB 底部必须设计与之相对应的散热焊盘和散热过孔。通常散热焊盘的尺寸至少和QFN 封装暴露的热焊盘相匹配,然而还需考虑各种其他因素,如避免和周边焊盘的桥接等,所以热焊盘尺寸需要修订,具体尺寸如上图4及表2所示。中央散热焊盘应设计比QFN 焊端各边大0~0.15 mm,即总长大出0~0.3 mm。但中央散热焊盘不能过大,否则会影响与I/O 引脚焊盘间的合理间隙,桥连增加。此间隙最小为0.15 mm,可能的话最好是0.25 mm 或更大。

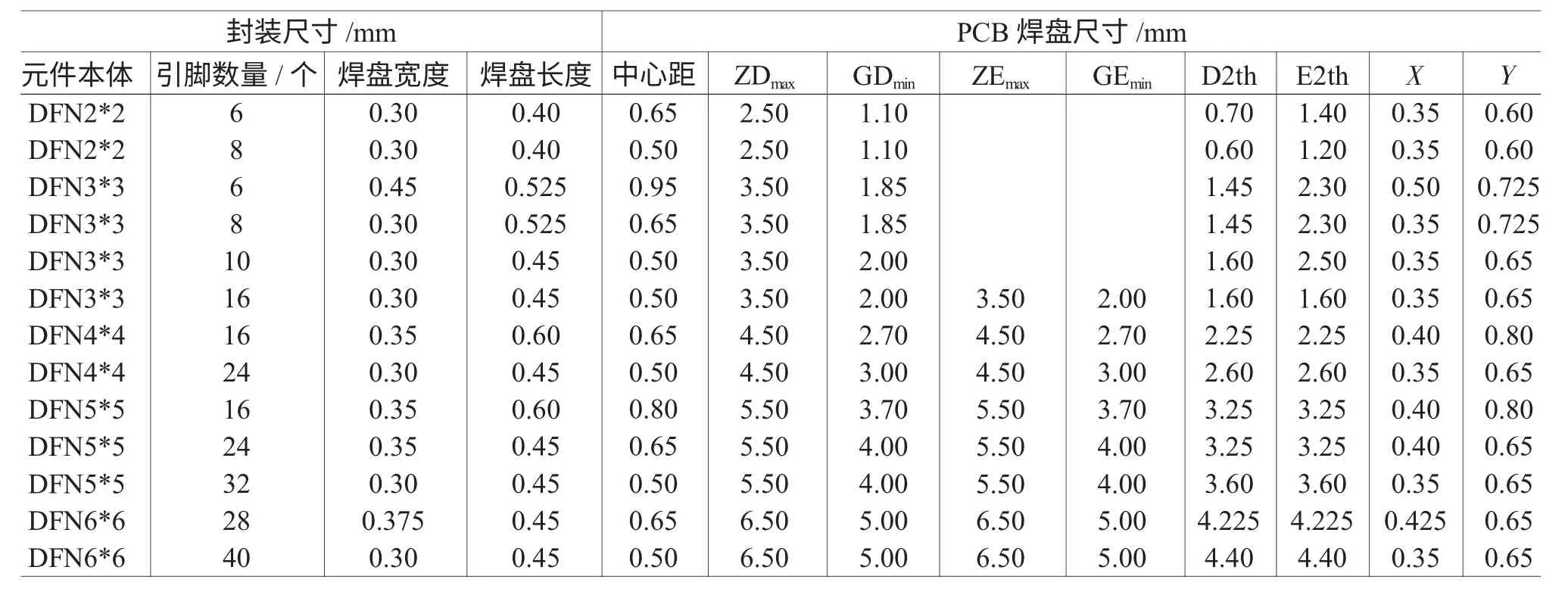

QFN 器件组装时,通常将散热焊盘直接焊接在PCB 上,PCB 中的散热过孔有助于将多余的热量扩散到接地铜板中。散热过孔的数量及尺寸取决于封装的应用情况、芯片功率大小,以及电性能的要求。一般建议开孔面积率在40%~60%,散热过孔间距1.0~1.2 mm,过孔孔径尺寸0.3~0.34 mm,如图5所示。虽然增加过孔(减小过孔间隙)表面上好像可以改善热性能,但因为增加过孔的同时也增加了热气进入的通道,所以实际情况需要根据PCB情况来决定(如散热焊盘尺寸及接地层)。散热过孔有4 种设计形式:使用干膜阻焊膜在过孔顶部或底部阻焊;使用液态感光阻焊膜从底部填充;采用“贯通孔”(如图6所示)。

图5 QFN 封装中央散热焊盘过孔设计要求

上述方法各有利弊:从顶部阻焊有利于控制气孔的产生,但会阻碍焊膏印刷;底边阻焊和底部填充由于气体的外逸会产生大的气孔,当覆盖2 个过孔时,对热性能方面有不利的影响;“贯通孔”允许焊料流进过孔,减小了气孔的尺寸,但QFN 封装底部散热焊盘上焊料会减少。散热过孔设计要根据具体情况而定,建议使用顶部阻焊或贯通孔。若采用底部阻焊后,容易形成气孔,若不会影响热性能、电性能和焊点可靠性,也是可以接受的。

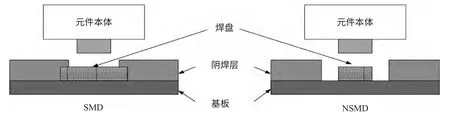

2.1.3 阻焊层的结构

目前阻焊层设计类型有SMD 和NSMD 两类,如图7所示,在尺寸相对较大的中央散热焊盘阻焊层设计中,一般采用SMD 工艺,否则建议使用NSMD 阻焊层,阻焊层开口应比焊盘开口大0.12~0.15 mm,即焊盘铜箔到阻焊层的间隙有0.06~0.075 mm,这样就允许阻焊层有50~65 μm 制造公差。有时QFN 中央散热焊盘设计过大,为了防止连锡,也会采用SMD 阻焊膜工艺,且开口缩小0.1 mm,以增加散热焊盘与I/O 焊盘之间的阻焊面积。

每个PCB I/O 焊盘应单独设计阻焊层开口,这样可以有效防止相连焊盘间形成桥连,且热焊盘过孔阻焊层直径应该比过孔直径大0.1 mm。但当引脚间距小于0.5 mm 时,引脚之间的阻焊可以省略,而设计一个大的开口,如图8所以。

图6 QFN 封装中央散热盘过孔的4 种设计形式

图7 阻焊层设计工艺

图8 粗细间距阻焊层设计形式

2.2 焊膏印刷网板开孔设计

能否得到完美、可靠的焊点,印刷网板设计是关键的第一步。不锈钢网板更耐用且很少有变形,激光切割、孔壁电抛光有助于提高焊膏释放率。如果印刷设备限制了网板实际印刷质量,建议使用阶梯(Step-Down)网板。对于焊盘上焊膏体积的沉积,网板厚度、开口形状及几何图形的作用同样重要。设计网板时应考虑满足两种比率,即面积比和宽厚比,其值应分别大于0.66 和1.5。一般建议网板开口尺寸和PCB 焊盘尺寸比为1:1,这样可以让面积比和宽厚比目标比较容易达到。

2.2.1 周边引脚焊盘的网板设计

焊后焊点高度一般在50~75 μm,网板的厚度决定了印刷在PCB 上的焊膏量,太多的焊膏将会导致回流焊接时桥连。所以建议大间距如0.65 mm 的QFN 封装使用0.15 mm 厚度的网板;0.5 mm 的QFN 封装使用0.12 mm 厚度的网板;≤0.5 mm 间距的QFN 封装使用0.12 mm 厚度的网板,但热焊盘网板开口尺寸可适当缩减5%~10%,以减少焊接桥连的发生,焊端焊盘可缩减或保持,如图9所示。

图9 防连锡细间距网板开口设计

2.2.2 中间散热焊盘的网板设计

PCB 上热焊盘和四周焊盘的面积差巨大,使得过回流焊后保持相同的焊锡高度非常困难。实验证明:0.13 mm 网板,面积比大于0.66 时,四周焊盘转印效率为73%,而热焊盘转印效率为100%。如果散热焊盘焊膏覆盖面积越大,越容易产生空洞、飞溅、锡球等缺陷,甚至发生QFN 元件浮起及导电焊盘四周焊端空焊。所以,必须通过减少热焊盘焊膏覆盖面积,使得过回流焊后热焊盘和四周焊盘的焊锡高度处在相同的水平。

针对热焊盘网板开口设计,建议采用多个呈“十”字分隔开的“小”网板开口代替单一的大网板开口,以确保一致的焊膏沉积,焊膏覆盖量的典型值为50%~80%,通常网板开成规则排列的小方型孔或圆孔,焊后连接面积一般大于40%,厚度介于50~65 μm 之间。值得注意的是,有底部填充过孔的焊膏印刷最好将过孔位于印刷边缘(如图10所示),有利于气体释放。“导通孔”被焊锡填充并不完全,往往只是让导通孔壁充分润湿直到底部塞紧(如图11所示)。

2.2.3 网板开口设计与QFN 封装焊接可靠性关系

QFN 封装焊接可靠性很大程度上受到焊点离板高度、焊点焊锡量、PCB 焊盘尺寸和热焊盘设计的影响,其中焊点离板高度、焊点焊锡量的变化和网板开口有关。组装生产时,有必要通过实际生产优化调整工艺方法,达到QFN 封装的可靠焊接,必要时还须反馈到设计部门进行优化设计。

图10 中央散热盘底部填充孔焊膏印刷位置

图11 中央散热盘“导通孔”易导致焊锡填堵过孔

为了有助于提高产品可靠性,须保证达到离板高度50 μm 厚的焊接层。焊点离板高度与热焊盘上焊膏覆盖率有关和过孔类型有关:焊膏覆盖面积增大,离板高度就会增加;底部填充式过孔,由于过孔从反面被阻塞的缘故,焊锡会被阻止进入,而“贯通孔”方式很容易使熔融的焊锡流到孔内,降低焊点离板高度,如果控制不当可能会导致焊锡在背面渗出。一般地,对于底部填充过孔,焊膏覆盖率至少在50%以上,而对于“贯通孔”,覆盖率至少在75%以上。此外,“贯通孔”的数量和尺寸、焊接峰值温度也会影响到焊点的离板高度。

一个焊点具有合适的离板高度,但没有或仅有低的外部焊点,在实际应用过程中也是不可靠的。四周焊盘的外部焊点受PCB 焊盘尺寸、焊膏印刷量、离板高度等多种因素影响。如果网板开口是1:1,将会对外部焊点提供充足的焊锡量,前提条件是离板高度不能太高,因为可利用的焊锡量比较有限,如果热焊盘上焊膏覆盖面积增大,就会形成较高的离板高度,对焊点来说没有足够的焊锡来补充。相反地,如果离板高度太低,大的表面弯曲呈球状的外部焊点就会形成。

2.3 QFN 封装器件贴装工艺

贴片机的精度决定了QFN 封装元件的贴装精度和角度的调整,轻微的贴片偏移可以在过回流焊后自动纠偏,严重的偏移应该在回流焊前进行矫正,以免发展成短路缺陷,如图12所示。使用贴片机视觉系统调整QFN 的位置有两种方法:封装轮廓(视觉系统搜索封装的外形轮廓)和引脚识别(许多视觉系统可以直接搜索引脚的形状)。对QFN 来说,这两种方法都可以接受且各有利弊:封装轮廓识别起来比较快,但精度不够;焊盘识别比较准确,但要搜索多只引脚,多只引脚的图像数据由贴片机同时进行处理会较慢。在QFN 工艺优化期间,贴片不偏移是关键,以免同其它问题混在一起,不利于问题的分析和解决。

图12 QFN 封装元件贴装偏移

2.4 QFN 封装器件回流焊接工艺

QFN 封装元件对回流焊接工艺并无特殊的要求,和所有元器件一样,对各种类型的PCB 板在不同位置都要求回流温度符合规范,但每个元器件温度受周围焊盘、板上所处位置和组装密度的影响。实际的回流焊峰值温度、保温时间及升温斜率范围等都不可以超过所用焊膏的工艺要求。一般情况下,回流焊温度曲线可参考以下要求:

预热阶段温度曲线设定:爬升斜率一般在2~3 ℃/s,有铅温度在100~120 ℃时间约为60~90 s,无铅温度在130~140 ℃,时间约为100 s。

活化阶段温度曲线设定:有铅温度在120~150 ℃,时间约为90 s,无铅温度在140~170 ℃,时间约为90 s。

回流峰值温度设定:有铅一般为215~220 ℃,时间15~30 s,无铅一般为235~240 ℃,时间15~30 s。

冷却阶段温度曲线设定:焊点凝固之前一般控制在4~6 ℃/s,凝固后一般控制在2~3 ℃/s。

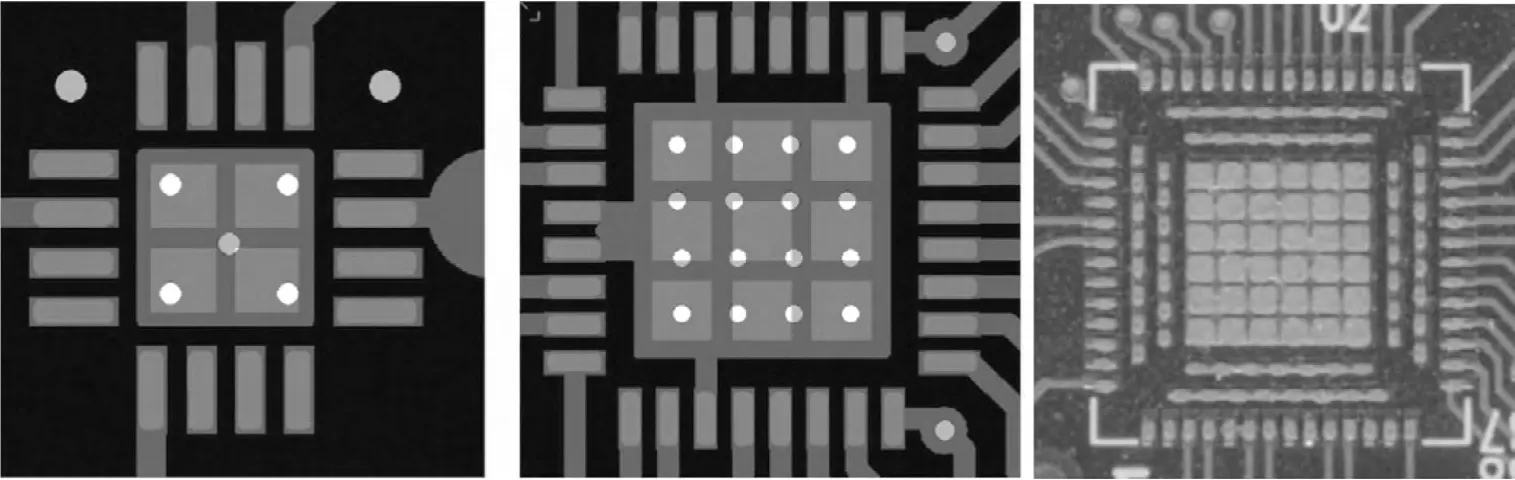

3 QFN 封装器件焊点缺陷及验收标准

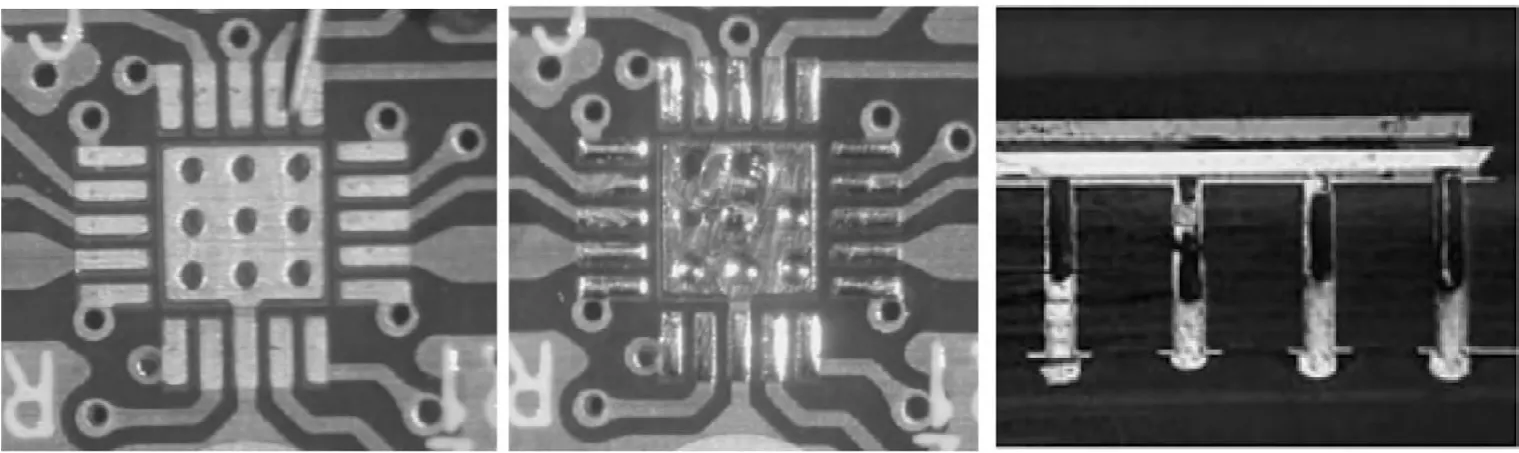

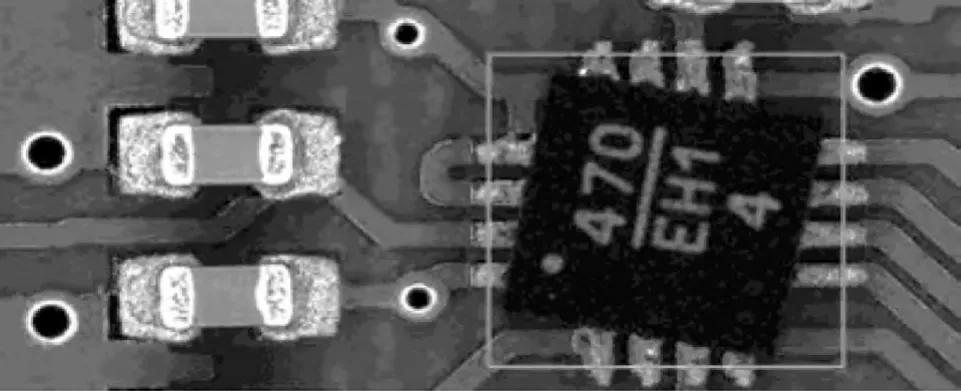

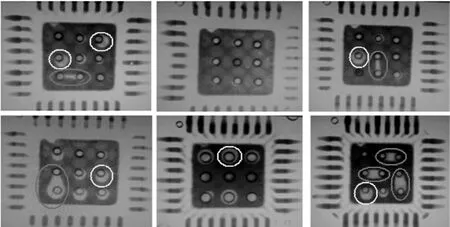

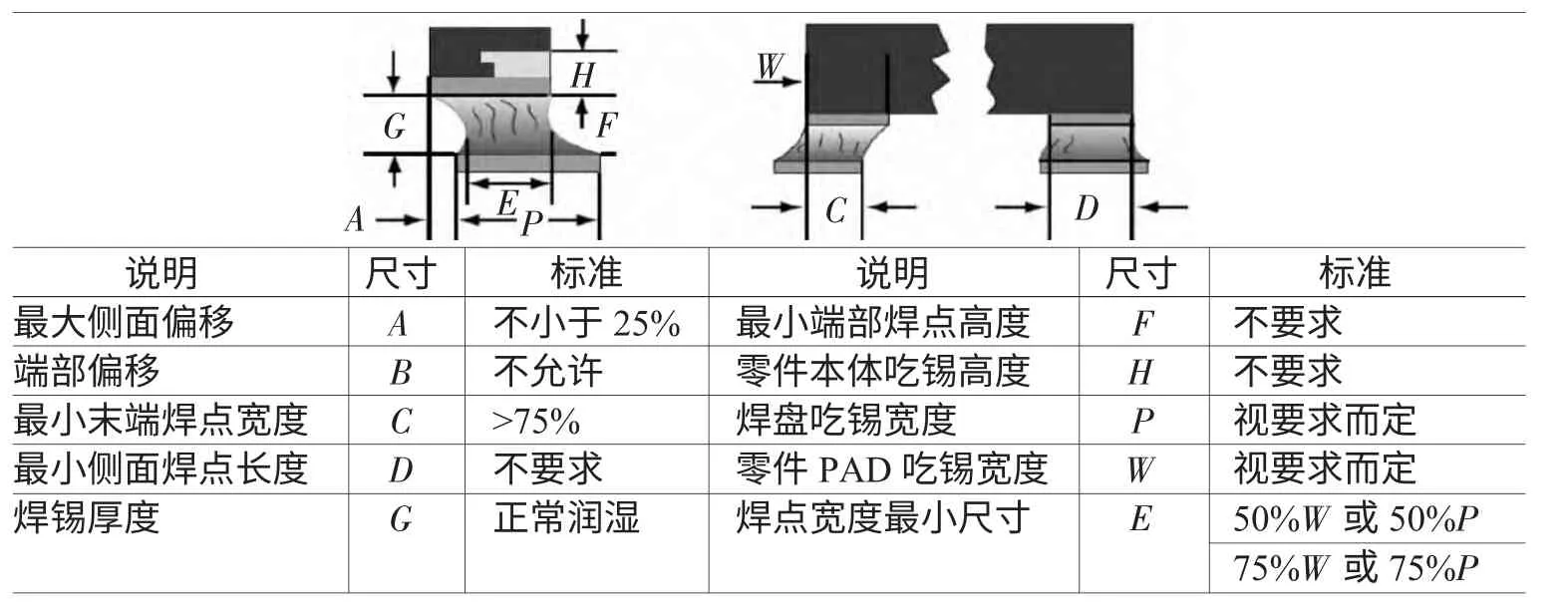

由于QFN 封装元件焊点在封装体的下方,X-ray 对焊点的桥连和空洞能检测出来,如图13所示,一般用于抽检;而对于虚焊、少锡和开路无法检测,只能通过外部焊点的情况进行判断。但焊点高度和填充部分到底是多少,在国标和电子行业标准中无具体标准可以参考,只能借助IPC/EIAJ-STD-001C 标准“电气和电子装配焊接要求”有关描述去判断,见表3。需要特别说明的是,针对QFN 封装元件,侧面焊点爬高无任何要求,只要求控制元件底面焊点的长度、宽度和厚度。

图13 X-ray 照射下底部填充过孔出现的空洞缺陷

表3 QFN 封装元件焊点判定标准

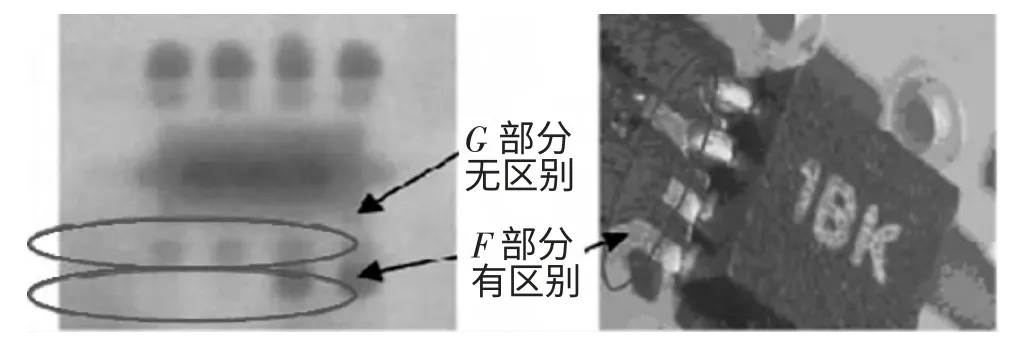

实际生产过程中,如果QFN 储存在不受控的环境中,其导电焊盘靠外的末端和侧面都可能会被氧化,形成虚焊,如图14所示。这是因为QFN仅导热焊盘和其在同一面的导电焊盘表面进行了可焊保护涂层,而导电焊盘靠外的末端和侧面则没有。如果氧化程度不严重,或助焊剂起到作用的话,也可能会形成良好的焊点。通过X-ray 图像可看出,图14中F 部分差别是明显的,但真正影响到焊点性能G 部分的图像则是相同的。虽然说QFN 封装元件焊点F 部分无具体要求,但在实际生产中发现,如果导电焊盘的外部焊点出现异常情况,那么在ICT 和FT 检测时出现的开路会较多。为了提高焊点可靠性及可检测性,实际生产中都要求能形成良好润湿的焊点,如图15所示。

图14 QFN 封装导电焊端外侧焊点虚焊缺陷

图15 QFN 封装导电焊端外侧形成良好润湿焊点

QFN 封装元件更多出现的是开路和少锡缺陷。依靠目视检查很难发现这些缺陷,甚至连X-Ray 也无法做出判断,这是因为QFN 焊点是在元件本体下方,且高度有限。在暂时没有更多办法的情况下,更多地依靠ICT/FT 测试来判断焊接的效果,或依靠目检焊点的外部F 部分情况来判断。

4 QFN 封装器件返修工艺

QFN 器件通过传统的电烙铁补焊返工,只对外露部分焊点有效,如果QFN 底部焊点存在桥接、开路、锡球等缺陷,就只能将元件拆除后返工。尽管QFN 封装元件很小,但拆除和返工都是可以手工完成的,这是一项具有挑战性的工作,因为QFN 元件本身体积很小,又通常被贴装在轻、薄且高密度PCB 上。

QFN 器件返修所需的工具和材料主要包括:

●带ESD 保护的返修焊台,温度可调且支持温度值425 ℃;

●ESD 垫板或桌面及ESD 碗带,保证两者都要接地;

●直径0.5 mm 焊锡丝及助焊剂;

●吸锡带、尖头镊子、防护镜及至少4×的放大镜;

●用于清洗电路板的异丙醇及小硬毛刷(毛长6 mm 为佳)。

4.1 QFN 器件返修前烘烤

返工之前,需要将PCBA 在125 ℃烘烤至少24 h,以除去PCB 和元件的潮气。

4.2 QFN 器件拆除

元件拆除时,温度曲线最好与装配元件时的回流焊温度曲线一致,但是焊锡液相线以上的温度和时间可以适当减少,只要能保证完成焊锡熔化即可。推荐在PCBA 底面用热风对流方式加热,预热温度达150 ℃,PCBA 顶部用热风喷嘴对元件本体加热,热风温度一般设定为425 ℃。

为慎重起见,可以先用吸锡带将元件周边可见焊点的焊锡清除。热风开启以后将喷嘴下降到离元件15~25 mm 的位置。当回流温度达到以后,可应用边缘加热系统向元件底部缝隙中吹热气,有利于面积较大的中央散热焊点的熔化。加热的同时,可在QFN 器件的角上插入尖头镊子,轻轻用力往上挑,一旦所有焊点的焊锡都熔化时,元件就可以被挑起。因为QFN 器件很小很轻,所以要严密注意控制加热时间,避免QFN 器件过度受热损坏,同时也应注意避免对周边元件的受热影响。一旦元件全部回流完成,用真空吸嘴或镊子将元件移除,真空压力不宜高于半个大气压,以防在元件未充分回流而过早吸取元件时损坏PCB 焊盘。

4.3 QFN 器件PCB 焊盘焊膏印刷

焊锡膏印刷在大约50~100 倍的显微镜下,使用特制的小钢网和刮刀进行焊膏印刷,小刮刀宽度应与元件宽度一致,以保证一次印刷成功。

4.4 QFN 器件重新贴装和回流焊接

由于QFN 器件重量很轻,在回流焊过程中的自对中能力很强,所以对贴装精度要求不是很高。用于贴装的返工台应该可以进行平移和旋转方向精细调整,并借助50~100 倍的光学成像系统,帮助进行器件对准。贴装完成后,使用与初次生产时同样的温度曲线重新进行回流焊接。

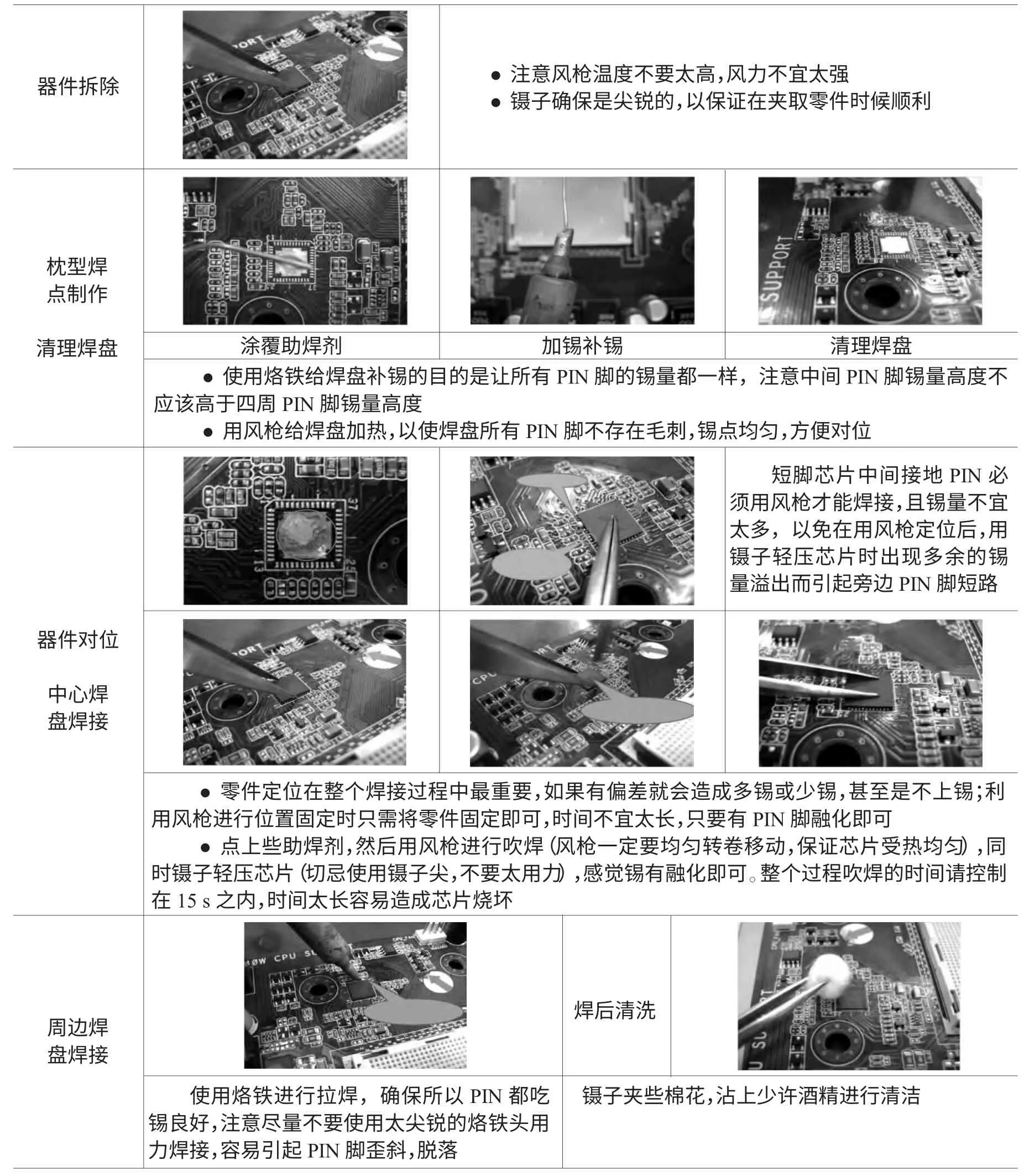

如果PCBA 元件密集度太高而无法使用特别小钢网印刷焊锡膏,就只能选择手工焊接进行返工,烙铁尖要细,顶部的宽度不能大于1 mm。具体工艺步骤见表4所述。

表4 QFN 封装器件手工返修工艺

(1)QFN 器件中央裸焊盘上锡。烙铁头温度设置为370 ℃,涂布适量液体助焊剂,将事先已贮满焊锡的烙铁头轻轻地接触中央裸焊端,或直接用烙铁头施加焊锡丝,保持数秒,焊锡开始润湿焊盘,形成一个漂亮的中间最高四边略低的“枕形”焊点。

清除助焊剂残渣后,测量元枕形焊点高度,控制在0.1~0.35 mm。如果枕形焊点高度太高,可以重新涂布助焊剂,将枕形焊点熔化后,用吸锡带吸走部分焊锡,以降低枕形焊点的高度。枕形焊点制作完成后,需清理元件周边I/O 焊盘上的焊锡残渣和助焊剂残渣。

(2)QFN 器件手工贴装。重新在元件的枕形焊点上涂布适量新鲜助焊剂,并借助显微镜尽可能精确地手工贴装到PCB 上,且根据第1 脚的位置确定元件方向。由于枕形焊点的存在,元件贴在PCB 上后会摇晃,所以手上动作要特别小心。

(3)QFN 器件热焊盘手工焊接。用镊子轻轻压住器件,通过喷嘴吹出热风加热元件顶部,直到枕形焊点熔化。当枕形焊点熔化时,会感觉到元件有轻微的下沉。移走热风喷嘴待冷却后,元件已被固定在PCB 上。清理助焊剂残渣,并检查元件顶面是否水平,以及元件I/O 焊端与PCB 上的I/O焊盘是否对准。如不准,可重新涂布助焊剂,将枕形焊点重新加热熔化后,用镊子轻轻拨动调整。

(4)QFN 器件周边焊盘手工焊接。涂布新鲜助焊剂到元件周边I/O 焊盘和PCB 上的I/O 焊盘,用尖头烙铁逐个点焊,注意避免引起桥连。完成焊接后,用溶剂清洗除去器件和PCB 上的助焊剂残渣,获得完美的返工效果。

5 结 论

QFN器件由于其特有的优越性能,已在电子产品中被广泛的推广和应用,但其微型引线框架无引脚封装特点,对传统组装工艺带来了很大的挑战,尤其是PCB 焊盘设计与焊膏印刷网板开孔设计方面,这就需要设计工程师从源头抓起,慎重选型,仔细研究封装焊盘尺寸、PCB 焊盘尺寸及过孔特征,从设计方面提高产品可制造性,其次在组装过程中,严格控制焊膏印刷、元件贴装、回流焊接工艺,提高产品一次成品率。另外,还需熟练掌握专用返修台及手工返修工艺,实现不良品的高品质处理,降低制造成本。

[1]郑雪辉,王万平.QFN 焊盘设计和工艺[C].2013 中国高端SMT 学术会议论文集:193-198.2013,中国·重庆.

[2]年晓玲.QFN 焊盘设计与工艺组装[J].电子质量,2010(5):39-41.

[3]汪继凡,叶裕明,吴正旺.QFN 板级焊点可靠性研究[A].2011 中国高端SMT 学术会议论文集[C].636-643.2011,中国·南京。

[4]IPC-SM-782 表面安装设计和焊盘设计标准[S].