4 500 V碳化硅SBD和JFET功率模块的制备与测试

何骏伟 陈思哲 任 娜 柏 松 陶永洪 刘 奥 盛 况

(1.浙江大学电气工程学院 杭州 310027 2.南京电子器件研究所 南京 210016)

4 500 V碳化硅SBD和JFET功率模块的制备与测试

何骏伟1陈思哲1任 娜1柏 松2陶永洪2刘 奥2盛 况1

(1.浙江大学电气工程学院 杭州 310027 2.南京电子器件研究所 南京 210016)

基于自主研制的碳化硅肖特基势垒二极管(SBD)和碳化硅结型场效应晶体管(JFET)芯片,成功制备了4 500 V/150 A的碳化硅SBD功率模块和4 500 V/50 A的碳化硅JFET功率模块,并设计了JFET功率模块的驱动电路进行相应的静态和动态开关测试。测试结果表明,制备模块具备了相应的电流导通和电压阻断能力,同时开关特性良好,模块的容量是目前国内已报道的最高水平。

碳化硅 肖特基势垒二极管 结型场效应晶体管 功率模块

0 引言

碳化硅(SiC)是一种宽禁带半导体材料,具有高击穿电场强度(10倍于硅材料)以及低本征载流子浓度(常温下为硅材料的10-20)等特点[1]。一方面,高击穿电场强度意味着碳化硅电力电子器件可拥有比硅基器件更优越的耐压特性和更小的导通阻抗。另一方面,低本征载流子浓度使得碳化硅器件具有最高可达600℃的理论结温,为器件的高温应用提供了基础。此外,碳化硅材料具有的高饱和迁移速度和低介电系数也为器件带来了良好的高频特性[2]。因此,碳化硅器件在高电压、大容量、高温、高频率的应用中具有广泛前景[3-5]。

作为最早商业化的宽禁带功率器件,碳化硅肖特基二极管(Schottky Barrier Diode,SBD)已在高频电路中得到了广泛应用。肖特基二极管的单极性工作状态可大大减少器件的反向恢复电流,被认为是理想的二极管器件[6]。随着材料和工艺的不断进步,碳化硅二极管的耐压等级不断提高。目前,实验室阶段的碳化硅PiN型二极管阻断电压可达到19.5 kV,在电流密度为100 A/cm2时,其正向压降仅为6.5 V[7]。国内也已有4 500 V的碳化硅二极管的报道[8]。

对于碳化硅开关管器件,目前的主流技术包括碳化硅金属氧化物半导体场效应晶体管(Metal Oxide Semiconductor Filed Effect Transistor,MOSFET)以及结型场效应晶体管(Junction Field Effect Transistor,JFET)等。虽然碳化硅MOSFET得到了更广泛的关注,但其门极可靠性问题始终未得到很好的解决,特别是在高压器件中,上述问题更为严峻。因此,对于高压碳化硅器件,碳化硅JFET器件结构更为可靠,同时也易于制备。

然而,由于单极型器件阻断电压与导通电阻的制约关系以及晶圆材料的缺陷带来的芯片面积上的限制,碳化硅SBD和JFET器件的单芯片电流导通能力随电压等级提升而急剧减小。为了实现高压大容量应用,需要将多芯片并联组成碳化硅功率模块进行使用。目前,国际上对1 200 V等级的碳化硅JFET功率模块已开展了一定研究[9,10],但对高压碳化硅JFET功率模块的报道较少。

本文采用自主研制的碳化硅SBD和JFET芯片进行并联,成功制备出4 500 V/150 A的碳化硅SBD功率模块和4 500 V/50 A的碳化硅JFET功率模块,并对其进行了静态和动态测试。测试结果表明,制备的模块具有稳定的电流导通和电压阻断能力,动态开关特性良好。

1 芯片的设计与制备

功率模块的基础是相应高压功率器件芯片的制备。本文中,开关器件为碳化硅JFET,二极管器件为碳化硅SBD。为了实现超过4 500 V的电压阻断能力,SBD和JFET器件均使用外延厚度50 μm以上的4H-SiC材料。

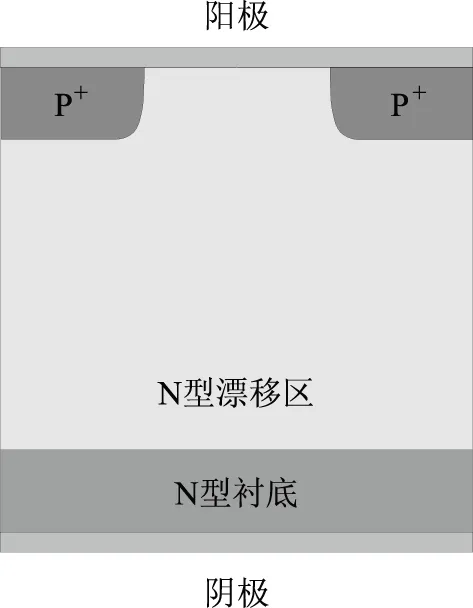

1.1 碳化硅SBD器件

在器件结构上,碳化硅SBD采用了结型肖特基势垒 (Junction Barrier Schottky,JBS) 二极管结构进行器件制备,其结构如图1所示。JBS二极管结构结合了肖特基二极管低导通压降的正向特性和类似PiN二极管的低漏电流的阻断特性,因而得到了广泛应用。

图1 碳化硅JBS二极管结构示意图Fig.1 Schematic cross section view of SiC JBS

碳化硅JBS二极管的关键工艺在于表面离子注入区宽度和间距的调控。在器件制备中,首先通过光刻和等离子体刻蚀等技术进行注入掩膜的图形化,然后进行多次铝离子注入,从而在器件表面形成P型重掺杂区。此外,这些注入的离子需要进行高温退火工艺以实现激活。完成高温退火后,对芯片进行表面钝化保护,并在芯片背面沉积金属并退火以形成欧姆接触,在芯片正面沉积金属形成肖特基接触,最后镀上电极金属。

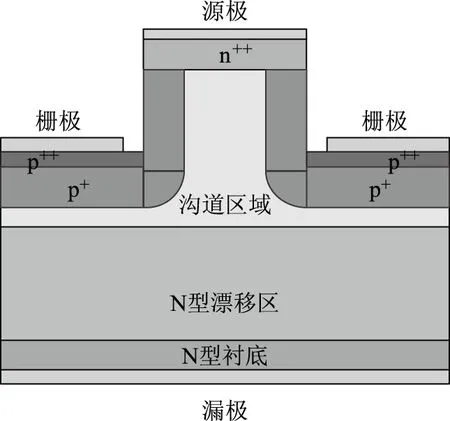

1.2 碳化硅JFET器件

相比于碳化硅SBD器件,碳化硅JFET的制备步骤较为复杂。在器件制备中,本文采用了沟槽-注入型结型场效应晶体管(Trenched-and-Implanted JFET,TI-JFET)结构[11],如图2所示。由于器件的沟道是通过半导体刻蚀形成的,不需要二次外延生长以及苛刻的光刻对准条件,TI-JFET器件结构具有高电流密度和易于制备的特点,得到了广泛使用。同时,通过调整沟道宽度等关键尺寸,可对器件的导通特性和阻断能力进行调整,便于器件特性优化。

图2 碳化硅JFET结构示意图Fig.2 Schematic cross section view of SiC JFET

TI-JFET器件制备的核心是使用等离子体刻蚀技术形成一系列沟槽结构,并通过离子注入的方式形成P型离子注入区,以形成器件沟道。完成离子注入和相应的退火激活工艺后,使用热氧化及化学气相沉积技术在碳化硅表面生成二氧化硅(SiO2)等钝化层结构,对器件表面进行保护。器件的电极由含有镍(Ni)的金属堆叠结构构成,并通过高温退火工艺形成良好的接触。之后,使用钝化材料对沟槽间的空隙进行填充,并在器件正面和背面沉积厚金属,以便于大电流的导通,完成器件制备。

关于4 500 V碳化硅SBD和JFET芯片设计、工艺以及优化等方面更详细的内容将另行撰文。

2 模块的设计与制备

2.1 模块DBC设计

碳化硅SBD和JFET模块均采用108 mm×62 mm的标准基板设计直接覆铜陶瓷板(Direct Bonded Copper,DBC)。考虑到模块的电流电压等级,DBC上下两层的铜层厚度均为0.3 mm,中间氧化铝陶瓷厚度为0.63 mm,功率回路铜层最小宽度为4 mm,铜层间隙以及四周铜层留边均为2 mm,这样保证在4 500 V绝缘强度的前提下最大程度地减小模块热阻,DBC剖面如图3所示。SBD和JFET模块的DBC布局分别如图4和图5所示,其中SBD模块最多可并联28个芯片,而JFET模块最多并联22个芯片,以获得较高的电流等级。此外,对于JFET模块,左右两部分芯片的源极相互独立,采用模块外部并联的方式连接,方便在DBC板上进行逐级并联测试。

图3 DBC设计剖面示意图Fig.3 Cross section view of DBC layout

图4 碳化硅SBD模块28个芯片并联DBC设计图Fig.4 DBC layout of SiC SBD Module with 28 chips in parallel

图5 碳化硅JFET模块22个芯片并联DBC设计图Fig.5 DBC layout of SiC JFET Module with 22 chips in parallel

2.2 模块热阻分析

对于功率模块设计而言,寄生电感和结壳热阻(Junction-to-case Thermal Resistance,RJ-C)的优化至关重要。由于设计的碳化硅SBD模块和JFET模块电压为4 500 V,而电流分别只有150 A和50 A,属于高压小电流的应用范围,功率回路的寄生电感对模块在实际电力电子电路工作的影响较小,此外,由于并联芯片数目较多,而DBC的有效面积裕量较小,从寄生电感方面来考虑对DBC芯片布局的优化也十分有限,故以下着重进行模块结壳热阻的分析。

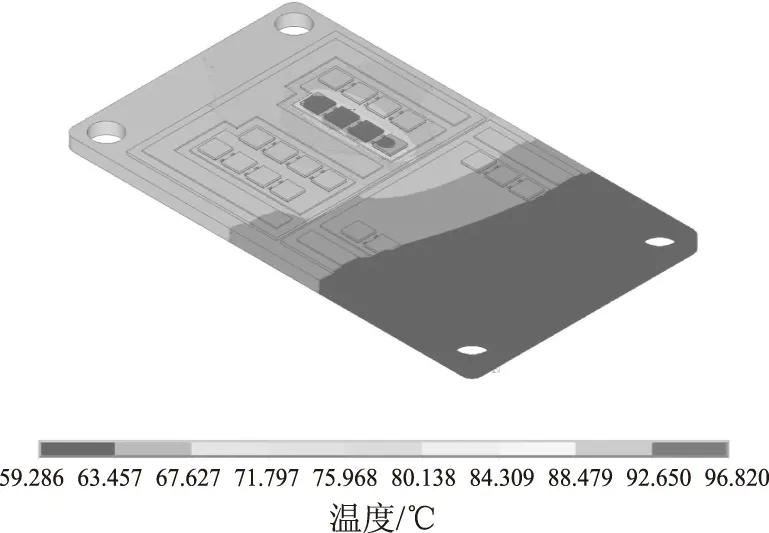

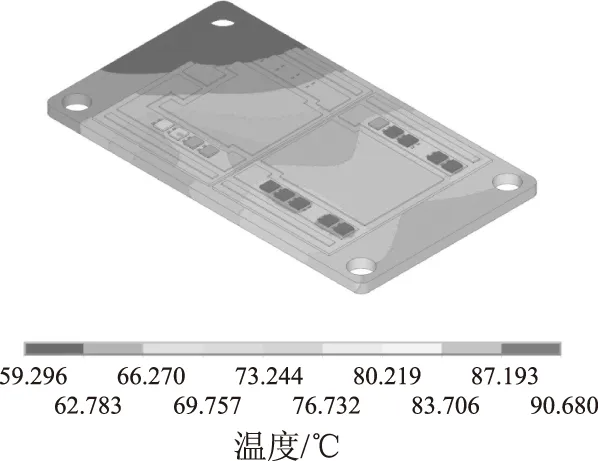

首先针对设计的SBD模块和JFET模块进行单芯片发热条件下的热学仿真,仿真平台为有限元分析软件ANSYS。仿真条件为室温下对模块进行风冷,根据单芯片正向特性的测试结果,仿真中SBD芯片和JFET芯片耗散功率分别设为19 W、12 W。仿真结果显示,单芯片情况下SBD模块和JFET模块芯片的最高温度分别为53.6℃、48.6℃,对应芯片中心处的铜基板温度分别为40.3℃、35.7℃,由此可计算得到SBD和JFET模块的结壳热阻RJ-C值分别约为0.70 K/W、1.1 K/W。

对于实验中制备的SBD模块和JFET模块,考虑到模块部分芯片排布较为密集,相邻芯片之间散热回路有一定重叠,因此,对SBD进行了4芯片ANSYS热仿真,仿真过程中保持单个芯片耗散功率不变。仿真结果如图6所示,此时模块单芯片结壳平均热阻约为0.79 K/W。

图6 碳化硅SBD模块ANSYS仿真热分布Fig.6 Thermal distribution of SiC SBD module in ANSYS simulation

对于JFET模块,由于JFET芯片源极的沟槽结构以及正面金属工艺的不完善性,芯片的键合成功率低于SBD模块,于是根据其中一个模块实际有效工作的14个芯片的分布进行了热仿真,仿真结果如图7所示,模块单芯片平均结壳热阻约为0.67 K/W,表明设计的模块具有良好的散热条件,芯片结温被有效控制,并未因多芯片的并联而受到显著影响。

图7 碳化硅JFET模块ANSYS仿真热分布Fig.7 Thermal distribution of SiC JFET module in ANSYS simulation

2.3 模块的制备

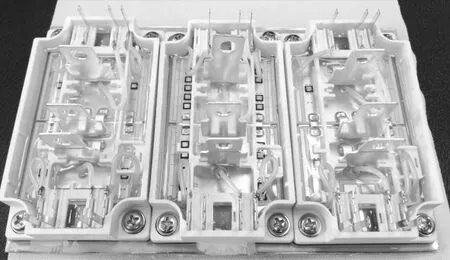

模块的制作包含两次焊接过程,其中芯片焊接的焊锡熔点为268℃,而基板支架的焊接选用的焊锡熔点为220℃,以确保基板和支架在第二次焊接过程中不会对芯片造成影响。芯片表面电极的引线采用超声波键合的方式进行,并使用5~12 mil的铝线,既保证了电流强度的需要,又减小了键合过程对芯片的机械冲击。最终制得SBD模块焊接了28个芯片,剔除一个键合强度不理想的芯片之后,最终为27个芯片并联,DBC照片以及封装完成后的模块分别如图8、图9所示。考虑到JFET芯片键合成功率的问题,最终将19个芯片分布在3个子模块上,然后再进行外部并联制得最终的JFET模块,其中中部的子模块有14个有效芯片,其分布如图7所示,左右两个子模块共有5个芯片。模块的部分DBC芯片键合情况及灌胶后的样品分别如图10、图11所示。

图8 碳化硅SBD模块内部DBC芯片键合图Fig.8 DBC substrate with SiC SBD chips bonded inside the power module

图9 碳化硅SBD模块实物图Fig.9 The picture of fabricated SiC SBD module

图10 碳化硅JFET模块内部DBC芯片键合图Fig.10 DBC substrate with SiC JFET chips bonded inside the power module

图11 碳化硅JFET模块最终实物图Fig.11 The picture of fabricated SiC JFET module

3 模块的静态测试

3.1 正向导通电流测试

在对模块完成灌胶之后,使用大功率晶体管图示仪(Tektronix 371A)对制备的模块在室温下进行正向导通特性的测试。测试回路为四线制的开尔文连接,以充分减小回路电阻的影响,并采用周期80 ms、宽度300 μs的漏源脉冲电压进行测试,ANSYS仿真表明,在此测试条件下,模块温升小于2℃。测试仪器的栅源信号在电压型驱动时为阶梯信号,而在电流型驱动时为脉冲信号,考虑到JFET模块栅源电流较大,测试中采取电流型驱动的测试方法。图12、图13分别为碳化硅SBD模块和JFET模块的正向特性测试结果。由图可看出,SBD模块在导通电流为100 A和150 A时,正向压降分别约为2.8 V、3.5 V,JFET模块在导通电流为50 A时,正向压降约为4.5 V。

图12 碳化硅SBD模块正向导通电流特性Fig.12 Forward characteristics of fabricated SiC SBD module

图13 碳化硅JFET模块在VGS为5~8 V栅极偏置下的正向电流导通特性Fig.13 Forward characteristics of fabricated SiC JFET module at various gate biases (VGS=5~8 V)

3.2 阻断电压测试

图14 碳化硅SBD模块反向阻断特性Fig.14 Reverse I-V characteristics of SiC SBD module

图15 碳化硅JFET模块阻断特性 (VGS=-18 V)Fig.15 Blocking characteristics of SiC JFET module (VGS=-18 V)

阻断测试过程中,高压源输出宽度为1 s的逐渐上升的阶梯电压信号,同时高精度数字万用表测得每个阻断电压下器件的漏电流并记录,采用的高压源和万用表的误差分别在5 V和0.05 μA以内,其中JFET模块在测试过程中栅源偏压VGS为-18 V。图14、图15 分别为SiC SBD模块和SiC JFET模块的阻断特性。测试结果表明SBD模块与JFET模块均实现了4 500 V的阻断能力,在偏置电压为4 500 V时,制备模块的漏电流分别为263 μA、72.8 μA。

需要说明的是,本文中碳化硅SBD与JFET模块均是使用实验室自主试制的芯片组成的,相比于商业化的1 200 V碳化硅器件,其阻断漏电流明显偏大。主要原因可能包括:碳化硅材料本身有一定缺陷且芯片面积较大;终端区场线环采用的30级设计对于4 500 V的器件来说裕量不够;芯片制备过程中采用的工艺不够完善,如离子注入会对碳化硅材料造成晶格损伤,从而影响器件的漏电流,这就要求探索出合适的加热方法和退火氛围,以实现低缺陷的退火工艺来降低这种损伤。由此可见,该批芯片的工艺和性能尚需进一步优化和提升。

4 模块的动态测试

4.1 驱动与测试电路

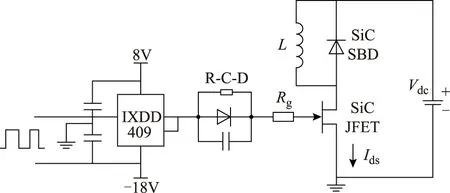

动态测试的驱动以及双脉冲测试电路如图16所示,开关管为自制的碳化硅JFET模块,续流二极管为自制的碳化硅SBD模块。驱动电路中采用了IXYS公司IXDD 409驱动芯片,芯片较高的驱动电流能力可满足19个芯片并联的JFET模块的驱动需求。根据静态测试的结果,驱动芯片在器件开通和关断时分别提供8 V和-18 V的栅极偏置。此外,驱动电路中采用的R-C-D网络可为JFET器件在提供足够驱动电流的同时提供保护,其中,电容C容值为100 nF,在开通过程中可保证足够的瞬态电流,电阻R为1 kΩ,保证了器件在关断时栅源二极管不会有过大的雪崩电流[12]。

图16 碳化硅JFET模块驱动及双脉冲测试电路Fig.16 Double-pulse test circuit with drive circuit for SiC JFET module

模块测试采用典型的感性负载双脉冲测试电路,驱动提供两个开通脉冲信号,第一个脉冲的作用是使流过器件的电流达到需要测试的值,在第一个脉冲的下降沿阶段得到JFET模块在母线电压及测试电流下的关断波形,器件关断后电感电流通过碳化硅二极管模块续流,在第二个脉冲的上升沿阶段器件开通,得到JFET模块的开通波形,同时二极管模块恢复阻断状态,且此时测得的开关管电流波形可较大程度上体现二极管反向恢复特性。

4.2 动态测试结果

在室温下采用上述驱动和测试电路,并在不同电压电流等级下对模块进行动态测试,其中在2 000 V/30 A的条件下,模块的开通波形如图17所示。

需要特别指出的是,作为试验性样品,考虑到由3个子模块外部并联组成的JFET模块的寄生电感特别是栅极的寄生电感较大,器件在快速开关时可能存在较大的误开通风险,故驱动电路采用较大的驱动电阻,减缓了器件的开关速度。尽管如此,由图17可看出模块的开通时间约为200 ns,相比于相同电压电流等级的硅基器件具有明显优势。当然,若想得到较好的关断特性,还需对门极驱动电路作进一步优化。另外,由图17的电流波形可看到模块开通时具有明显的电流过冲,这是由于开关管和二极管的电流等级不匹配造成的,且该过冲值不会随测试电流增加而明显变大。若开关管的电流容量能进一步提升,电流过冲问题将会得到缓解。

5 结论

本文介绍了基于自主研制芯片的高压大容量碳化硅SBD和JFET模块的设计、制备及测试工作。制备的模块阻断电压能力均达到4 500 V,其中,碳化硅SBD模块在正向压降3.5 V时,导通电流达到150 A,而碳化硅JFET模块在漏源电压4.5 V时,导通电流达到50 A,模块的电压电流等级均为国内领先水平。本文的工作为进一步研制高压大电流的碳化硅功率模块提供了一定的实践基础。

[1] 钱照明,张军明,吕征宇,等.我国电力电子与电力传动面临的挑战与机遇[J].电工技术学报,2004,19(8):10-22. Qian Zhaoming,Zhang Junming,Lv Zhengyu,et al.Challenge and opportunity for power electronics and electrical drive in China[J].Transactions of China Electrotechnical Society,2004,19(8):10-22.

[2] 钱照明,盛况.大功率半导体器件的发展与展望[J].大功率变流技术,2010(1):1-9. Qian Zhaoming,Sheng Kuang.Development and perspective of high power semiconductor device[J].Converter Technology & Electric Traction,2010(1):1-9.

[3] 徐殿国,李向荣.极限温度下的电力电子技术[J].电工技术学报,2006,21(3):15-23. Xu Dianguo,Li Xiangrong.Power electronics in extreme temperature applications[J].Transactions of China Electrotechnical society,2006,21(3):15-23.

[4] 盛况,郭清,张军明,等.碳化硅电力电子器件在电力系统的应用展望[J].中国电机工程学报,2012,32(30):1-7. Sheng Kuang,Guo Qing,Zhang Junming,et al.Development and prospect of SiC power devices in power grid[J].Proceedings of CSEE,2012,32(30):1-7.

[5] 王学梅.宽禁带碳化硅功率器件在电动汽车中的研究与应用[J].中国电机工程学报,2014,34(3):371-379. Wang Xuemei.Researches and applications of wide bandgap SiC power devices in electric vehicles[J].Proceedings of CSEE,2014,34(3):371-379.

[6] Alatise O,Adotei N,Allotey P,et al.The impact of parasitic inductance on the performance of silicon-carbide schottky barrier diodes[J].IEEE Transactions on Power Electronics,2012,27(8):3826-3833.

[7] Sugawara Y,Takayama D,Asano K,et al.12~19 kV 4H-SiC pin diodes with low power loss[C].Proceedings of the 13th International Symposium on Power Semiconductor Devices and ICs,Osaka,Japan,2001:27-30.

[8] 黄润华,李理,陶永洪,等.4 500 V碳化硅肖特基二极管研究[J].固体电子学研究与进展,2013,33(3):220-223. Huang Runhua,Li Li,Tao Yonghong,et al.Research of 4.5 kV SiC JBS diode[J].Research and Progress of SEE,2013,33(3):220-223.

[9] Peftitsis D,Baburske R,Rabkowski J,et al.Challenges regarding parallel connection of SiC JFETs[J].IEEE Transactions on Power Electronics,2013,28(3):1449-1463.

[10]Xu F,Jiang D,Wang J,et al.Development of a SiC JFET-Based six-pack power module for a fully integrated inverter[J].IEEE Transactions on Power Electronics,2013,28(3):1464-1477.

[11]Chen S,Sheng K.Design consideration and fabrication of 1.2 kV 4H-SiC trenched-and-implanted vertical junction field-effect transistors[J].China Physics B,2014,23(7):077201.

[12]Round S,Heldwein M,Kolar K,et al.A SiC JFET driver for a 5 kW,150 kHz three-phase PWM converter[C].Proceedings of IEEE Industry Applications Conference,Hong Kong,2005:410-416.

Fabrication and Testing of 4 500 V SiC SBD and JFET Power Modules

HeJunwei1ChenSizhe1RenNa1BaiSong2TaoYonghong2LiuAo2ShengKuang1

(1.College of Electrical Engineering Zhejiang University Hangzhou 310027 China 2.Nanjing Electronic Devices Institute Nanjing 210016 China)

Based on self-developed SiC devices,this paper presents the fabrication and characterization of a 4 500 V/150 A SiC Schottky barrier diode (SBD) power module and a 4 500 V/50 A junction field effect transistor (JFET) power module.Additionally,with an appropriate gate drive circuit,the static and dynamic performances of both modules are also evaluated.The testing results indicate good current-conducting,voltage-blocking,and switching capabilities of the fabricated modules.This work demonstrates the highest power level of SiC power modules with self-fabricated chips in China.

SiC,Schottky barrier diode,junction field effect transistor,power module

2014-12-22 改稿日期2015-06-20

TN30

何骏伟 男,1990年生,硕士研究生,研究方向为电力电子器件的封装与测试。(通信作者)

陈思哲 男,1988年生,博士研究生,研究方向为碳化硅电力电子器件。

中央高校基本科研业务费专项资金(2014FZA4014)和浙江省教育厅科研项目(Y201329864)资助。