基于FPGA的1553B 总线的接口设计

张惠宇宸,王晓曼,刘 鹏,仵宗钦,叶琳琳,张立媛

(长春理工大学a.电子信息工程学院;b.空地激光通信技术国防重点学科实验室,长春130022)

0 引 言

随着航空航天事业的发展,卫星的综合电子系统与单机设备之间的通信网络成为电子综合化最关键的基础设施。而卫星的高实时性和机动性对星载电子通信系统提出了更高的要求。基于1553B建立的电子通信系统具有高效性和可靠性,经常用于条件苛刻的通信系统。卫星采用1553B总线与星载通信载荷分系统、中心处理单元、综合管理单元、执行单元、驱动单元以及电源控制单元等进行通信。

随着半导体技术的发展,FPGA(Field Programmable Gate Array)的集成度越来越高且价格适中,所以笔者提出一种基于FPGA的MIL-STD-1553B(Military Standard 1553 Bus)数据总线接口卡的设计方案,包含MIL-STD-1553B总线的接口模块,不需要大量的外围电路,使用方便。

1 MIL-STD-1553B数据传输总线协议

MIL-STD-1553B数据传输总线的工作频率为1 Mbit/s[1]。数据以曼彻斯特双极性码的形式进行传输,以半双工的方式进行工作。总线上的硬件部分主要由总线控制器(BC:Bus Controller)、远程终端(RT:Remote Terminal)以及总线监控器(MT:Monitor)组成。

BC是总线上发起数据传输的唯一终端,即建立总线数据传输任务的终端[2]。

RT是总线上任务的执行终端,在总线控制器的控制下发送数据或接收数据[3]。

MT记录总线上的数据传输情况,但其本身不进行数据通信[4]。

1553B总线采用可屏蔽双绞线,以数字信号的形式进行数据传输。

1553B协议规定传输一个消息的完整过程应该包括命令字,数据字和状态字。每种字的字长为20位,有效位是16位,每种字的前3位为同步字头,而最后1位是奇偶校验位。由信息发送端对16位有效位进行补奇操作[5],而在信息接收端进行奇校验操作。有效位和奇偶位在总线上采用曼彻斯特码的形式进行传输,工作频率为1 MHz。同步字头为3位,先正后负时为命令字或状态字;先负后正时为数据字,正/负电平各占1.5 μs。1553B总线传输的字格式如图1所示。

图1 MIL-STD-1553B 3种字格式结构图Fig.1 Three word format of MIL-STD-1553B

1.1 命令字

命令字包含了与总线控制器通信的终端地址,数据传输方向,数据的来源以及连续传输的数据字个数[6]。

1.2 数据字与状态字

数据字可由总线控制器或某终端发送,其有效数据长度为16位[7]。状态字只能由终端发出,总线控制器可通过读取状态字了解终端的状态,从而决定下一步的动作。

命令字、数据字与状态字可通过信息来源进行判断。

1.3 MIL-STD-1553B的数据传输格式

在MIL-STD-1553B中有3种主要的数据传输格式(见图2)。

图2 3种主要的数据传输格式Fig.2 Three main data format

图2中@代表响应时间,#代表消息间隔时间,需大于4 μs。

2 系统的硬件设计

1553B的总线接口完成总线和子系统的信息交换。1553B总线接口的主要任务是实现数据的接收、发送和处理。

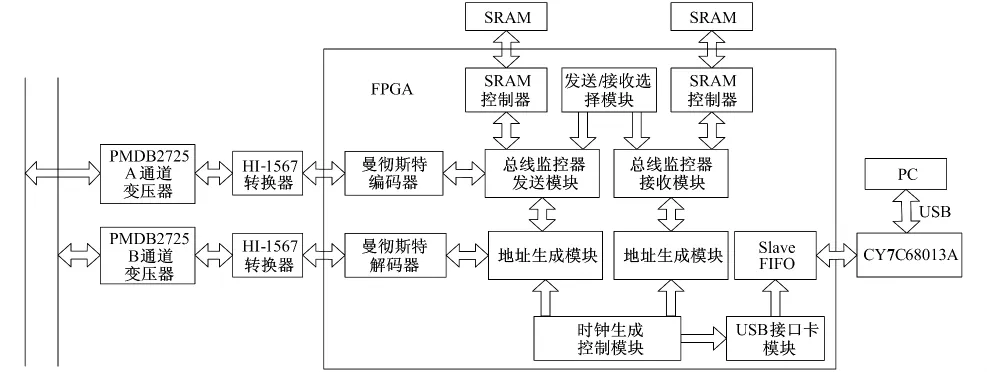

该系统的硬件核心是FPGA,系统结构如图3所示。在图3中,1553B数据总线的耦合方式采用变压器耦合方式,总线收发的信号需要经过电平转换器后进入FPGA中处理。在FPGA的内部,由曼彻斯特编解码器、SRAM(Static Random Access Memory)控制器、总线发送模块、总线接收模块、时钟生成模块和FIFO(First Input First Output)等组成1553B接口系统。

图3 系统结构图Fig.3 System structure

2.1 PMDB2725 变压器

转换器与总线之间的连接可采用变压器耦合或直接耦合。由于直接耦合不利于终端故障的隔离,一个终端的故障将导致整个总线系统的完全瘫痪,所以采用变压器耦合。理论上,变压器耦合使用短截线的长度不超过6 m。在总线与变压器之间需加一个隔离电阻,而隔离电阻与耦合变压器之间应以尽量短的短截线连接。

设计中采用PMDB2725变压器(见图4)。该变压器的较高匝数端在隔离电阻的一侧,具有连续的可提供最小覆盖(75%)的屏蔽。变压器的输入阻抗从FPGA方向看,其值大于3 000 Ω。

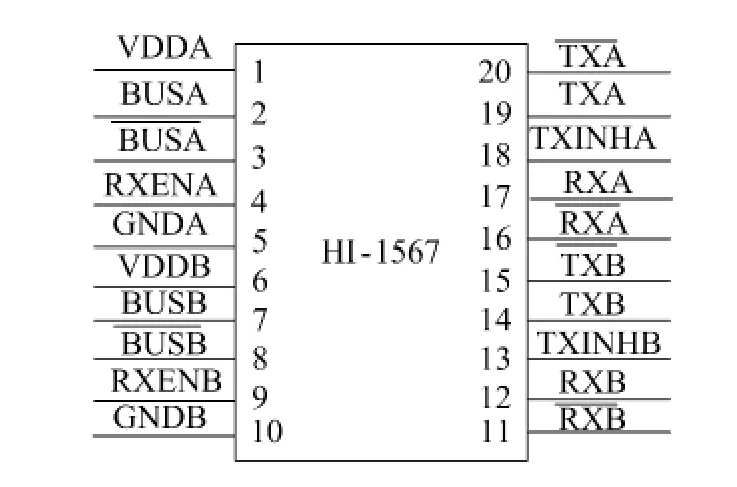

2.2 HI-1567 转换器

HOLT公司的HI-1567芯片是一种双通道模拟收发器。HI-1567供电电源为5 V的直流电源。其中RXA和RXA、RXB和RXB分别为两个接收器的正相和反相数字输出。TXA和RXA、TXB和RXB分别为两个发送器的正相和反相数字输入。其管脚图如图5所示。

图4 PMDB2725变压器Fig.4 PMDB2725 transformer

图5 HI-1567管脚图Fig.5 HI-1567 pin diagram

2.3 SRAM 控制器

SRAM是静态随机存储器,不需刷新电路就能保存其内部存储的数据,速度快,因此SRAM具有较高的性能[8]。设计中采用两个SRAM作为数据的缓存区。1553B的数据总线的工作频率为1 MHz,而FPGA的工作频率为50 MHz,为了解决工作频率不同的问题,增加了数据缓存区。为了保证两个SRAM能无遗漏地存储数据,采用乒乓操作的方法(见图6)进行数据缓存。乒乓操作是用于数据流控制的处理技巧[9],数据通过二选一的控制器,向其中的一个SRAM中写数据,与此同时另一个SRAM中的数据被读出,当寄存器的写满信号有效时,二选一的控制器切换读写的寄存器,这样周而复始就会实现数据的无缝缓冲与处理。

图6 乒乓操作Fig.6 Ping-pong operation

2.4 USB 接口

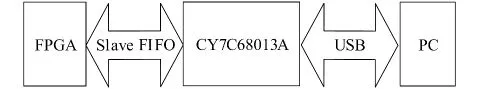

USB作为一种通用的串行接口,具有传输速度快、占用资源少及即插即用等优点[10],因此,USB接口得到广泛的应用。笔者利用EZ_USB FX2 CY7C68013A芯片实现PC机与FPGA之间的通信。

CY7C68013A具有USB2.0的收发器、全速方式、接口引擎、增强型8051、8.5 kByte的 RAM、4 kByte的FIFO存储器、I/O口、数据总线、地址总线、IIC控制器和通用可编程接口[11]。设计中采用USB的全速工作模式,信号速率为12 Mbit/s。

CY7C68013A具有GPIF和Slave FIFO接口两种工作模式[12],笔者采用Slave FIFO接口的工作模式。CY7C68013A具有一种独特的结构,使FPGA与USB共享FIFO存储器,此时增强型的8051不参与数据通信,但可通过FIFO和RAM访问所传输的数据。

在USB进行OUT传输的过程中,USB端只要有一个FIFO为半满即可进行数据发送,当FIFO的写满信号有效时,FX2自动将其转换为外部接口端,排队等待数据读取。当出现一个FIFO的空信号有效时,FX2会自动将其转换到USB接口端,等候数据的写入,并将下一个写满的FIFO转换到外部接口,以供USB读取数据。

FPGA与PC机之间的通信如图7所示。

图7 FPGA与PC机之间的通信Fig.7 Communication between PC and FPGA

3 软件实现

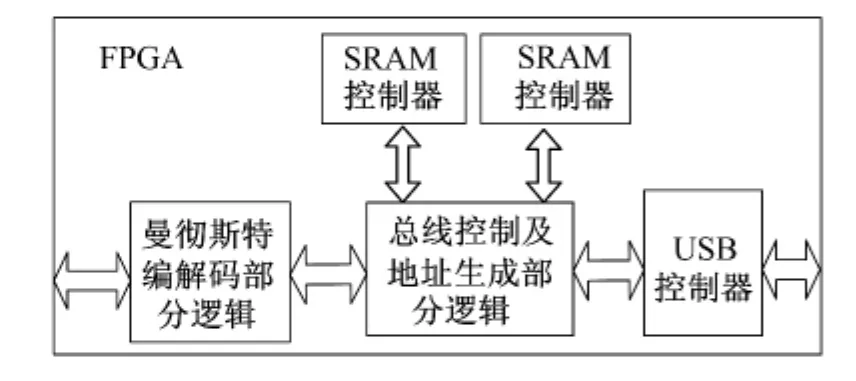

设计核心是FPGA,程序采用硬件描述语言进行编写,在QuartusⅡ软件的环境下进行调试。FPGA作为主控器,需要对SRAM、HI-1567和USB接口进行控制。FPGA内部的结构如图8所示。

3.1 FPGA 控制 HI-1567

FPGA控制HI-1567如图9所示。FPGA的两个输出信号RXENA和RXENB为HI-1567的使能信号。TXINHA和TXINHB为禁止信号,也来自FPGA。根据1553B总线协议,在某一时刻总线上只能有一个终端活动,且接收和发送不能同时进行,因此,这些控制信号需在一个状态机中经过判断获得。

图8 FPGA内部结构图Fig.8 FPGA internal structure

图9 FPGA控制HI-1567Fig.9 FPGA control HI-1567

3.2 FPGA 控制 SRAM

FPGA对SRAM的控制是通过SRAM控制器实现的。SRAM的控制信号主要有CE,OE,WE,LB和UB,其中CE是芯片的片选,OE是输出使能端,LB是低8位控制端,UB是高8位控制端。FPGA主要通过控制上述4个信号实现对SRAM的控制。

3.3 FPGA控制USB接口

FPGA与PC机进行USB通信主要通过控制CY7C68013A实现。CY7C68013A是一种USB协议芯片,支持USB2.0协议。

FPGA对USB接口的控制通过异步状态机实现,异步读状态机有IDLE、STATE1、STATE2、STATE3和STATE4 5个状态(见图10)。每个状态的功能如下。

IDLE:空闲状态。当“读”时,转到状态STATE1。

STATE1:FPGA写FIFO操作,设置FIFOOADR[1:0],转到状态 STATE2。

STATE2:如果FIFO中有数据尚未读出,则转到状态STATE3,否则继续在状态STATE2。

STATE3:SLRD和SLOE为高电平时,FPGA从FD管脚读入数据到输入缓存,SLRD置0,转到状态STATE4。

图10 FPGA控制USB状态机Fig.10 The state flow of FPGA control USB

STATE4:如果进行连续读数据,则转到状态STATE2,否则返回IDLE状态。

4 测试仿真

图11是FPGA采集HI-1567转换器的仿真波形图。在使能信号有效时,由FPGA采集数据。

图11 FPGA采集数据Fig.11 FPGA collects data

图12是FPGA控制SRAM的仿真波形图,其中两个SRAM进行乒乓操作,分别进行数据采集。FPGA向SRAM_1中写数据的同时,从SRAM_2中读取数据;SRAM_2读空后,FPGA再从SRAM_1中读数据,并向SRAM_2中写数据,从而实现数据的无缝传输。

图12FPGA控制SRAMFig.12 FPGA controls SRAM

图13是利用Labview制作的USB调试助手界面在上位机上观察的数据。将官方提供的USB固件程序和厂商号添加到Labview中接收FPGA传输的数据。实验结果表明,该方法得到的数据准确无误,且便于上位机的数据处理。

5 结语

笔者以FPGA为主控器设计1553B总线的通用接口,提高了系统的可靠性和实时性,初步测试满足各类终端的功能。由FPGA通过USB接口向上位机传送数据,实现实时显示,通过功能仿真、逻辑综合和联调测试完成了总线数据的发送与接收。实现了1553B接口设计。

[1]季鹏辉,任勇峰,文丰.基于FPGA的1553B总线控制器设计与实践[J].自动化与仪表,2013,26(3):26-28,40.

JI Penghui,REN Yongfeng,WEN Feng.Design and Practice of 1553B Bus Controller Based on FPGA[J].Automation and Instrumentation,2013,26(3):26-28,40.

[2]赵杰,甄国涌,王宇,等.基于 FPGA的1553B总线测试系统设计[J].科学技术与工程,2013,34(13):10337-10343.

ZHAO Jie,ZHEN Guoyong,WANG Yu,et al.Design of 1553B Bus Test System Based on FPGA [J].Science Technology and Engineering,2013,34(13):10337-10343.

[3]夏清发,胡晓吉.基于FPGA的1553B总线板卡的设计[J].计算机工程与设计,2012,33(11):4131-4137.

XIA Qingfa,HU Xiaoji.Design of 1553B Bus Board Based on FPGA [J].Computer Engineering and Design,2012,33(11):4131-4137.

[4]邢秀琴,姚竹亭.基于1553B总线的通信接口及其应用[J].中北大学学报:自然科学版,2007,28(1):91-94.

XING Xiuqin,YAO Zhuting.Communication Interface and Its Application Based on 1553B Bus[J].North University:Natural Science Edition,2007,28(1):91-94.

[5]谢拴勤,宋捷,宋怀达.基于FPGA+DSP的1553B总线通用接口设计与实现[J].计算机测量与控制,2009,17(1):183-186.

XIE Shuanqin,SONG Jie,SONG Huaida.Design and Implementation of 1553B Bus Universal Interface Based on FPGA+DSP[J].Computer Measurement& Control,2009,17(1):183-186.

[6]周兆军.1553B总线数据模拟器设计[J].舰船电子工程,2012,32(12):90-91.

ZHOU Zhaojun.Design of 1553B Bus Data Simulator[J].Ship Electronic Engineering,2012,32(12):90-91.

[7]周密,金惠华,尚利宏,等.1553B总线协议IP核设计与实现[J].电子器件,2007,30(1):334-338.

ZHOU Mi,JIN Huihua,SHANG Lihong,et al.Design and Implementation of 1553B Bus Protocol IP Core [J].Electronic Devices,2007,30(1):334-338.

[8]杜改丽,封治华,王勇.1553B总线协议分析及应用[J].仪器仪表用户,2007,14(2):6-7,12.

DU Gaili,FENG Zhihua,WANG Yong.Analysis and Application of 1553B Bus Protocol[J].Instrumentation Users,2007,14(2):6-7,12.

[9]闵晓华,陈绍炜,张涛.基于1553B总线的接口软件设计与实现[J].计算机工程与科学,2009,31(1):130-133.

MIN Xiaohua,CHEN Shaowei,ZHANG Tao.Design and Implementation of Interface Software Based on 1553B Bus[J].Computer Engineering and Science,2009,31(1):130-133.

[10]陈升来,郭立红,谭振江,等.Win2000下USB数据采集系统驱动程序开发[J].吉林大学学报:信息科学版,2003,21(2):183-187.

CHEN Shenglai,GUO Lihong,TAN Zhenjiang,et al.The USB Data Acquisition System Driver Development under Win2000 System[J].Jilin University:Information Science Edition,2003,21(2):183-187.

[11]岳奎,刘少君,任参,等.USB协议下PC机与FPGA的数据通信[J].微型电脑应用,2009,25(12):46-47,52.

YUE Kui,LIU Shaojun,REN Can,et al.The Data Communication between PC and FPGA under the USB Protocol[J].Microcomputer Applications,2009,25(12):46-47,52.

[12]张世伟,印世平,何运桃.USB2.0接口传输的FPGA控制与实现[J].国外电子测量技术,2009,28(11):74-76,80.

ZHANG Shiwei,YIN Shiping,HE Yuntao.USB2.0 Interface Transfer of FPGA Control and Implementation [J].Foreign Electronic Measurement Technology,2009,28(11):74-76,80.