一种视频缩放插值算法的FPGA实现

樊凌雁,徐向阳

(1.杭州电子科技大学微电子研究中心,浙江 杭州310018;2.杭州士兰微电子股份有限公司设计所,浙江 杭州310012)

0 引 言

数字视频信号处理的后端,经过处理后的视频信号需要支持不同分辨率的显示器。故需要采用相应的图像缩放处理技术将输入信号的分辨率进行缩放处理以适应不同显示器的需要。在缩放处理过程中,让视频信号仍平滑显示,要对像素进行插值运算[1-2]。目前图像缩放处理通常采用的方法有最邻近点法、双线性内插法、双三次插值法和基于图像边缘的算法等[3-5]。这些插值算法多种多样,各有优缺点,如最邻近点法、双线性内插法算法简单、容易实现,但是效果一般;基于图像边缘的算法在图像边缘区域做特殊处理,图像边缘清晰可见,但是算法实现复杂度高。在视频处理的场合,为提高速度,需要采用硬件方法实现差值算法。目前在进行硬件图像处理过程中,因考虑实现复杂度的问题,大多采用最邻近点法和低次数的插值算法,图像显示的质量较差[6]。为保证在高速进行视频处理过程中,同时达到图像缩放处理的高质量要求,本文提出了一种基于双三次的视频缩放插值的实现方法,针对不同的分辨率,将输入信号进行缩小或放大处理,来适应后续显示器的需要。并在FPGA 上得到实现,满足视频图像缩放的要求。

1 双三次方插值算法描述

双线性算法插值目标图像中需要的像素值是由源图像位置在它附近的2×2 区域4个邻近像素通过加权平均计算得出的。相比于双线性插值算法,对于放大后未知的像素点,以4点为例,双三次插值算法将对其影响的范围扩大到邻近的16个像素点,依据对待求点的远近影响进行插值计算,是三次插值在二维空间上的扩展,可得到较细致的影像。双三次插值算法即克服了最邻近插值算法出现的边缘阶梯现象,又消除了双线性插值算法的边缘模糊效应,是一种插值效果较好但是运算量大的插值算法。

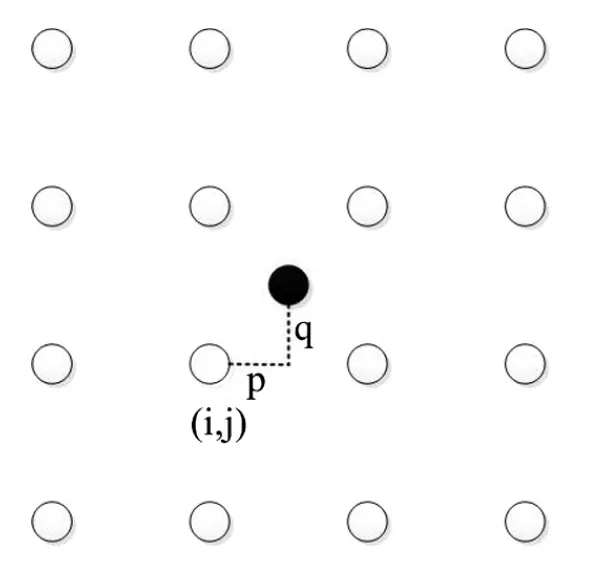

双三次插值算法的目标像素如图1所示。图1中,空心圆代表低分辨率图像中的像素,实心圆代表待插值的高分辨率像素,(i,j)是原图像中像素的坐标,(i+p,j+q)是待插值的高分辨率像素的坐标。

图1 双三次插值算法的目标像素

双三次插值基于如下的三阶多项式产生插值系数:

式中,w为目标插值点与周围邻近点的距离。

双三次插值算法的插值公式如下:

式中,A,B,C代表3个矩阵:

式中,S(w)代表插值基函数,f(i,j)代表原图像像素的灰度值,矩阵B 包含双三次估计窗口的所有像素。

2 算法实现

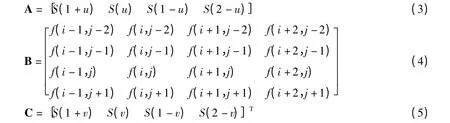

双三次插值硬件实现时,为降低计算复杂度,通常分解为水平和垂直处理的两个一维的插值。整个处理分为4次水平处理和一次垂直处理两个过程。

视频缩放模块的硬件实现模块如图2所示,视频信号在缩放前,首先要先放入先入先出缓存器(FIFO)中缓存,然后进行水平缩放,缩放后数据放入行缓冲区,在从缓冲区中取出数据进行垂直缩放。最后经过处理成特定的接口信号送入显示器中显示。

图2 视频缩放模块框图

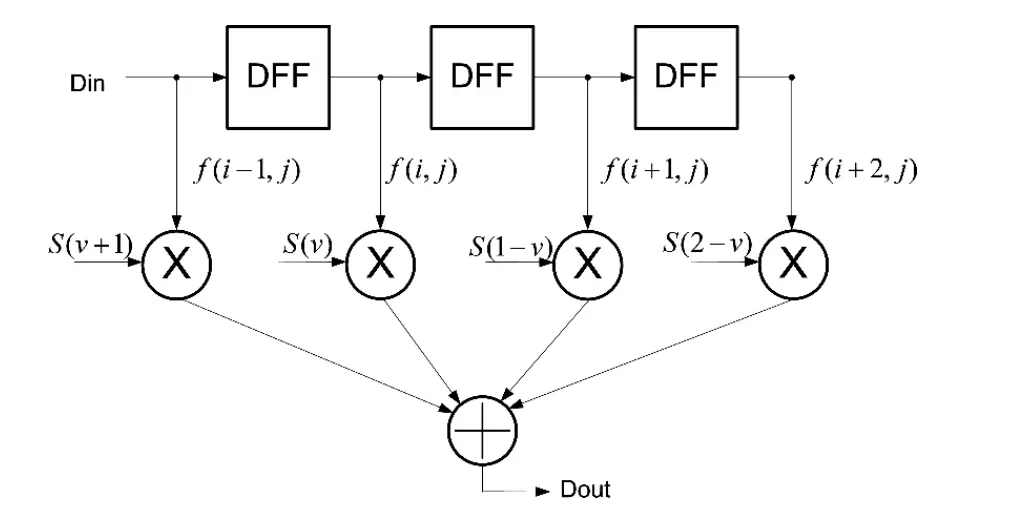

无论是行处理还是列处理,目标像素和源像素的距离决定了插值系数的大小,在具体硬件实现时,为了易于实现,插值系数采用分段处理,并且先进行水平缩放再进行垂直缩放。在FPGA实现时,采用如图3所示的框图实现水平缩放,垂直缩放的实现原理类似。

图3 水平缩放的内部实现框图

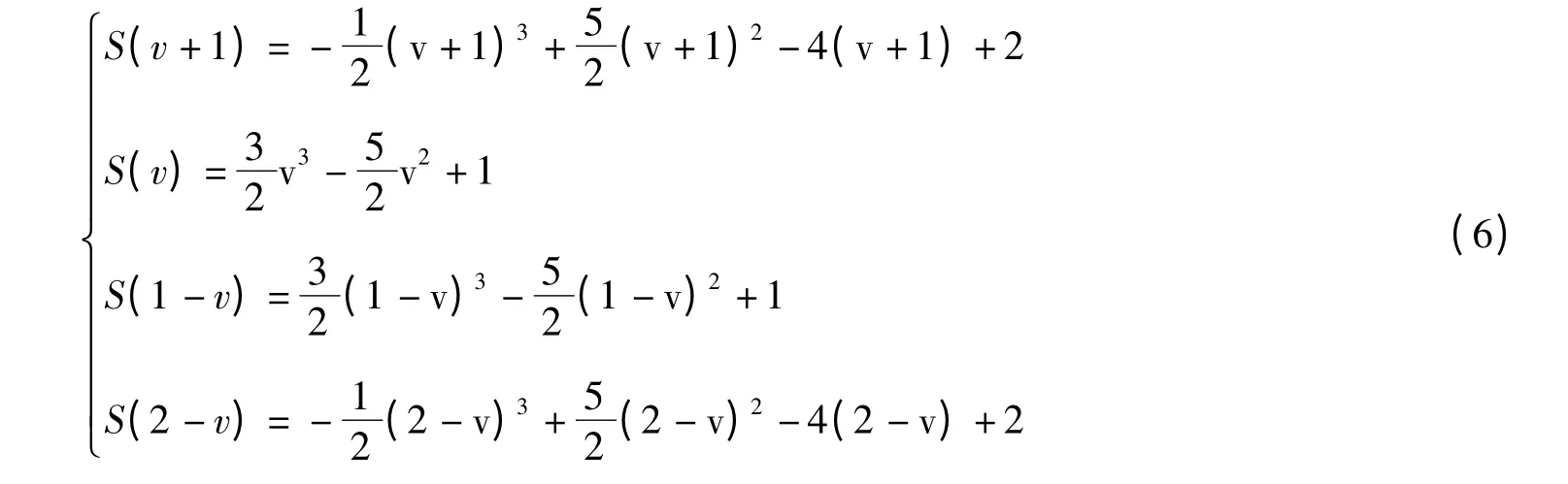

图3中,DFF表示移位寄存器,插值系数矩阵根据式(1)得到:

为了降低计算复杂度,距离系数事先计算好,采用矩阵形式存放在处理器的存储器中,视频信号输出时,根据显示器的分辨率,选择调入不同的系数矩阵,实现不同的缩放比例。举例来说,如果输入信号的分辨率为x,输出信号的分辨率为y,则缩放比例:x/y=n(k/g),n为整数,k <g,调入的系数矩阵即为k/g 带入式(6)后得到。

举例子说明,如果缩放比例为0/16,缩放比例为整数,缩放系数为[0 255 0 0]/256,也就是对输出信号有影响的就是当前位的图像灰度值;如果缩放比例为1/16,缩放系数为[-7 252 10 0]/256,除了当前位,前一位和后一位的像素值影响输出,影响比例由系数大小决定。

3 实验结果

视频缩放模块在某公司数字视频信号处理芯片中应用,用Verilog 语言对算法进行描述,并在Xilinx公司提供的可编程逻辑器件集成开发环境Xilinx ISE10.1 中进行编译和综合,目标FPGA 芯片选为Virtex-4系列的XC4VSX-35,已通过FPGA 验证。因为采用了在RAM 中配置不同分辨率的系数,所以可以支持缩小放大32倍以内的视频信号,后续的显示器支持标准视频信号和高清视频信号。

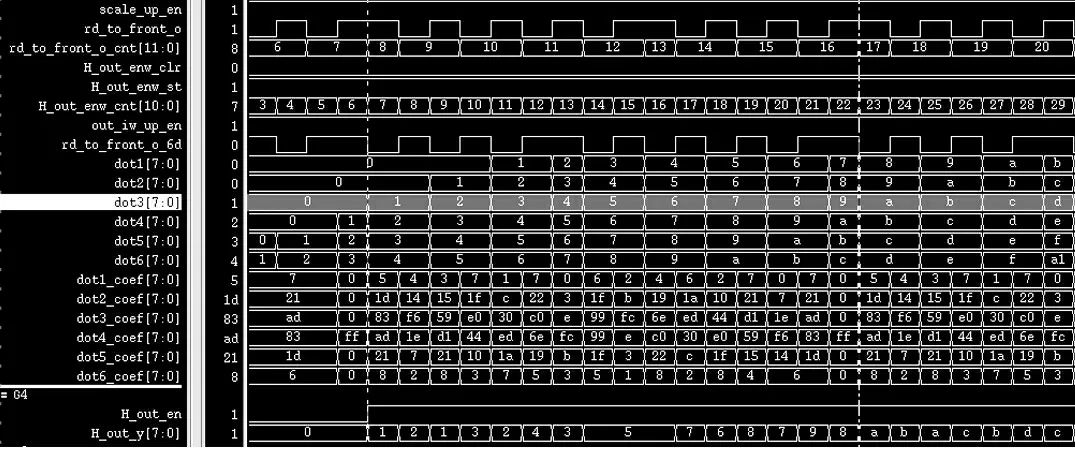

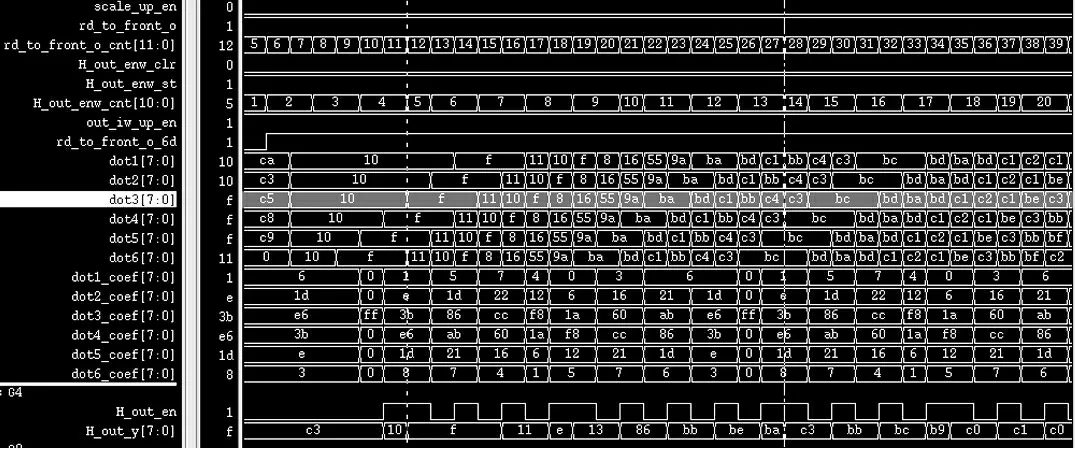

在VCS仿真测试中,通过测试现有的标准视频信号和高清视频信号之间的缩放,都满足要求。水平放大的仿真结果如图4所示。输入视频信号是720列,输出到显示器的视频信号是1 280列,故放大倍数是16/9倍。图4中,两条白色光标之间数据显示了放大过程。器件输入的数据计数信号是8 16,共9个像素点,对应的输出像素计数信号是7 22,共16个像素,完成了放大过程。视频信号的水平缩小仿真结果如图5所示。

图4 水平放大(720列到1 280列)

图5 水平缩小(1 280列到720列)

经过FPGA实现算法的实际图片放大效果如图6、图7所示,图6为720×480的图片,图6采用本文算法放大为1 280×720 后如图7所示,两张图片均采用30%显示。

图6 原图720×480(30%显示)

图7 放大为1 280×720的图(30%显示)

4 结束语

本文针对视频后处理信号,提出了一种视频缩放插值算法的FPGA 硬件实现方案。在缩放插值算法实现时,采用插值矩阵存放插值系数,根据视频输入和输出信号的缩放关系,调用对应的插值系数,实现图像缩放,保证插值效果,可支持多种分辨率的显示器输出。

[1]尤玉虎,周孝宽.数字图像最佳插值算法研究[J].中国空间科学技术,2005,3(6):14-18.

[2]Kemal U,Alshin A,Alshina E,et al.Motion Compensated Prediction and Interpolation Filter Design in H.265/HEVC[J].2013,7(6):946-956.

[3]Sonka M,Hlavac V,Boyle.Image Processing,Analysis and Machine Vision[M].Canada:Thomson,2007:121-134.

[4]程光权,成礼智.基于小波的方向自适应图像插值[J].电子与信息学报,2009,3(2):265-269.

[5]任杰,刘家瑛,白蔚,等.基于隐式分段自回归模型的图像插值算法[J].软件学报,2012,23(5):1 248-1 259.

[6]李开宇,张焕春,经亚枝.基于FPGA 动态可重构的高速、高质量的图像放大[J].中国图象图形学报,2005,10(1):69-74.