基于FPGA的TDM over IP的设计

阴亚芳, 刘传明, 张 斌

(西安邮电大学 电子工程学院, 陕西 西安 710121)

基于FPGA的TDM over IP的设计

阴亚芳, 刘传明, 张 斌

(西安邮电大学 电子工程学院, 陕西 西安 710121)

设计一种TDM over IP的技术系统。该系统用FPGA将E1数据包通过串并转换到千兆以太网数据包,经IP网传输到终端设备,再通过并串转换将以太网数据包转换成E1数据包完成传输。经过软件和硬件测试验证了此系统在千兆以太网上传输的可行性,系统没有出现误码,固有输出抖动是0.55UI,最大峰值抖动指标均满足ITU-G.823标准要求。

时分复用模式;E1;千兆以太网;TDM over IP

IP网络在许多领域都有着广泛的应用,如IP网络电话就是当前一个比较成功的典型应用[1]。它的主要特点是成本低、操作灵活、资源共享等[2-3]。目前来看,IP网络将取代上一代基础网络架构,由传统的时分复用(Time Division Multiplexing, TDM)设备向高性能分组主干网转移已经成为一种发展趋势。目前研究的热点和关键难题是怎么样通过IP网络高效地传输TDM业务[4]。以色列的RAD数据通讯公司率先提出TDM over IP技术[5]的概念,TDM over IP技术能在IP网络中传输传统的TDM语音和数据业务,很大程度地发挥IP网络的优势,同时给使用者提供了一种由传统电信网络向未来的全IP网络过渡的设计方案[6]。

目前已经出现了基于FPGA的10/100M以太网的TDM over IP实现系统[7],但是其带宽比较低,而且传输速率比较慢。本文拟运用该技术,来实现千兆以太网传输TDM数据。

1 TDM over IP概述

1.1 工作原理

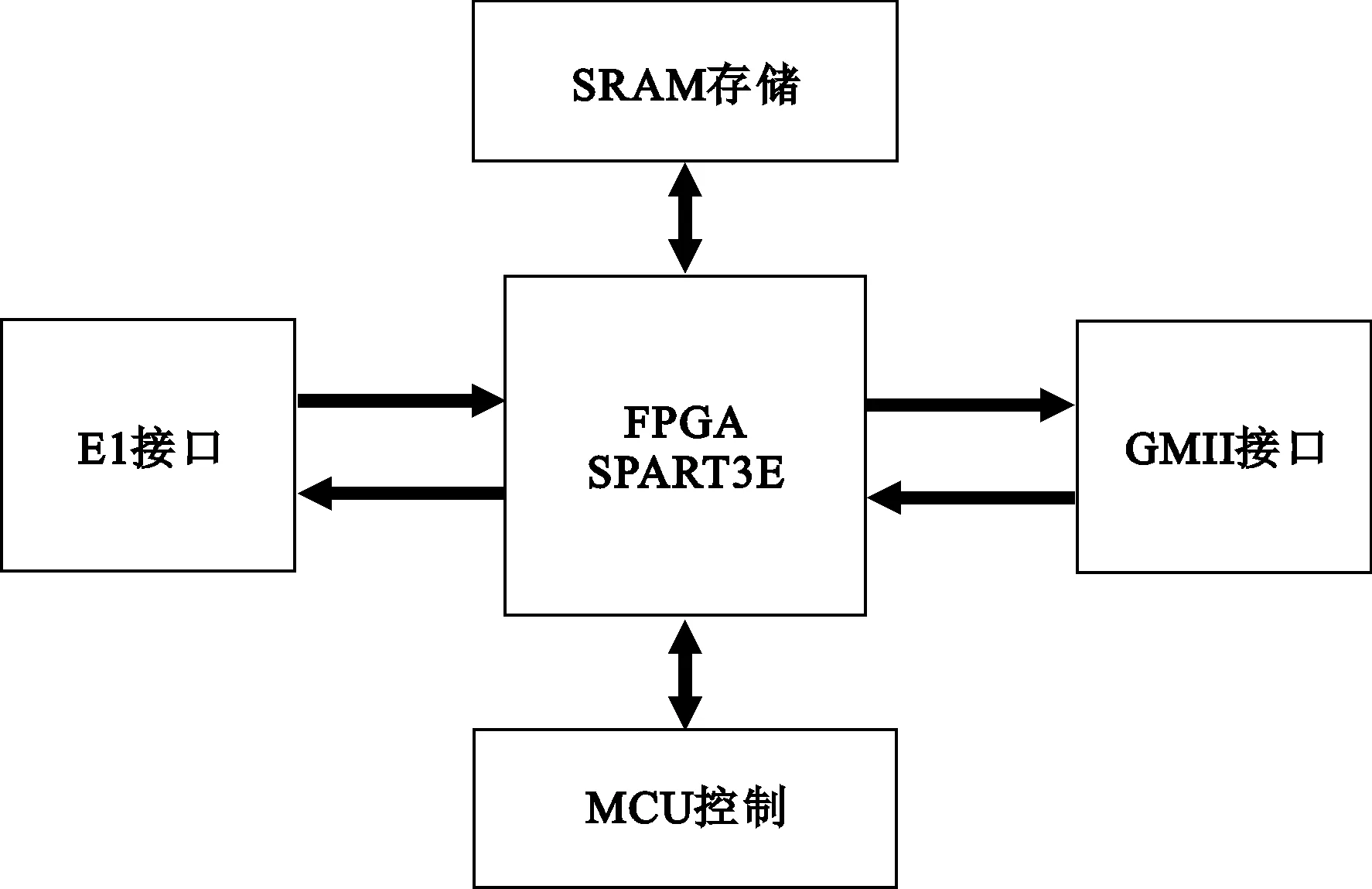

TDM over IP的工作原理[8]如图1所示。将E1数据流打包成为TDM的数据帧,然后在TDM数据帧前插入IP帧头,封装成IP数据帧。将IP数据帧通过IP网络快速运送到对端设备,在对端重新生成工作时钟,再将IP数据帧中的IP帧头去掉,把剩余的数据帧解帧成E1数据流发送出去。因为E1数据流在IP网络中的传输是透明的,所以它能与传统的电信网络很好的兼容,所有传统的业务,例如数据、协议等都能够不作改变地使用此技术,而且终端设备也不用改动。

图1 TDM over IP原理

1.2 TDM over IP报文

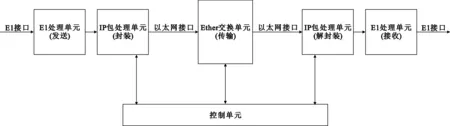

数据在包交换的IP网络上传输时,TDM over IP芯片将TDM数据封装为以太报文,报文的格式如图2所示。

以太报文的帧头共有6种,分别为互联网协议第四版(Internet Protocol version 4,IPv4)、互联网协议第六版(Internet Protocol version 6,IPv6)、用户数据报协议(User Datagram Protocol,UDP)、第二层隧道协议第三版(Layer Two Tunneling Protocol - Version 3,L2TPv3)、城域以太网(Managed Extensibility Framework,MEF)、多协议标签交换(Multi-Protocol Label Switching,MPLS)。

在代码实现时,这6种格式先添加在一个只读存储器(Read-Only Memory,ROM)中,当需要添加帧头时,微控制单元(Micro Control Unit,MCU)会调用ROM中的帧头。

6种帧格式的参数值可以参考IEEE802.3[9]及相关协议规定。

图2 TDM over IP封装以太报文

2 FPGA设计实现

TDM over IP的设计是要在FPGA开发板内部将E1数据流打包成Ether数据包,通过千兆以太网发送到目的端,再在目的端选出Ether数据包,恢复成E1数据流。为了实现Ether数据和E1数据在传输速率及结构上的匹配,设计时参考了IEEE802.3、ITU-TG.823[10]等协议标准。主要分为两部分,分别是E1数据转换成Ether数据(发送)和Ether数据转换成E1数据(接收)。

2.1 E1数据转换成Ether数据

E1数据到Ether数据的转换主要有4个部分:E1接收模块、E1接收FIFO、Ether打包发送模块以及帧头ROM。E1到Ether转换的难点是在E1接口、千兆媒体独立接口(Gigabit Medium Independent Interface,GMII)和缓存间的数据交换。由于以太网接口的时钟为125M,而E1接口的工作时钟为2.048M,各个模块间的数据交换为异步过程,为保证数据交换的准确性,需要用异步FIFO来实现。FIFO的大小为二帧(512 Bytes),先从E1接口接收数据,存入异步FIFO中,当检测到存入异步FIFO的数据大于一帧时,产生中断信号,通知Ether打包发送模块准备,将从异步FIFO中读到的E1数据打包成帧发至GMII接口。实现原理如图3所示。

图3 E1到Ether实现框图

2.2 Ether数据转换成E1数据

Ether数据到E1数据的转换主要有4个部分:Ether接收模块、Ether字节处理模块、E1时钟处理模块以及E1数据发送模块。Ether数据到E1数据转换的难点主要集中在E1时钟的恢复和GMII接口到E1接口的数据转换。E1时钟的恢复解决方案有两种。一种方案是在TDM over IP设备外添加一个精确的时钟源,作为参考时钟;另一种方案是接收端重新生成本地时钟。由于第一种方案增加了成本,而且存在时钟源的稳定性等问题,因此选择第二种方案。第二种方案通过比较FIFO接收和发送出去帧的数目以及测量FIFO的深度来计算发送端和接收端的时钟偏差,然后调整接收端的时钟,这样通过不断比较就能够实现接收端时钟的动态跟踪及校准[11-13]。由于GMII接口的时钟是125M,而E1接口时钟2.048M,时钟不同步,因此GMII接口到E1接口数据转换需要通过异步的FIFO来实现数据转换,FIFO的大小为二帧(512 Bytes),在转换前先将Ether数据的帧头去掉,剩下的净负荷进行数据转换,当检测到一帧完成时,Ether接口再向FIFO中发送一帧数据,依此类推完成数据的转换。实现原理如图4所示。

图4 Ether到E1实现框图

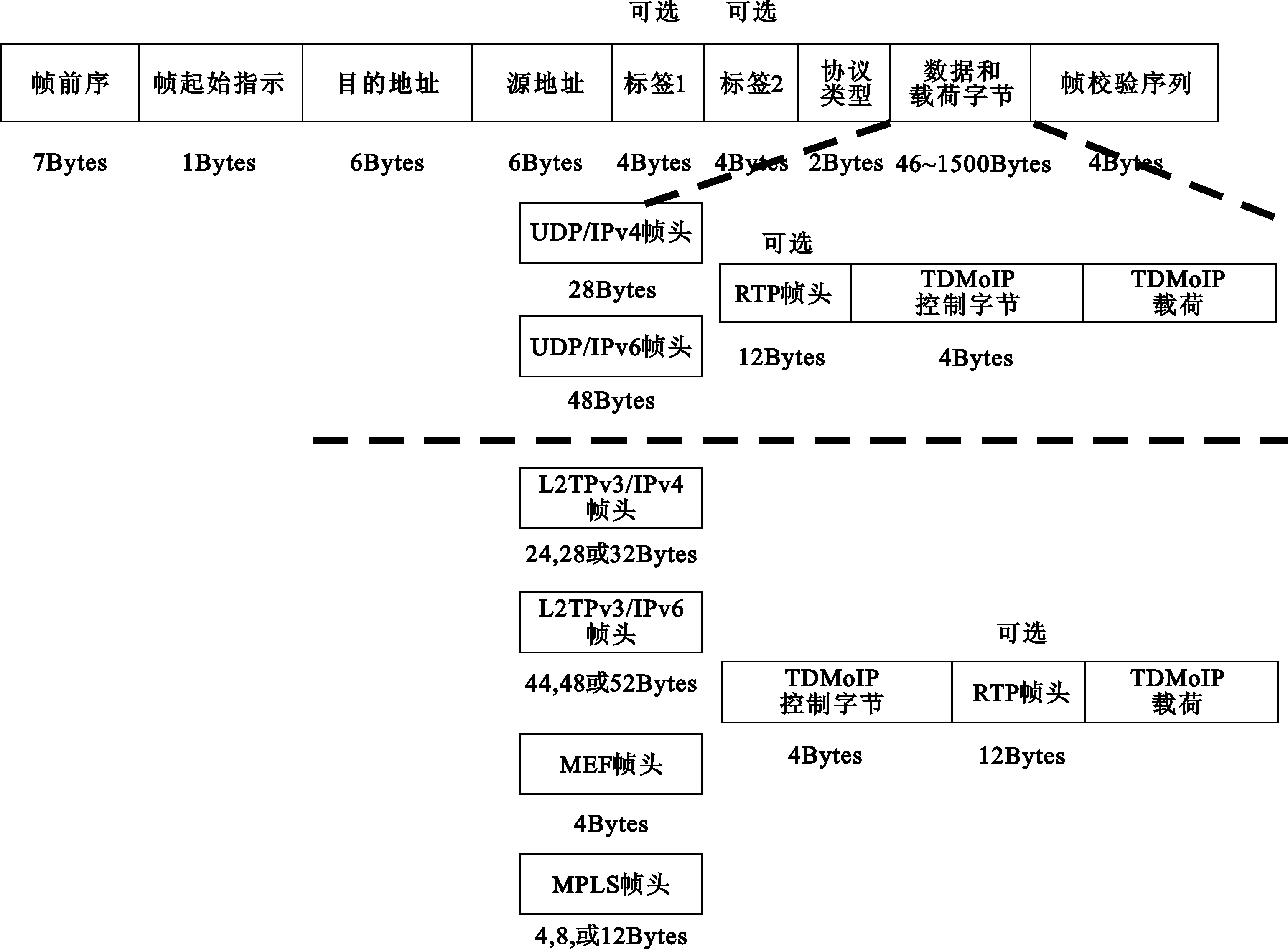

FPGA硬件实现电路主要采用的是一片XILINX的FPGA芯片,外加静态随机存取存储器(Static Random Access Memory,SRAM)、以太网交换芯片、MCU等芯片,具体硬件实现如图5所示。

图5 TDM over IP硬件架构

3 仿真验证

3.1 软件仿真验证

通过Modelsim仿真软件对代码进行仿真,在仿真的过程中Ether端进行环回连接,输入的是E1数据和时钟,输出也是E1数据和时钟,然后进行比较。仿真波形如图6所示。仿真时间是8ms,rx_clk_2m和e1_data是E1端发送的数据,clk_2m和tx_e1是接收端接收到的E1数据,paral_in经过并串转换后为E1提供输入数据,paral_out是E1输出数据经过串并转换的值,对paral_in和paral_out波形的比较后,能够完成正常通信。

图6 Modelsim仿真波形

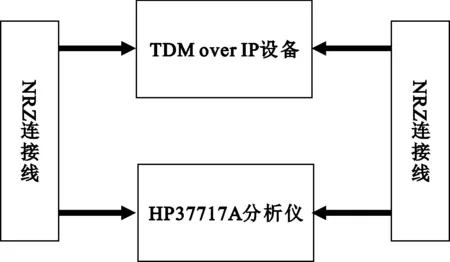

3.2 硬件验证

在FPGA内部Ether端口环回连接,然后将FPGA开发板与HP37717A分析仪[14]连接,硬件验证模块如图7所示,HP37717A分析仪先输出E1的时钟和数据,然后再分析环回接收到的E1数据和时钟。

图7 TDM over IP设备验证模块

E1支路的最大峰值抖动测试结果如图8所示,实线是设备的抖动测试结果,虚线是标准的抖动指标,在虚线之上的结果满足ITU-G.823要求。另外,测试结果表明,系统没有出现误码,固有输出抖动为0.55UI,最大峰值抖动等指标均满足ITU-G.823要求。

图8 TDM over IP设备抖动测试结果

4 结束语

设计一种基于FPGA的千兆以太网传输的TDM over IP系统,实现了TDM数据在IP网络的快速传输,完成了TDM业务与IP网络的兼容和优化,而且经测试E1接口的抖动满足ITU-G.823标准的要求。

[1] 马严.基于IP网络的多媒体通信[J].西安邮电学院学报,2005,10(1):38-43.

[2] 冯景超,师亚莉.移动IP网络的视频通信[J].西安邮电学院学报,2005,10(3):39 - 42.

[3] 杜能功.Asterisk和IAX协议部署VOIP网络[J].西安邮电学院学报,2006,11(3):34-37.

[4] Graham C. Transferring TDM to IP technology[J]. Electronic Product Design,2003,24(8):41-43.

[5] 刘加杰,楚纪正,王琦.TDM over IP的发展趋势及其应用[J].光网络,2009(9):9-12.

[6] Parikh K, Kim J. TDM services over IP networks[C]// Military Communication Conference.US: Institute of Electrical and Electronics Engineers Inc, 2007:1-10.

[7] 景英娟,范红,董育宁.TDM over IP关键技术研究[J].江苏通信技术,2005,21(1):22-25.

[8] 陈伟平.基于FPGA的TDMoIP方案设计与实现[J].江西通信科技,2007(4):9-12.

[9] IEEE Std 802.3,1998 Edition,LAN MAN Standards Committee of the IEEE Computer Society[S].USA:IEEE Standards Department ,1998.

[10] ITU-T.G.823,The control of jitter and wander within digital networks which are based on the 2048 Kbit/s hierarchy[S].CH:CCITT,2005.

[11] 宁连悦.基于FPGA的Ethernet over E1接口芯片的设计与实现[D].西安:西安电子科技大学,2006:5-42.

[12] 曾宇辉.TDM over IP系统框架与实现方案研究[D].武汉:华中科技大学,2007:1-30.

[13] 曾宇辉,周宗仪.TDM over IP技术原理及实现方案[J].计算机与数字工程,2007,35(7):154-156.

[14] Hewlett-Packerd.HP37717A PDH/SDH Test set Operating Manual[M].[S.I.]: U.K,HP, 1994:1-15.

[责任编辑:祝剑]

Design of TDM over IP scheme with FPGA

YIN Yafang, LIU Chuangming, ZHANG Bing

(School of Electronic Engineering, Xi’an University of Posts and Telecommunications, Xi’an 710121, China)

A technical scheme of TDM over IP is designed in this paper. Transitions between the E1 packet and Gigabit Ethernet packet can be achieved by using FPGA and by serial-parallel conversion and IP network. The feasibility of this system in the Gigabit Ethernet transmission is verified by software and hardware test. The system has no error. The natural output jitter is 0.55 UI. The maximum peak jitter can meet the requirements of ITU-G.823 standard.

TDM, E1, gigabit-ethernet, TDM over IP

10.13682/j.issn.2095-6533.2014.06.013

2014-03-04

阴亚芳(1966-),女,博士,教授,从事数字信号处理及光通信技术研究。E-mail:yinyf@xupt.edu.cn 刘传明(1989-),男,硕士研究生,研究方向为电路与系统。E-mail:410976664@qq.com

TP393.5

A

2095-6533(2014)06-0066-05