空间交会对接多体制接收机设计与实现

程庆林,洪 亮,吴毅杰,石云墀

(上海航天电子技术研究所,上海201109)

空间交会对接多体制接收机设计与实现

程庆林,洪 亮,吴毅杰,石云墀

(上海航天电子技术研究所,上海201109)

空间交会对接时,空空通信系统需在两个航天器之间建立双向通信链路,完成两者间的信息交换。在载人航天交会对接任务中,空空通信系统担负交会对接段以及撤离段航天器间的双向链路数据传输任务。针对不同的任务模式、分析不同信号的解调模型和算法特点,基于软件无线电技术确定本系统的全数字化解调算法和硬件平台设计方案,实现过程运用复用/优化设计思路,节省了逻辑资源、降低了算法复杂度。对关键指标的测试表明,该设计可满足空空通信系统的指标需求。

多体制;数字接收机;空空通信系统;交会对接

1 引言

航天器空间交会对接是空间交会与空间对接的总称,是两个航天器之间的在轨运动行为。通常称在轨运行的航天器为目标航天器,与目标航天器进行交会对接的航天器为追踪航天器。空空通信设备在执行任务A时,追踪航天器与目标航天器之间双向数据传输速率较低,采用DS⁃DB⁃PSK(Direct Sequence Spread Spectrum⁃Differential Encode Binary Phase⁃Shift Keying)直接序列扩频方式进行通信;空空通信设备任务模式为任务B时,追踪航天器与目标航天器之间双向数据传输速率较高,追踪航天器与目标航天器之间空空通信采用非扩频的差分二相相移键控(Differentially Encoded Binary Phase⁃Shift Keying,DBPSK)和差分正交相移键控(Differentially Encoded Quadra⁃ture Phase⁃Shift Keying,DQPSK)进行通信。本文从硬件平台通用化、软件功能模块化的角度出发,在基于“FPGA(Field Programmable Gate Array)、ADC(Analog Digital Converter)”架构的硬件平台上设计并实现了一种具有三种解调模式的数字接收机。在继承二期空空通信接口和通信指标的基础上扩展了接收机的DQPSK解调功能,提高了应用广度和可靠性。

2 需求分析

2.1 工作模式需求

1)在执行任务A时,数据通信链路继承二期空空通信的通信模式。整个过程中空空通信链路数据率较低,综合考虑发射功率和捕获跟踪作用距离,应采用扩频方式进行通信。

扩频模式下,直接序列扩频体制将原始数据与远高于其码速率的伪噪声序列模二加后生成新序列,可明显扩展信号频谱。接收时,利用伪噪声序列的自相关特性能将信号能量集中在窄带范围内,提高接收信号的信噪比,获得较高的处理增益[1]。

2)在执行任务B时,数据通信链路需要在任务A的基础上增加大量的数据,双向通道数据量较大,应采用非扩频的模式进行通信。

非扩频模式下,相移键控(Phase⁃Shift Keying,PSK)调制方式具有恒定的包络、在给定信号电平中有最低误码率、高效率等特点而被广泛应用在军事和商业通信系统中[2]。QPSK调制体制在相同符号速率情况下码速率是BPSK调制的2倍,拥有更高的频带利用率[3]。针对双向通信链路需求同时继承二期的通信需求保留非扩频DBPSK调制体制,新增DQPSK调制体制。

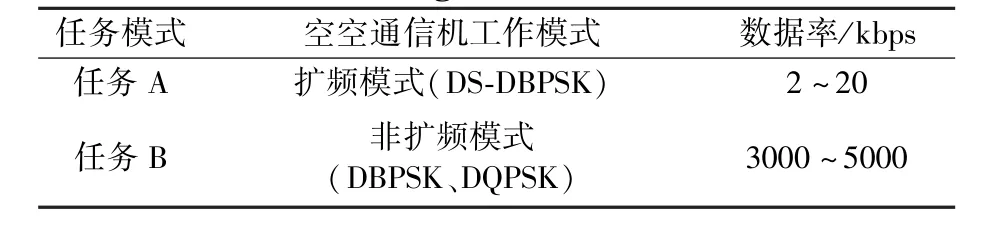

表1给出了空空通信设备在不同任务模式下的数据率和工作模式。

表1 不同任务模式下工作模式和数据率需求Table 1 The modulation mode and bit rate requirementat different stages

2.2 调制模式和码速率

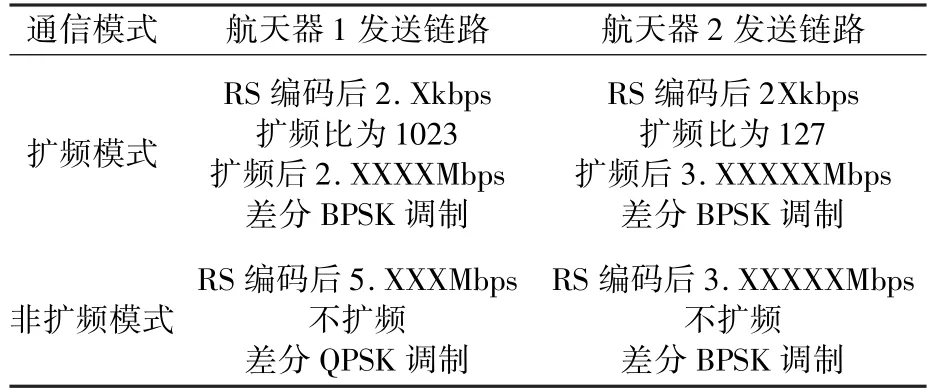

空空通信设备具有扩频与非扩频两种通信模式,表2给出了两种通信体制下空空通信机中的传输速率及调制方式。

表2 空空通信机码速率及调制方式Table 2 The bit rate and modulation mode of space to space communicator

3 多体制接收机的设计

空空通信机是空间交会对接任务中的核心设备,它的内部结构如图1所示。多体制中频接收机作为空空通信机中的关键部件,需要把天线接收到的信号放大、数字下变频、解扩、解调、RS解码后送给空空接口[1]。

图1 空空通信机内部组成Fig.1 The structure of space to space communicator

多体制接收机中的关键技术是中频信号的解扩、解调,该功能由中频解扩/解调模块实现[1]。考虑到追踪航天器和目标航天器的通信链路中的码速率、扩频比不同,若要采用软件无线电技术实现三种不同的调制体制的中频信号的解扩/解调功能,从平台通用化的角度出发可基于相同的硬件平台加载不同的软件来实现;从软件功能模块化的角度出发可对功能相同的模块进行复用设计,减少逻辑器件的资源损耗;从工程继承性角度出发可涵盖之前的空空通信指标和接口,增强可靠性。

多体制中频解扩/解调模块的主要技术指标:中频7X MHz;采样率DS_DBPSK:45.X MHz/56. X MHz,DQPSK:45.X MHz,DBPSK:56.X MHz;载波最大多普勒频偏15 kHz。

4 多体制接收机的实现

4.1 硬件设计

系统的应用目标包含航天产品,对可靠性的要求非常严格。减少系统使用的器件种类、降低系统的复杂程度,能够有效的提高系统的可靠性。综合以上因素,选择使用“ADC+FPGA”的方案进行设计,系统的硬件框图如图2所示。

图2 系统硬件框图Fig.2 Block diagram of the system hardware

下面对硬件平台主要构成进行说明。

4.1.1 模/数转换器

模/数转换器(ADC)使用的是ADI公司生产的AD6645,该芯片采用单电源(+3.3 V)供电,内置基准和采样保持电路,转换位数14 bit,最高工作频率可达200 MHz,最大转换速率105 MHz,输入的信号带宽最大可达3 GHz,输出的数据格式可以设置为二进制补码或偏移二进制格式。接口形式简单,只需提供一个采样时钟,14位的并行数据即可按时间顺序依次输出[4]。ADC的输入采用差分低压正发射极耦合逻辑(Low Voltage Positive Emitter⁃Couple Logic,LVPECL)电平,AD转换数据可以截取N bit(N≤14)或者全部选用14 bit作为有效数据,编码形式为二进制补码。

4.1.2 FPGA

FPGA使用的是Xilinx公司的300万门FP⁃GA⁃XC2V3000,内含14436个Slice、1728 Kbit的RAM和96个18 bit×18 bit的乘法器[5],完全能够满足应用的需求。解扩/解调过程中的伪码捕获、伪码跟踪、载波捕获、载波跟踪、数字变频、数字滤波、数字基带处理以及后续的RS解码等功能均由其实现。

4.1.3 时钟源

由于解扩/解调系统的工作时钟需要根据不同的解调模式发生改变。为了提高系硬件平台的灵活性和通用化程度,配置两片频率分别为45.X MHz和56.X MHz晶振,必要时可配合DCM得到不同的时钟资源以满足系统需求。

4.2 软件设计

FPGA软件是接收机的核心,由并行相关器、伪码发生器、下变频器、鉴相器、环路滤波器、RS解码解帧等模块组成。每个功能模块在数字域都有其相对应的模型,因此所有的功能部件都工作在数字域,采用Verilog HDL语言编写。

4.2.1 扩频模式

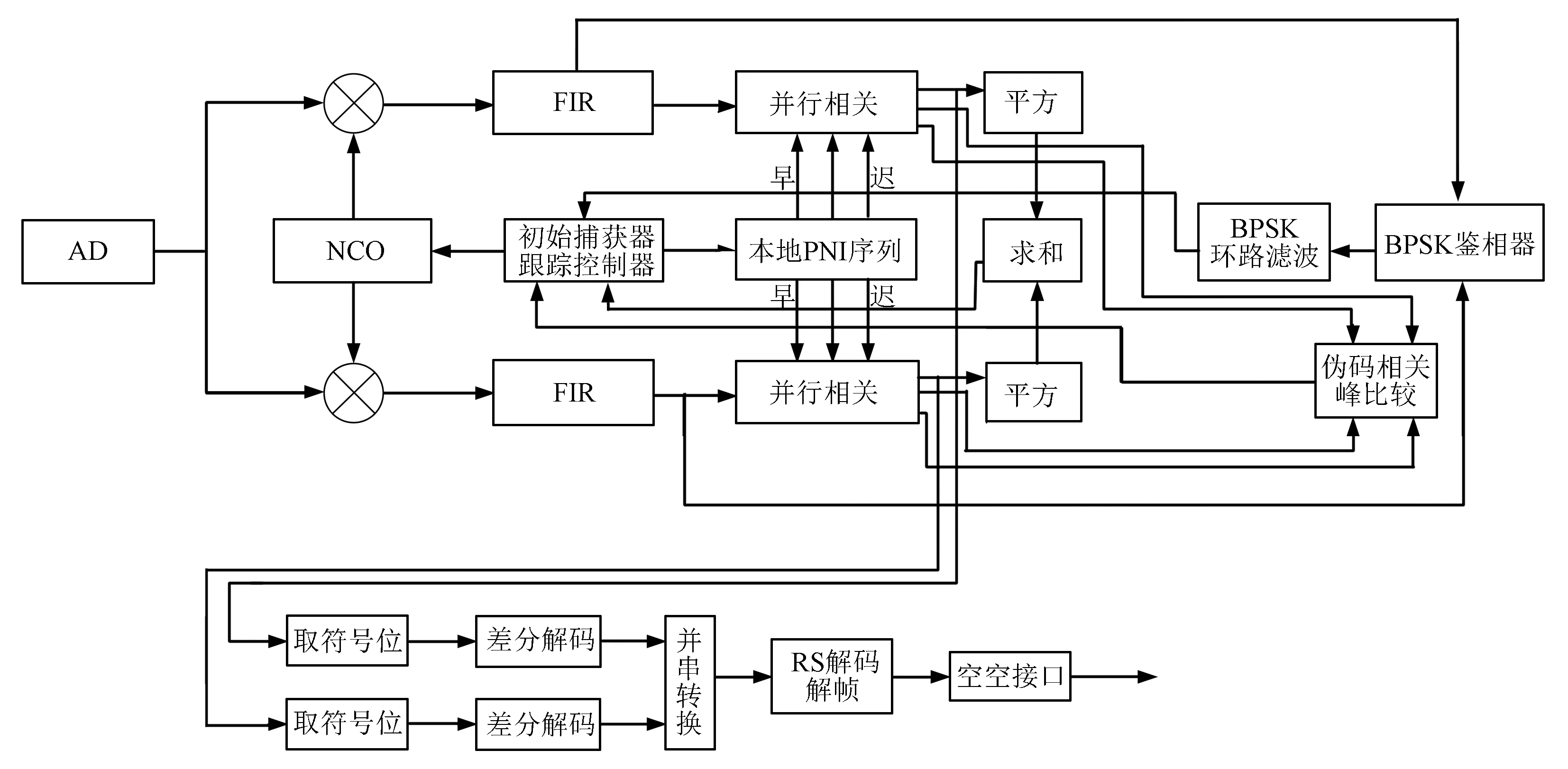

扩频模式下多体制接收机需要对发送来的数据进行解扩、BPSK解调、RS解码、解帧后输出原始信息给空空接口[1]。根据以上要求,扩频模式软件设计框图如图3所示。

1)伪码的捕获和跟踪

直接扩频信号解扩的关键是保证本地PN序列和与接收信号同步。通过与本地PN序列进行相关运算恢复出原始数据。伪码的同步分捕获和跟踪两个阶段:通过扩频码的捕获可使本地伪码与接收到的码元基本保持同步,获得一定的同步精度(如1/2码元宽)。由于发射机和接收机的相对运动及时钟的不稳定,特别是在扩频模式下,须进一步跟踪接收信号,使本地伪码尽可能跟随接收信号的变化,将同步精度控制在更小码元周期范围内,进一步降低数据误码率。综合考虑算法复杂度和逻辑资源伪码捕获所采用的多通道相关捕获法,伪码跟踪阶段采用延迟锁定环,门限判决阶段采用基于瞬时标定功率的自适应算法[1]。

2)载波的捕获和跟踪

在进行载波捕获时,为了能够达到最小的捕获时间,应该先搜索最大可能性的频率点,然后再搜索次可能性的频率点。在不考虑多普勒漂移的情况下,中频输入信号的频率点为18.X MHz,所以这就是可能性最大的频率点,搜索应该围绕这个频率点展开。搜索策略如图4所示。

假设频率搜索带宽为f,频率搜索步进为Δf,那么需要在f/Δf个频率点上进行搜索。由于采用并行相关,因而调整1次码相位可以完成多个码相位位置的相关计算。设在一个频率点上需要调整m次码相位,即m次码相位调整可以完成一个完整PN序列所有码相位的遍历;并且设一次码相位调整需要相位计算时间T才能完成计算,则捕获时间为mTf/Δf。

载波跟踪阶段采用经典的Costas环,包括下变频,低通滤波,鉴相器,环路滤波和压控振荡器[6]。由于这一部分与非扩模式下DBPSK解调的功能相似,考虑对该部分模块功能进行复用。

4.2.2 非扩频模式

BPSK信号与QPSK信号解调的主要区别:

在载波同步上,两者的鉴相算法完全不同;在基带处理上,两者的编码特点不同,使得各自的差分解码在实现时也不同。其次,因为BPSK信号携带信息的只有I路,不需要并串转换模块,而QPSK信号I、Q两路都携带相应的码元信息,需要对I、Q路数据信息进行串行组合。

1)鉴相算法

经典的Costas环的中的鉴相器是一个简单的乘法器,该环路被广泛应用在各种数字通信解调接收系统中。但是经典Costas环只能解调BPSK信号和UQPSK信号,要实现QPSK解调必须考虑使用其他的环路。将经典的Costas环进行推广得到可以用于QPSK载波恢复的改进型硬判决Costas环[2],其中的鉴相部分就是硬判决鉴相器,其鉴相算法实现框图如图5所示。

图3 扩频模式软件设计框图Fig.3 The FPGA structure of DSSS demodulation

图4 扩频模式下载波搜索策略Fig.4 The carrier searching strategy of DSSS demodulation

图5 硬判决鉴相器算法实现Fig.5 The implementation of hard-decision phase detecting algorithm

其中sgn()表示符号函数,表3给出了两种锁相环路中鉴相器的鉴相算法。

表中:Ud表示鉴相误差,I、Q表示经低通滤波后的同相、正交信号。Δω、Δφ分别表示输入输出信号的频差和相差。当环路锁定时Δω=0,I(k)2=1、Q(k)2=1,Δφ很小。

表3 两种鉴相器的鉴相算法Table 3 The phase detection algorithm of two phase detectors

2)数字下变频器

下变频器主要由三个部分组成:本地振荡器,数字混频器,低通滤波器。

数控振荡器(Numerically Controlled Oscillator,NCO)的原理与直接数字频率合成的原理相同,也是从相位概念出发直接合成所需的正/余弦波形[2]。将采样频率fclk均分为2N份,输出频率是频率分辨率的s倍,s是频率控制字(Frequency Control Word,FCW),则有式(1):

数字混频器完成采样的信号与NCO产生的正/余弦信号相乘;低通滤波器滤除其中的二次倍频分量。

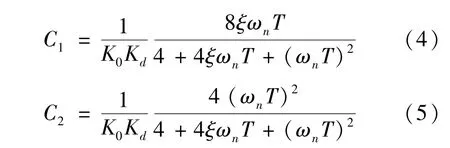

环路滤波器有很多类型,常见的主要包括RC滤波器、无源比例积分滤波器和有源比例积分滤波器[7],这里选用有源比例积分滤波器。典型的一阶模拟环路滤波器的传递函数如式(2)、(3)所示:

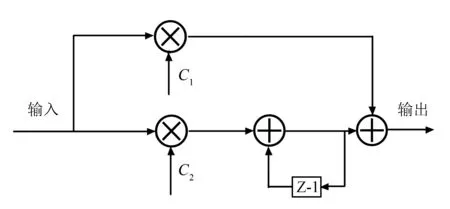

图6 环路滤波器基本结构Fig.6 The basic structure of loop filter

利用双线性变换,得到环路滤波器的最终计算公式如式(4)与(5)。

从式(4)和式(5)可以看出,在一个采样时间间隔后,可以由给定的环路自然角频率ωn和环路阻尼因子ξ来共同确定环路滤波器的系数。

4.2.3 复用/优化设计思想

非扩频模式下,考虑到BPSK信号与QPSK信号解调模型中很多的功能模块的结构相同,在软件设计上考虑复用设计。

1)低通滤波器

要实现多模数字解调功能,最直接的思路是设计多个低通滤波器。通过后续的工程实践发现:在所有功能模块的设计中,滤波器耗费逻辑资源最多。本文采用的方案是结合Matlab FDATool和FIR滤波器IP core对低通滤波器进行复用设计或者融合设计。当两种解调模式中的时钟和采样率都是码速率的某一整数倍时,两种调制模式可以考虑完全复用;当采样率不是码速率的同一整数倍时,在设计低通滤波器时可以考虑融合设计。仅设计一个低通滤波器时,先利用Matlab FDATool设计阶数相同的滤波器系数,再通过模式选择相应的系数组来实现预期的滤波功能;ISE中提供的用来实现FIR滤波器的IP core(fir_compiler V3.2)最高的采样时钟可达250 MHz;如此设计的滤波器还可同时完成整数倍插值和抽取,内部可实现多通道配置,完全能满足设计需要。

2)压控振荡器

设计一个压控振荡器,通过模式选择信号对NCO的三种模式下的频率控制字做选择,而非单独设计。ISE中提供的用来实现DDS的IP core(dds_compiler v2.1)最高工作时钟可达550 M;输出的正/余弦信号动态范围为:18~120 dB,对应的有效位数为3~21 bit;频率分辨率范围为:0.0233 Hz~10 kHz;两者都能在其范围内实现自主配置以适应不同的需求;内部提供频率偏移和相位偏移的可编程设计,具有较高的通用性。

(3)环路滤波器

将环路滤波器中的两个系数的乘法运算优化为数据移位运算。图7说明了环路滤波器在软件中的实现过程。在复用过程中,将LF的输入信号通过上位机选择不同的移位位数代替各自的相乘功能,累加器可以通过一个加法器和一个D触发器来实现。

图7 环路滤波器的优化设计Fig.7 The optimization of loop filter

其中K1≈log2C1、K2≈log2C2

图8表示的是非扩频模式下两种PSK信号的解调软件的实现过程,其中的相关部件考虑复用或者优化处理。

虚线框内的部分表示的数字下变频部分,三种模式下该部分功能完全复用。上位机软件通过模式选择信号通知NCO、低通滤波器、鉴相器、环路滤波器等部件选择对应的参数组或相对应的功能模式完成非扩模式下的两种PSK信号解调。

4.2.4 设计思路对比

如果采用传统的设计思路,即低通滤波器、压控振荡器、环路滤波器等都采用采用独立设计,并且在算法上不做任何优化设计,纯源码实现占据300万门FPGA逻辑资源的71%;而采用模块复用+优化设计思路,纯源码实现只占FPGA的46%。

4.2.5 在线测试与分析

主要就以下三个指标对多体制中频接收机进行整机测试:

图8 非扩频模式软件设计框图Fig.8 The FPGA structure of DBPSK/DQPSK demodulation

1)可捕获跟踪的中频信号频率范围测试;

2)解调系统的抗干扰能力测试:在中频信号中混入不同信噪比的加性白噪声,在保证一定误码率水平的情况下确定解调系统所能够承受的信噪比下限;

3)接收的中频动态范围即无噪声中频信号的功率范围测试。

表4、5、6分别给出了三种性能的测试结果。

表4 不同模式/参数下的中频频率捕获跟踪范围Table 4 The IF frequency capture&trace range under different modes/parameters

表5 不同模式/参数下的解调损耗Table 5 The demodulation loss under differentmode/parameter

表6 不同模式/参数下的中频接收动态范围Table 6 The IF receiving dynamic range under different modes/parameters

分析三表测试结果,可以发现在扩频模式下,中频频率捕获跟踪范围大于13 kHz,非扩频模式下,中频频率捕获跟踪范围都维持在符号速率的±3%以上。对于空间通信来说,在同时考虑到多普勒频移和发射机发射频率精度的情况下,该测试结果有足够大的裕量;抗干扰的测试结果中,没有引入RS解码时,解调损耗都在3.5 dB以下,扩频模式由于解扩带来了一定的损耗;如果引入RS解码模块,解调损耗将进一步减小1.5~2 dB。对于中频接收动态范围测试,接收信号功率过大,会引起AD过幅,导致其有效位数降低;信号功率过小,信号无法被检测到,动态范围就是指这个最大最小的范围。影响中频接收动态范围的主要有:ADC的量化精度、各功能模块增益分配等。如果接收机前端引入自动增益控制模块,动态范围能得到进一步的扩展。

5 结论

多体制接收机作为空空通信子系统中的核心部件,将在载人航天新一期的交会对接任务中扮演关键角色。文章基于软件无线电技术结合型号的现实需求,研究并实现了一种模式可切换的全数字化多体制中频接收机。从功能模块化、平台通用化和具有继承性的角度出发,在常规设计方法的基础上提出了复用/优化设计方法,减少了FPGA逻辑资源的使用,提高了算法的可移植性,丰富了接收机的解调功能。还重点对接收机的中频频率跟踪性能、抗噪声性能和中频接收动态范围等表征接收机重要性能的指标进行了定量评估和分析,验证了该全数字多体制中频接收机的功能与指标,测试结果表明该多体制接收机能够满足型号任务需求。

[1] 石云墀.载人航天空空子系统及其关键技术[J].上海航天,2011,38(6):38⁃42.

[2] 洪振宏.高码速率QPSK解调器载波恢复环的算法与实现[D].北京:中国科学院空间科学与应用研究中心,2007.

[3] 樊昌信,曹丽娜.通信原理[M].第6版.北京:国防工业出版社,2006.

[4] Analog Device.AD6645 data sheet[EB/OL].2008.ht⁃tp://www.analog.com/en/analog⁃to⁃digital⁃converters/ad⁃converter/ad6645/products/product.html.

[5] Xilinx Inc.Virtex⁃ii XC2V3000 data sheet[EB/OL].2001. http://www.xilinx.com/support/index.html/cont ent/xil⁃inx/en/supportNav/silicon_devices/mature_and_discontinued_products/virtex⁃ii.html.

[6] 杨小牛,楼才义,徐建良.软件无线电技术与应用[M].北京:北京理工大学出版社,2010.

[7] Floyd M.Gardner.锁相环技术[M].姚剑清译.第3版.北京:人民邮电出版社,2007.

[8] John G.Proakis.数字通信[M].张力军等,译.第四版.北京:电子工业出版社,2010.

The Design and Implementation of Multi⁃mode Receiver for Rendezvous and Docking in Space

CHENG Qinglin,HONG Liang,WU Yijie,SHI Yunchi

(Shanghai Institute of Aerospace Electronic Technology,Shanghai201109,China)

During the manned spaceflight mission,space to space communication system is responsible for the information exchange between two spacecrafts at the rendezvous and docking and evacuation stages.For different mission stages,different communications modes are required.In order to fulfill the different mission requirements in the same hardware,the feature of various demodulation modes and algorithm was analyzed,and full digital demodulation algorithm and hardware design were determined based on software radio technology.A method of restructure and multiplex was used to optimize the design,which leads to less logical resource and decreasing algorithm complexity.The result of the test for the system indicted that the key characteristic of the design could meet the specification of the space to space communication system.

multi⁃modes;digital receiver;space to space communication system;rendezvous and docking

V443+.1;V526

文章编号:1674⁃5825(2014)01⁃0058⁃07

2013⁃07⁃01;

2013⁃12⁃27

程庆林(1987⁃),男,硕士研究生,研究方向为软件无线电技术。E⁃mail:cnhbcql@126.com