数字设计中基本电路评价方法研究

张 鹰,姜书艳,陈德军,卢有亮,崔琳莉

(电子科技大学数字逻辑设计及应用课程组,四川成都 611731)

数字电路设计中评价电路结构优劣的早期标准可以表达为尽量减少晶体管的使用量。现在已体现为满足功能要求下采用尽可能少的通用集成块。基于FPGA的设计希望使用最少的逻辑单元,得到最高的时钟频率(或最短的时间延迟),而VLSI设计则需要考虑集成度、速度和功耗的综合优化。从数字技术的发展来看,最受关注的当属集成度问题:如何使集成电路面积更小已成为设计的第一目标。目前数字集成主要采用CMOS工艺,以平面器件形成电路,每个器件占据一定的芯片面积。设计人员要考虑减小电路的面积,需要从器件规模开始。

目前的“数字电路”课程在处理这一问题时,没有对电路评价建立相关模型,导致逻辑优化设计与功能器件设计缺乏统一的设计标准,不能适应飞速发展的设计要求。

1 MOS晶体管的电学参数模型

1.1 MOS晶体管的简单模型

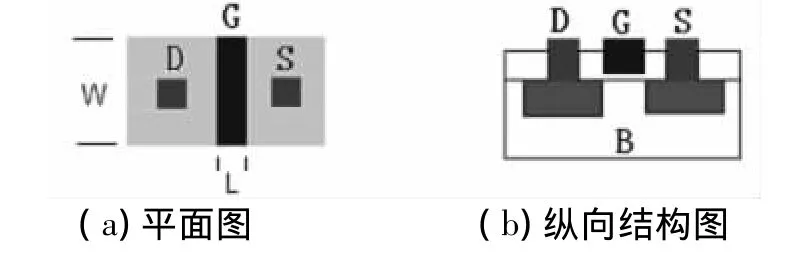

在CMOS工艺条件下,电路逻辑结构由MOS晶体管担任开关作用来实现。作为平面器件,MOS晶体管的简单模型如图1所示。

图1 MOS晶体管的简单模型

图1(a)所示的晶MOS体管平面为一个矩形区域,分为漏(D)、栅(G)和源(S)三个区域。各区电极引出均通过接触孔连接到上层(布线层),器件的相互连接由上层的多层布线实现,不占用额外面积。从图2(b)的纵向结构看,G与其他极被绝缘层阻断;衬底B与D/S之间存在PN结耗尽区阻断,D与S间为高阻状态(断开);当G和B处于不同电平时,G可以通过电场吸引载流子到G区下面聚集,形成导电沟道,使得D与S间变为低阻状态(导通)。

对于导电沟道中电流流动方向称为沟道长度(L),与之垂直的方向为沟道宽度(W);在大规模数字集成设计中,通常L受工艺线宽影响,保持为容许的最小值;此时器件的面积与W成正比。可以将最小晶体管的面积作为面积单位。即使在导通的情况下,沟道也存在一定电阻,该电阻与沟道宽度W成反比。当D/S/G电平状态与B不同时,隔离区会存在电荷聚集,表现出电容现象;各极的电容与相应面积有关,表现为与W成正比。

在简单模型中,可以认为同一晶体管中D极电容与S极电容相同;根据VLSI工艺中的实际情况,可以假定D极电容为G极电容的2倍。因此可以将最小晶体管的G极电容作为最小电容单位。MOS器件可以分为PMOS和NMOS两类,使用的载流子各不相同。随着集成电路工艺的发展,两者在尺度与性能上的差异正日渐缩小。本文对简单模型忽略这些差异,在后续分析中,将扇入相同的NAND和NOR器件视为同等性能的器件。

1.2 基本逻辑器件的结构与参数分析

目前最常用的基本数字逻辑单元是采用MOS器件互补连接形成,一些典型结构如图2所示。这些结构在通常的数字电路教材中均有详细描述。

图2 MOS器件互补连接的典型结构

这种逻辑结构的特点为:每个输入控制2个晶体管(1个P型和1个N型);N型晶体管串联构成AND运算,并联构成OR运算;P型晶体管采用与N型对偶方式连接;每个器件输出均为反相输出。

值得一提的是,与或非/或与非AOI/OAI(ANDOR-INVERTOR/OR-AND-INVERTOR)结构可以采用支路的串/并联表达与/或运算,因此在多级与或结构表达中,除了第1级的实际输入端需要连接晶体管外,后级运算都不需要采用晶体管。这种设计可以节约晶体管数量,在基于晶体管设计的时代,曾经成为一种重要的设计结构。

当晶体管连接成互补逻辑器件时,器件的输入端都连接到晶体管的G极,该G极电容之和构成器件的输入电容;器件的输出端通过导通支路连接电源形成输出,导通支路上的电阻构成器件的输出电阻,而与输出支路连接的有可能发生状态变化的电容(D极电容和S极电容)构成器件输出电容。

2 互补逻辑的最小设计及评价方法

逻辑单元电路的评价主要关心其逻辑面积、延迟时间和功耗。逻辑面积为构成该电路的各晶体管面积的总和。延迟时间可以由电路时间常数RC表达;在最小设计中,导通电阻R被驱动能力限定为固定值,延迟时间可以单纯由电容大小表征;涉及的电容应为在信号传递中可能发生状态变化的输入电容和输出电容。CMOS电路功耗主要为动态功耗,也与电路中可能发生状态变化的电容大小成正比。

为了得到最大限度的集成效果,电路设计应该在保障最小驱动能力条件下,采用最小尺度设计方案,也就是采用最小宽度或最大输出电阻设计方案。在此方案中,要求所有导电通道的输出电阻均保持为统一最大值(在驱动能力容许的条件下)。

最简单的逻辑器件是反相器。最小反相器可以采用2个最小晶体管连接形成。该反相器具有最低驱动能力限制下的最大输出电阻。以最小晶体管面积为基本单位,该反相器面积为2。以最小晶体管G极电容为基本单位,反相器输入电容为2,输出电容为4。由于延迟时间可用电容大小表达,因此该反相器的延迟时间为6。功耗也与之成正比。

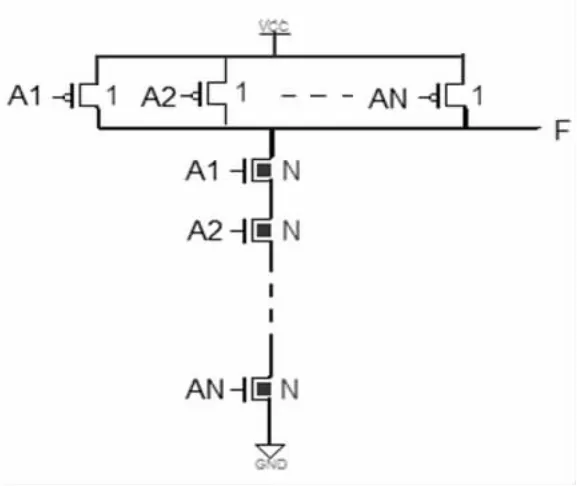

多输入逻辑器件中最基本的是与非和或非(NAND和NOR),分别采用晶体管的并联和串联形成逻辑结构。图3为NAND(N)的结构形式。

图3 与非门NAND(N)的结构形式

当晶体管形成串联支路时,导通电阻串联会导致电阻增大;为了保持输出电阻的最大限制,需要加宽晶体管沟道以减小每个晶体管的导通电阻。容易看出,若一条支路上有N个晶体管串联,则需要将每个晶体管的宽度加大N倍。由于串联支路的晶体管数量与逻辑单元输入端数量(扇入)相同,器件的逻辑面积与扇入数有关。由图3可见,并联支路中可以采用最小晶体管,而串联支路中每个晶体管面积都为最小晶体管的N倍。由此可以得到扇入数与逻辑面积的关系为

晶体管逻辑宽度增加也会导致各极的电容增加,在考虑信号传递时可能变化状态的电容时,可以由图3看出,输入电容与输出电容均与扇入相关:

由此可见,电路的扇入增加将导致逻辑面积和延迟时间的急剧增加,大扇入器件是不可取的。

利用上述分析方法也可以分析与或非门(AOI)结构的逻辑面积和延迟时间。由于AOI结构中导通支路通常都存在串联现象,所有晶体管都需要不同尺度的加大,导致逻辑面积和延迟时间集聚增加。因此在集成电路设计中,几乎不采用AOI结构。此项分析可以作为课程设计内容交给学生去完成(各自选择不同的AOI结构进行分析,并与相同逻辑的NAND-NAND结构的结果进行比较)。

3 评价方法的应用

3.1 CMOS中的基本逻辑器件的应用

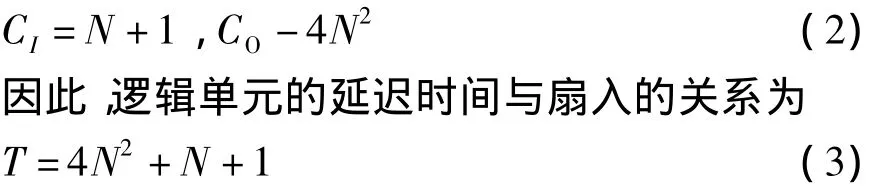

根据上述分析,大扇入器件占用逻辑面积大,延迟时间长,不适合在集成电路中采用。利用基本逻辑定理(结合律和德摩根定理),可以将大扇入的NAND/NOR分解为小扇入器件的组合。在图4中表达了对于4输入NOR的分解。

图4 对于4输入或非门的分解

由图4可以看出,一旦扇入达到4以上,就应通过分解获得更好的性能。因此,数字集成电路中的基本逻辑器件只应包含5种器件:反相器、2输入NAND/NOR、3输入 NAND/NOR。此外,传输门(TG)也可以作为基本器件用于一些特定的电路中。

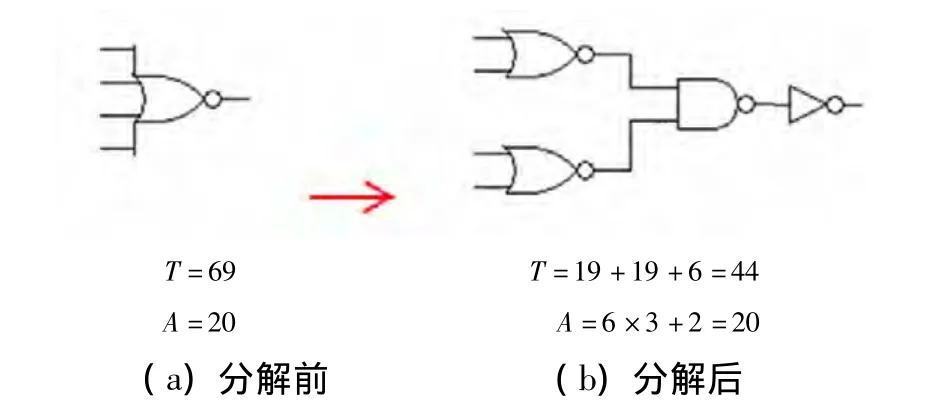

3.2 输出单元设计的应用

集成电路系统输出单元通常需要强大的对外驱动能力(mA级)。通过加大直接输出器件的宽度可以使驱动能力增加,但这种增加会使输出器件的逻辑面积和延迟时间成正比增加。为了尽量实现最小化设计,通常采用反相器组合成输出缓冲器件实现输出,一种典型的输出缓冲设计如图5所示。

图5 典型的输出缓冲设计

由该图可以看出,采用逐渐扩大驱动能力的缓冲方式,能够在增加成本不多的条件下,将延迟时间大幅度减少。这已成为集成器件输出单元的标准设计方式。

4 结语

本文经过对典型CMOS电路结构的分析和MOS晶体管参数的分析,考虑到电路驱动能力对集成度的影响,按照最小设计方式,对逻辑单元电路的输出电阻实现统一的最大值设计。笔者根据该设计方式,得到了器件扇入与逻辑面积、输入/输出电容、延迟时间和功耗之间的关系。这些关系可以构成对于基本电路单元的评价。利用该评价,可以得出基本电路单元扇入应小于4的结论。

[1]叶佳卓,卢斌,程栋.基于EDA技术的数字电路实践教学探讨[J].北京:实验技术与管理,2010,27(11):249-252

[2]魏坚华,贾熹滨.基于EDA技术推进数字逻辑课程改革和精品课程建设[J].北京:计算机教育,2011,16:41-43

[3]朱正伟,周炯如.EDA技术在硬件课程体系教学改革中的应用[J].南京:电气电子教学学报,2010,32(6):23-25

[4]陈进,吴柯.从一个工程实例对“数字电路”教学的反思[J].南京:电气电子教学学报,2012,34(2):112-114

[5]颜雪松,樊媛媛等.数字逻辑课程设计的教学探索[J].北京:中国科教创新导刊,2008,8:31-31

[6]俎云霄,王卫东.基于课程群的电子信息类专业基础课教学改革[J].北京:现代教育技术,2OlO,20(13):34-36

[7]施键兰,赵芮,黄文秀,李冬芬.《数字逻辑》课程教学改革的探索[J].广州:现代计算机:下半月版,2011,19:45-47