LTE 系统下行链路FDRX 节能机制研究

蔡卫红,欧红玉

(湖南邮电职业技术学院,湖南长沙410015)

本文FDRX 节能策略以下行链路分组包数据传输时单一UE 功率节省为目的,以便降低电量消耗及延迟时间来满足QoS 需求[1-2]。其策略分为两个阶段:第一阶段为流量预估和数据信息收集。其中流量预估是根据分组包到达时间间隔与延迟时间来进行[3]。而数据信息收集,若为VoIP 流量类型,则会利用分组包到达时间间隔数据信息;若是非VoIP 流量类型,则会利用UE 目前所使用DRX cycle 数值,再将此数值作为第二阶段模糊逻辑控制器所需Input 值,即采用模糊逻辑理论,借由第一阶段数值作为Input 值,再结合模糊逻辑控制器以得到最佳DRX cycle 参数值,并将此参数值传给UE,让UE 使用在下一时间段的DRX模式中。

1 流量预估

延迟时间属于QoS 参数之一,不同服务类型有不同QoS 需求。延迟时间通常包括:处理延迟时间、排队延迟时间、传输延迟时间、广播延迟时间等多种情况。延迟时间太长可能导致分组包在eNB buffer 中丢失,导致分组包遗失率增加,进而造成用户满意度降低。eNB 收集每个分组包所产生延迟时间作为延迟时间数据信息。因eNB 已知UE 的DRX mode,故可推测出分组包延迟时间,其延迟时间的计算是从某分组包到达eNB 那一刻开始算起,直到此分组包传给UE并接收完为止,如图1 所示。eNB 通过这些延迟时间数据信息与历史延迟时间进行流量预估来计算出平均延迟时间数据,而此数据会用来推估下一段时间DRX cycle 参数。

为推估出DRX cycle 参数需将延迟时间数值用于第二阶段Input 值,进而应对下一阶段的流量传输,如图2 所示。图中的历史延迟时间表示之前已收集的平均延迟时间。此部分计算延迟时间数值会大大影响第二阶段结果。

分组包到达时间间隔也是由eNB 收集,eNB 再通过这些分组包到达时间间隔与历史分组包到达时间间隔值来进行流量预估并计算出平均分组包到达率,并将此数值用于第二阶段的Input 值,进而应对下一段时间的流量传输,如图1 与图2 所示。图中的历史分组包到达时间间隔值表示之前已收集且平均的分组包到达率。

图1 延迟时间于分组包到达时间间隔说明图

图2 流量预估流程图

2 模糊逻辑控制器

当UE 分组包延迟时间过长导致不满足QoS 需求,此时需通过缩短DRX cycle 长度来减少延迟时间。而DRX cycle 设定多长才算短,则通过模糊逻辑控制理论加经验的判断进行,即通过不断实验的结果来调整模糊逻辑控制器内参数值,使模糊逻辑控制器输出最佳DRX cycle 参数值[4-5]。从最初步骤的模糊化到最后步骤的去模糊化过程中,利用相关推理引擎结合模糊逻辑规则来模拟人类决策,并通过近似准确的数据来找到解决方案。模糊逻辑控制器流程如下:

第一步:将延迟时间数值及分组包到达率或当前DRX cycle 数值一起输入到模糊逻辑控制器进行模拟化[6]。分组包到达率适用于流量类型为即时服务VoIP业务,若流量类型为非即时服务业务,则会使用该UE当前DRX cycle 数值。流量类型在进入模糊逻辑控制器之前进行判断[7]。模糊化方法通过隶属函数,其参数值都是通过QoS 信息及不断实验调整所得到的结果,如图3 及图4 所示。

图3 水平轴为延迟时间Input Variable,其模糊值定义为Extremely Short、Short、Middle、Long、Extremely Long五种长度,分别设定为:50 ms 内、25 ms 至100 ms、75 ms至150 ms、12 ms至300 ms、250 ms 以上。

图3 Input Variable 延迟时间

图4 水平轴为分组包达到率当前DRX cycle 的Input Variable, 其 模 糊 值 定 义 为Extremely Short、Short、Middle、Long、Very Long 与Extremely Long 六种长度,分别设定为:40 ms 内、20 ms 至80 ms、40 ms至160 ms、80 ms至320 ms、256 ms 至640 ms、512 ms 至2560 ms。当Input 值转变为模糊值后进入第二步。

图4 Input Variable 分组包到达率当前DRX cycle

第二步:将第一步模拟化输出值在推理引擎中结合模糊逻辑规则进行推理与对应。推理引擎,即将第一步所得模糊值与模糊逻辑规则进行对应,并通过不断实验、经验及QoS 需求中的最大可延迟时间来制定出10 条模糊逻辑规则,如表1 所示。首先表1 中有两种流量类型,第一种为非即时服务,如网页浏览、文件传输等,其最大延迟时间为300 ms。另一种为即时性服务,主要以VoIP 为主,其最大可延迟时间为100 ms。eNB 在接收到该UE 的数据流量时,就已知其流量类型,在模糊逻辑规则中加入流量类型是为了使模糊逻辑控制器能方便地去处理。在延迟时间部分则与第一步骤延迟时间的Input Variable 相同,有Extremely Short、Short、Middle、Long、Extremely Long 共5种长度。在DRX Cycle 部分,“+1”“0”“- 1”“- 2”分别指的是当前DRX cycle 长度拉长一个状态、DRX cycle长度不改变、DRX cycle 长度缩短一个状态、DRX cycle 长度缩短两个状态。DRX cycle 的长度状态分别为Extremely Short、Short、Middle、Long、Very Long 及Extremely Long 共六种状态。

举例如下:假设流量类型为非即时服务和延迟时间为Short,且假设通过第一步取得DRX cycle 的长度为Short,则推理引擎对应模糊逻辑规则会产生出“+1” 的值,DRX cycle 长度会从Short 拉长一个状态变为Middle,此Middle 即输出DRX cycle 的模糊值。

表1 模糊逻辑的规则表

第三步:将推理引擎所得输出值再进行去模糊化步骤获得最佳DRX cycle 参数值。第三步是将上一步所输出的DRX cycle 模糊值进行去模糊化动作,而去模糊化方法就是将DRX cycle 模糊值去对应DRX cycle 的Output Variable,而此DRX cycle 的Output Variable 定义与设定都与图4 完全相同。当DRX cycle 模糊值转变为DRX cycle 参数值后就进行输出,并将此参数值传给UE,让UE 当作下一段时间的DRX mode。

模糊逻辑控制器的目的是选择最佳DRX cycle参数值,并将此参数值提供给UE 作为下一段时间的DRX mode,让DRX 机制能达到最低限度省电及减少延迟时间来满足QoS 需求。

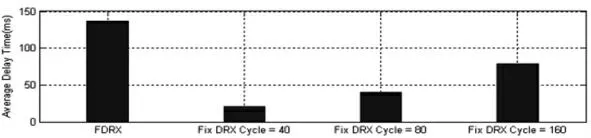

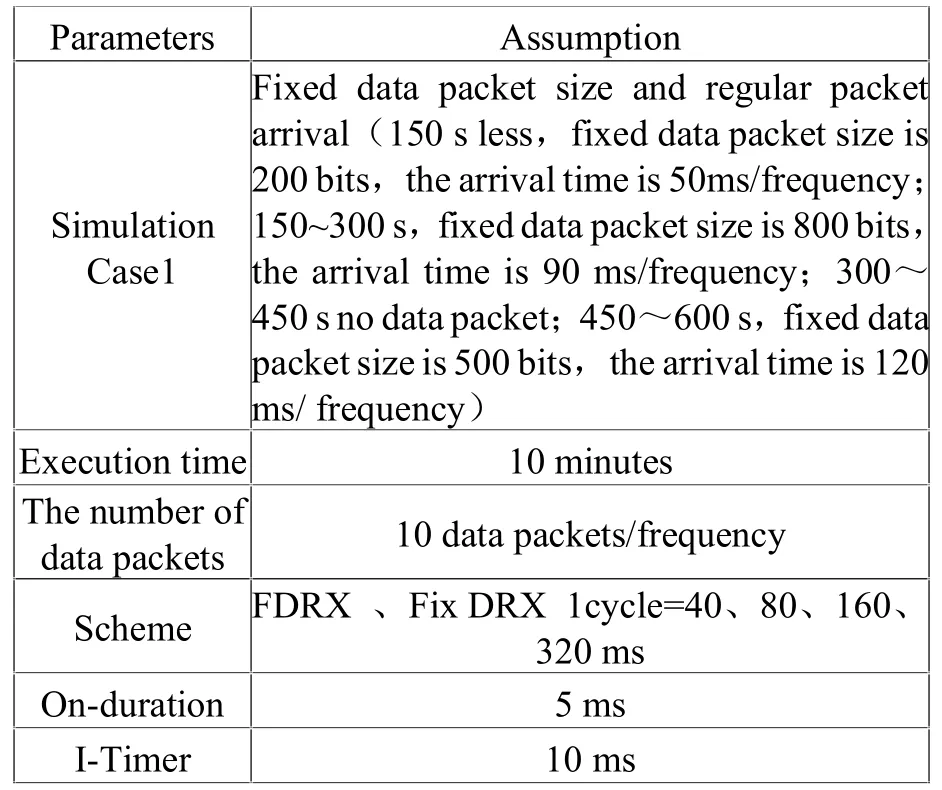

3 模拟仿真

Case1 实验参数设定如表2 所示。其模拟仿真以非即时服务为主,随机乱数方式产生分组包大小与分组包到达时间。UE 的DRX 机制以3000 ms 为单位共执行200 次,共执行10 分钟,随机乱数产生1 至10个数据分组包/ 次,比较使用固定DRX cycle 长度分别为40 ms、80 ms、160 ms 及本文所提出的FDRX 方法共4 个对象。On- duration 参数值固定为5 ms,以及I- Timer 参数值固定为10 ms。

表2 FDRX Case1 参数设定

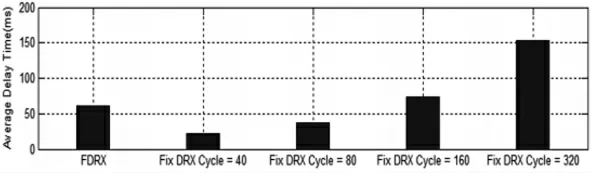

模拟结果分别如图5 及图6 所示。图5 为电量消耗仿真比较,数值越小越好,图6 为平均延迟时间仿真比较,也是数值越小越好,更能满足QoS 需求。从图5 及图6 可看出,FDRX 方法与其它比较对象相比,电量消耗最低,所以最优。虽然其余比较对象的分组包传输延迟时间比FDRX 方法要低,但是它们的电量消耗大幅增加,由于仿真实验以浏览网页或文件传输的QoS 需求最大延迟时间为300 ms,在满足较低延迟时间等QoS 需求下,为达到最低电量消耗,FDRX 方法最优。

图5 FDRX Case1 的Energy Consumption 比较图

图6 FDRX Case1 的Average Delay Time 比较图

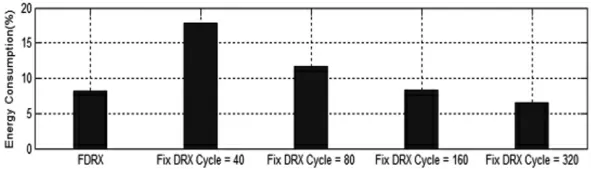

Case 2 仿真参数设定如表3 所示。其模拟仿真以即时服务VoIP 为主,并固定分组包大小和规律性时间到达,分组包到达时间为150 s 以内的分组包大小固定为200 bits,50 ms 传输一次;分组包到达时间为150 s 到300 s 间的分组包大小固定为800 bits,90 ms传输一次;分组包到达时间为300 s 到450 s 间无分组包传输;分组包到达时间为450 s 到600 s 间的分组包大小固定为500 bits,120 ms 传输一次。UE 的DRX 机制是以3000 ms 为单位共执行200 次,共执行10 分钟,分组包数量10 个/ 次,比较对象为使用固定DRX cycle 长度分别为40 ms、80 ms、160 ms、320 ms 及本文所提出的FDRX 方法共5 个对象。On- duration 参数值固定为5 ms,以及I- Timer 参数值固定为10 ms。

表3 FDRX Case2 实验参数表

模拟仿真结果如图7 至图9 所示。图7 为电量消耗仿真比较,其数值越小越好。图8 为平均延迟时间仿真比较,也是数值越小越好,越能满足QoS 需求。图9 为FDRX 方法与比较对象的效能比较图,其数值越高表示效能越好。本文提出的FDRX 方法以减少电量消耗为主,延迟时间仅需满足QoS 需求。在图7 至图9 中,FDRX 方法的电量消耗与平均延迟时间都不是最好,因需满足QoS 需求,如以电量消耗为最好,容易导致延迟时间增长,进而不满足QoS 需求。如Fix DRX cycle 为320 ms 时其电量消耗虽然最低,但其延迟时间最高,且大于VoIP 在QoS 需求中的最大可延迟时间。反之若要延迟时间最低,则容易导致电量消耗最高,如Fix DRX cycle 为40 ms 时。所以本文提出的FDRX 方法有较低的电量消耗及延迟时间满足QoS 需求,从图9 效能比较图可看出比其他策略更为优异。

图7 FDRX Case2 的Energy Consumption 比较图

图8 FDRX Case2 的Average Delay Time 比较图

图9 FDRX Case2 效能比较图

4 总结

从Case 1 和Case 2 的模拟仿真针对不同的业务服务类型进行测试,其结果发现使用FDRX 方法其效能比其他比较对象的效能还要好,但是若在模糊逻辑控制器的参数方面进行调整,以及增加多种不同的Input 值,就可使此方法适用在更多不同的应用上,再加上此方法可动态去调整DRX cycle,优势明显。