广义多相滤波及其应用

(中国电子科技集团公司第三十八研究所,安徽合肥230088)

0 引言

在雷达、电子对抗、成像等系统的应用中,数字接收机面临着带宽不断加大的挑战,这同时给模数变换器件(ADC)和数字信号处理器件带来了很大困难。随着ADC技术的高速发展,数字信号处理器件对数字接收机带宽的制约尤为明显。多相滤波理论的提出有效缓解了数字信号处理器件对宽带数字化接收的制约,其滤波器位于抽取器之后,即滤波是在降速之后进行的,这就大大降低了对器件处理速度的要求,提高了系统的实时处理能力[1-2]。多相滤波的本质是,在进行数字滤波的同时实现了抽取。多相滤波之所以能够提高系统的实时处理能力,也正是由于这种同时进行的“抽取”操作,可以说,抽取是多相滤波的“牛鼻子”。

传统多相滤波算法将滤波处理的速度降为输入信号速度的1/D(D为多相分解的阶数),并实现了D倍抽取,即多相分解的阶数与抽取比是一致的[3]。在工程实践中,这只是情形之一,另一个经常遇到的情形是,多相分解的阶数与所需的抽取比并不一致。笔者在研究传统多相滤波算法的基础上,试图通过一种“广义多相滤波”的概念,为这两种情形找到一种统一的表述方式,即,使得多相滤波在实现D倍降速(D为多相分解的阶数)的同时进行K倍抽取(K为抽取比,D=K或者D≠K)。

1 广义多相滤波

在使用多相滤波时,人们对输入数据进行多相分解,并对多相分解后的各路数据进行分支滤波,以此实现所需处理速度的下降,如图1所示,虚线框内即为多相分解的过程[4]。在宽带数字接收的工程实际中,ADC采样后得到的高速数字信号在进入数字信号处理器件时往往需要进行串并转换,这一串并转换过程正好实现了多相滤波所需的多相分解操作[5]。

图1 传统多相滤波过程

一般而言,多相分解的“阶数”由两个因素决定,一是数字信号处理器件的处理速度,二是实现多相分解的硬件结构。第一个因素顺理成章,这里对第二个因素举例说明。

某L波段数字接收机,需要对中心频率1 200 MHz、带宽300 MHz的信号进行直接采样和数字下变频,使用现场可编程门阵列(FPGA)作为数字信号处理器件,在FPGA中对ADC送来的高速数字信号进行串并转换。为了减少芯片输出引脚数,便于板级集成,ADC输出的高速数据采用DDR格式,在这一前提下,集成在该FPGA中的串并转换器,其转换比只能是固定的4,6,8三种。设计者别无选择,只能进行这三种阶数的多相分解,这就是多相分解的阶数受实际硬件结构影响的典型情形。

对于一个多速率信号处理系统,其抽取比主要由采样率和信号带宽决定,比如在上述数字接收机中,当采样率为960 MHz时,抽取比不能超过3,否则便不能满足系统带宽对输出信号速率的需求。当然,人们可以通过将串并转换后的数据再进行并串转换的方式来实现数据的“提速”,可是这意味着系统需要更高速度的数字信号处理器件。

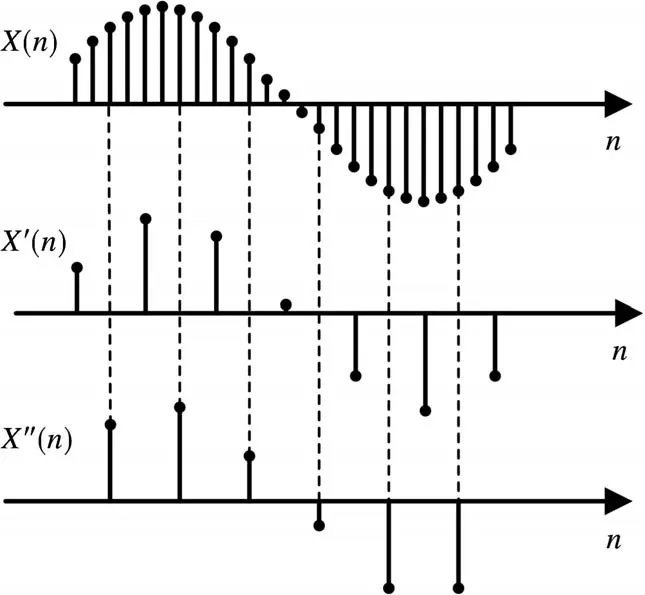

针对这里遇到的多相分解的阶数D与抽取比K不一致的情形,笔者设想,为了实现对D阶多相分解数据的K倍抽取(K≤D、P=D/K为正整数),可以在传统多相滤波的基础上进行P-1倍“补相”操作,使其输出为并行的P路数据。如图2所示,图中X′(n)为抽取结果,X″(n)为补相结果,只需找出X′(n)和X″(n)的关系即可由传统多相滤波的结果得到各路补相输出,从而达到进行K倍抽取(K≤D)的目的。

图2 “补相”示意图

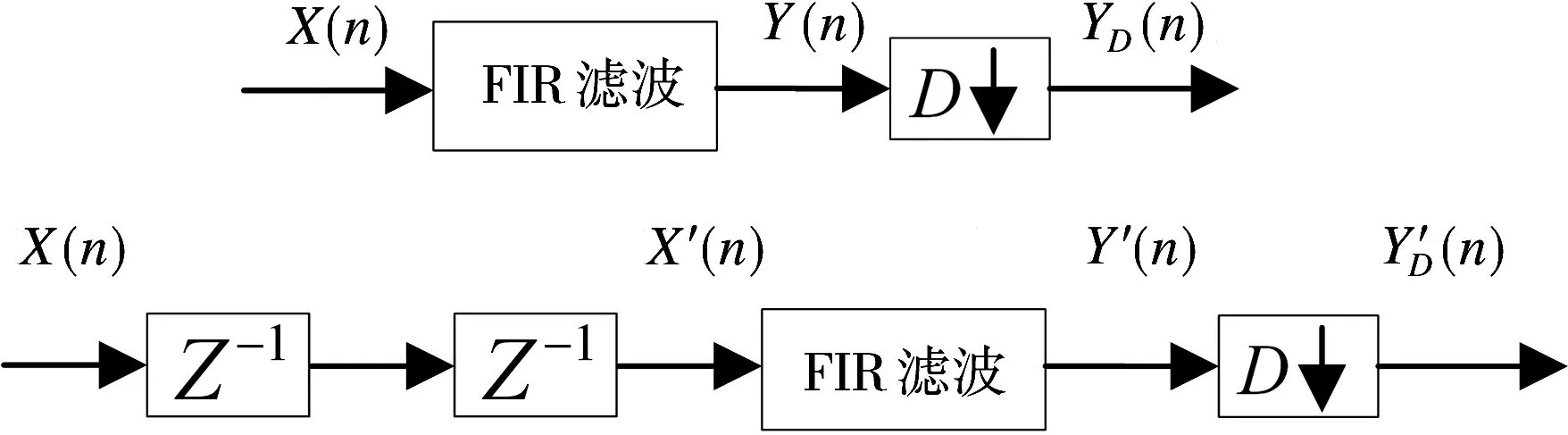

我们首先从频域考察如图3所示的两个过程。

图3 滤波抽取及延迟后滤波抽取过程

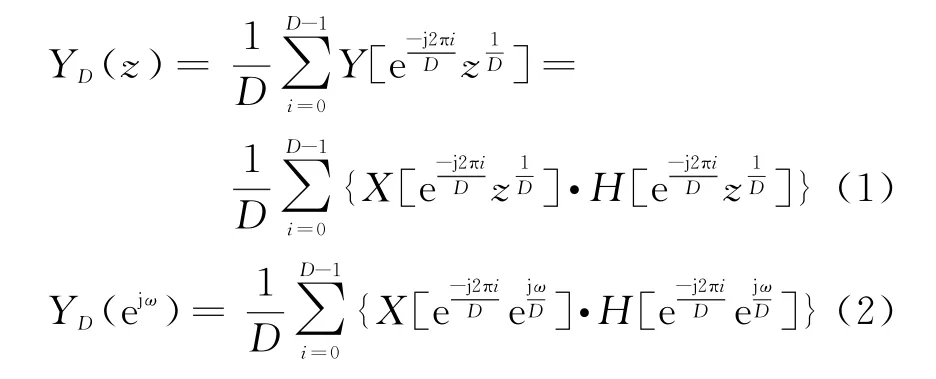

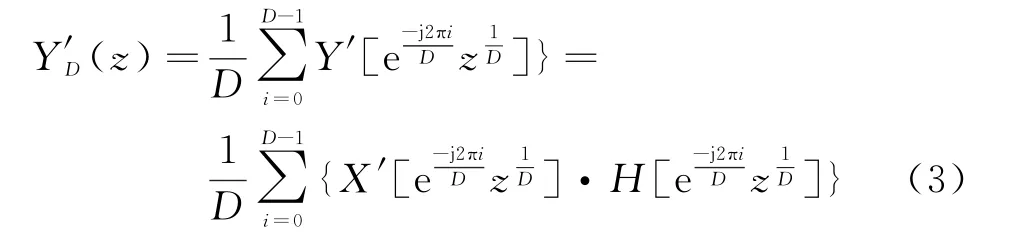

假设图中X(n),Y(n),Y D(n),X′(n),Y′(n),Y′D(n)的z变换分别为X(z),Y(z),Y D(z),X′(z),Y′(z),Y′D(z),其 傅 里 叶 变 换 分 别 为X(ejω),Y(ejω),Y D(ejω),X′(ejω),Y′(ejω),Y′D(ejω),并设图中FIR滤波器的单位脉冲响应为H(n),其z变换、傅里叶变换分别为H(z),H(ejω),则

而X′(z)=X(z)z-N,代入上式,可得

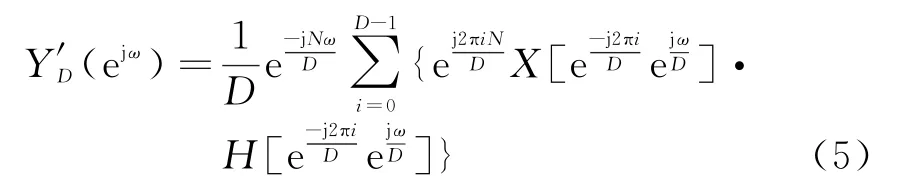

因此Y′D(n)的傅里叶变换为

考虑其傅里叶变换的周期性,可以只关注(-π,π)之间的频谱,即令i=0,同时省去常数因子,此时

将N=K∗i(K为抽取比)代入式(6)中,即可得到,第i路补相输出的频谱为普通多相滤波输出乘以,这本质上就是一个相移的过程,将这一过程与分支滤波过程的顺序进行颠倒,即可得到如图4所示的结构。如前所述,虚线框中的过程由数字信号处理器件的串并转换器完成。

图4 多相滤波的第i路补相输出频谱(i=0,1,…,P-1)

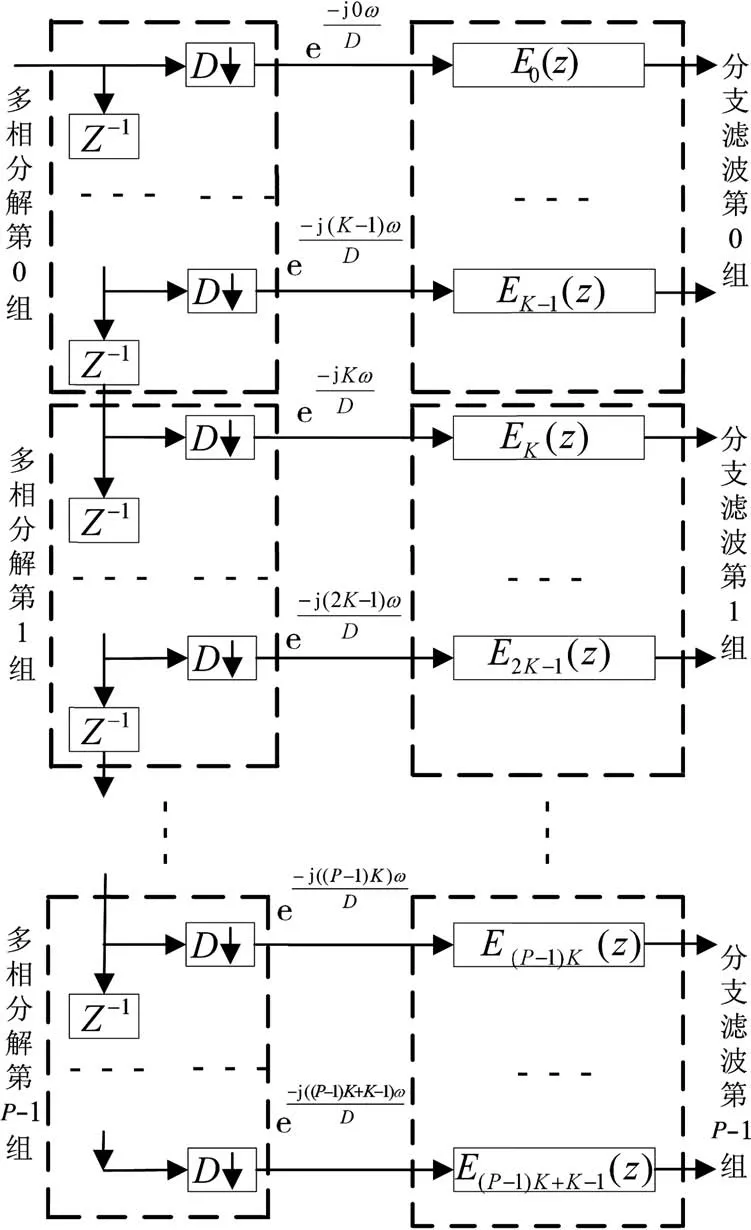

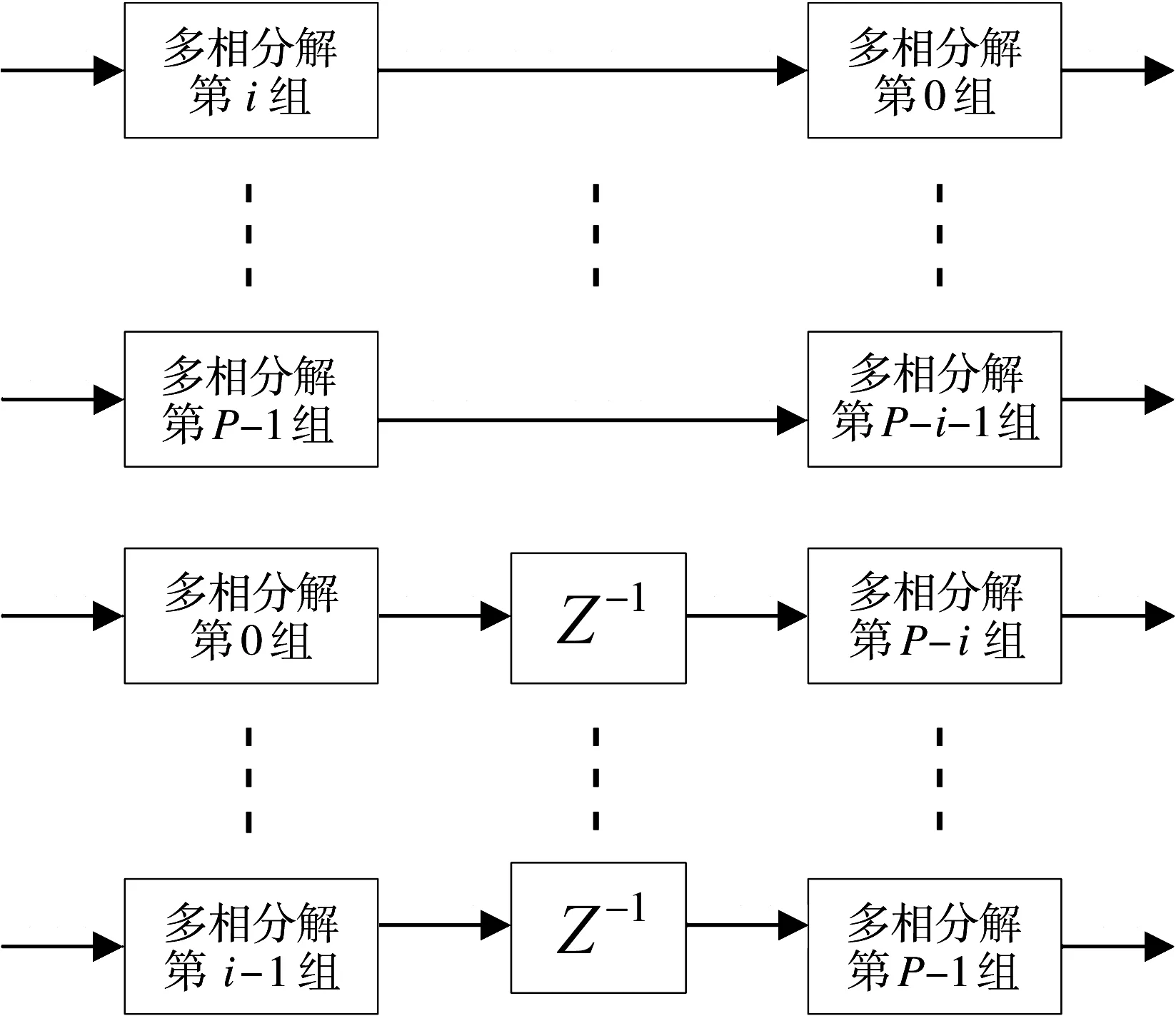

为了探求图4所述滤波处理结构的实现途径,考察传统多相分解得到的分支数据的频谱,分别将多相分解及随后的分支滤波分为P组,每组K个分支(K=D/P),如图5所示,其中,每个分支数据的频谱如图中所述。由图5可知,为了得到图4所述结构的处理结果,可以将多相分解的分组结果和分支滤波的分组结果重新进行组合,并对部分分支进行一个节拍延迟,再进行对应分支滤波,如图6所示。

图5 多相滤波的分组及频谱

图6 第i路补相结果的产生

由此可得到广义多相滤波的具体步骤如下:

a) 进行传统多相分解。

b) 将多相分解的结果分为P组,每组K个分支。

c) 将分组结果按图6所示顺序重新组合,将部分分组(如图6所示)寄存,进行分支滤波,得到第i路补相结果。

d) 按照c)所述重复进行所需的各路补相,将各路补相结果并行输出。

2 基于广义多相滤波的L波段数字接收机

2.1 数字接收机架构

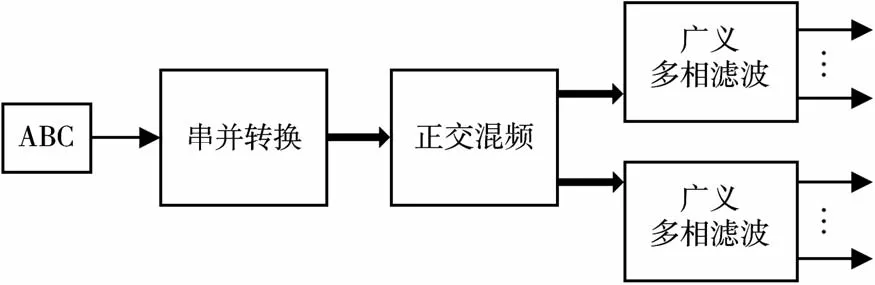

以上文所述L波段数字接收机为例,该数字接收机对L波段的宽带信号进行直接采样,中心频率1.2 GHz,带宽300 MHz,采样时钟960 MHz,在FPGA中完成宽带数字接收处理后使用光纤送出基带信号,基于广义多相滤波构建数字接收机,如图7所示。

图7 基于广义多相滤波的数字接收机架构

ADC采用某公司XXX190芯片,该芯片模拟带宽达3 GHz,可以对四路信号同时进行1.25 GHz采样。该芯片输出为串行高速lvds信号,以DDR模式传输。为了满足高速源同步系统的应用需求,所用FPGA中集成了具有专用时钟和逻辑性能的串并转换器,当输入数据采用DDR模式时,该串并转换器的转换比可以为4,6,8。考虑到后续处理资源的使用,选用的转换比为6,此时串并转换器的输出为6路160 MHz并行数字信号。

由于采样频率和信号中心频率之间正好满足最佳采样率的要求,在进行数字混频时可以避免乘法器的使用,直接与“1,0,-1,0”和“0,-1,0,1”相乘即完成数字混频和正交变换。这里不难根据前述的串并转换比推导出每一路160 MHz信号的转换规律,比如第一路应依次乘以“1,-1,1,-1…”第二路为全0,以此类推。

在该数字接收机中,信号带宽达300 MHz,这就决定了该数字接收机的抽取比不能大于3。但是,由于硬件的限制,无法直接进行转换比为3的串并转换。解决该问题有两个途径,一是将转换后的数据提速,由此带来的问题是处理速度的提高,这将是数字信号处理器件面临的严重挑战。本文使用的是另一个办法,即基于广义多相滤波进行系统架构,多相分解因子D=6,抽取因子K=3,需进行P=2倍补相。广义多相滤波共输出2路信号,整个数字接收机输出4路i/q信号,每路信号速率为160 M Hz,这里数字滤波的速率仍然为160 M Hz,可以有效缓解对数字信号处理器件的速度要求。同时,广义多相滤波还为实际应用提供了更多的选择。比如,当带宽更宽时,可以令K=1,P=6,即不对数据进行抽取,但是同样可以通过多相分解降低处理速率,而当带宽更窄时,可以令K=6,P=1,此时成了传统的多相滤波,它是广义多相滤波的一个特例。由此可见,设计者可以在广义多相滤波概念的框架内灵活进行速度与面积的互换。

2.2 仿真验证

为了对所述广义多相滤波及数字接收机进行验证,使用Matlab软件产生测试数据,使用Verilog语言实现上述功能模块,在目标芯片中进行布局布线,将产生的网表文件和测试数据一起导入Modelsim软件进行仿真,并使用Matlab读出仿真结果。

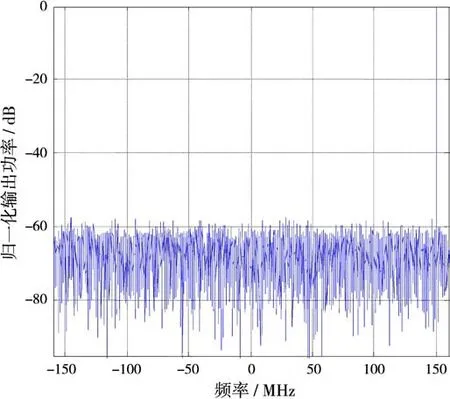

假定输入信号频率为1350 MHz,载频为1200 MHz,按上述架构实现数字接收机,其中广义多相滤波的阶数为96阶,输出时域信号如图8所示,上图为广义多相滤波输出的第1路同相/正交分量,下图为广义多相滤波输出的第2路同相/正交分量。图9为广义多相滤波输出的信号频谱。

图8 广义多相滤波输出信号时域波形

图9 广义多相滤波输出信号频谱

2.3 广义多相滤波所需的硬件资源

上述广义多相滤波(96阶FIR滤波)的综合结果在某FPGA芯片上进行布局布线,所需的资源如下:

Combinational ALUTa:2127

Dedicated logic registers:5135

Total registers:5135

DSP block 18-bit elements:384(即192个18×18乘法器)

这里我们重点关注的是乘法器资源的使用,96阶FIR滤波器在进行P=2广义多相滤波时,所需的乘法器资源为384个DSP block 18-bit elements,即192个18×18乘法器。在进行P=1广义多相滤波,即传统多相滤波时,所需的乘法器资源为192个DSP block 18-bit elements,即96个18×18乘法器。这说明广义多相滤波对乘法器资源的需求是数据提速的方式的P倍(P=D/K,为多相分解阶数和抽取比之间的比例)。设计者可以灵活调节P的值,从而按实际需求在速度与面积之间进行权衡。

3 结束语

本文所述广义多相滤波解决了工程中常见的多相分解的阶数与所需抽取比不一致的问题。传统多相滤波器可以看作广义多相滤波在P=1时的一个特例。本文在广义多相滤波的基础上构建了一个宽带数字接收机,仿真验证表明,该算法能够满足宽带数字接收机的使用要求,为工程实践中的速度与面积互换原则提供了一种新的理解方式,可操作性强,对于宽带数字接收机的研制有一定的实际意义。

[1]James Tsui.宽带数字接收机[M].杨小牛,陆安南,金飚,译.北京:电子工业出版社,2002:7-13.

[2]朱拥建,王宏.宽带数字接收机的设计与实现[J].中国电子科学研究院学报,2010,5(1):86-89.ZHU Yong-jian,WANG Hong.The Design and Implementation of the Wide-band Digital Receiver[J].Journal of CAEIT,2010,5(1):86-89.(in Chinese)

[3]杨小牛,楼才义,徐建良.软件无线电原理与应用[M].北京:电子工业出版社,2005:28-31.

[4]刘宁,何子述.空间谱估计系统中信道化接收机的实现[J].雷达科学与技术,2010,8(5):469-473.LIU Ning,HE Zi-shu.Implementation of Digital Channelized Receiver for Spatial Spectrum Estimation System[J].Radar Science and Technology,2010,8(5):469-473.(in Chinese)

[5]邓岚,康怀祺,李宏波,等.基于FPGA的宽带信号数字下变频设计与实现[J].火控雷达技术,2011,40(4):52-55.