基于格雷码的深度可配置的异步FIFO设计实现

丛红艳,刘 瑛,万 清

(中国电子科技集团公司第58研究所,江苏 无锡 214035)

1 引言

异步FIFO存储器是一种先进先出的电路,使用在时钟频率不同的数据接口部分,用来存储、缓冲在两个异步时钟之间的数据传输。设计异步FIFO的关键是产生精确、可靠的“空”和“满”信号,空满标志主要用于在FIFO出口的入口向外部读写逻辑标志FIFO的数据存储情况,当空标志置位时,读时钟域的读写逻辑不能继续从FIFO读数据,否则会发生错误。当满标志置位时,写时钟域的读写逻辑也不能继续向FIFO写数据,否则会发生溢出。设计FIFO关键做到写满而不溢出,读空又不多读。

2 异步FIFO设计方法与实现

本设计采用SMIC 40 nm标准数字单元库。首先由memory compiler自动生成1024×18存储器,根据电路的各项指标要求,用Verilog硬件描述语言对其进行RTL仿真,来实现配置为18 kB或者36 kB存储器。对于18 kB,支持配置4k×4,2k×9,1k×18 FIFO,对于36 kB支持的配置是8k×4,4k×9,2k×18,1k×36 FIFO;Block RAM的端口A用作FIFO的读端口,端口B是FIFO的写端口[4]。NC、DC功能验证成功之后,综合得出门级的电路图,进行静态时序分析、版图的自动布局布线、反标延时、后仿真直到流片。

2.1 读写使能的产生

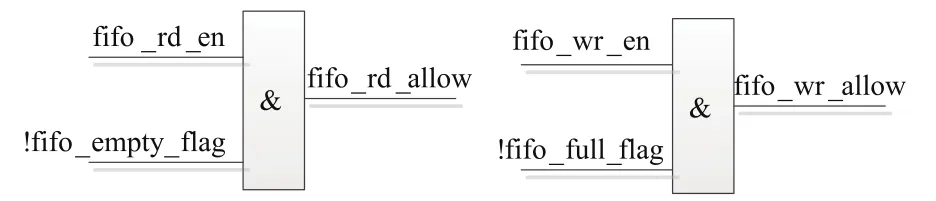

读写FIFO使能产生是为了确保FIFO即不多读又不多写,采用了自我保护方式,如图1所示。

图1 读写使能产生

真正的写FIFO使能为外部的写使能和非满的组合:Assign fi fo_write_allow = fi fo_wr_en&& ! fi fo_full_flag;真正的读FIFO使能为外部的读使能和非空的组合:Assign fifo_read_allow = fifo_read_en&& !fi fo_empty_ fl ag。

2.2 跨时钟域带来的亚稳态问题

亚稳态[1,3]是指触发器信号和时钟不满足建立时间/保持时间(setup/hold)的基本要求,触发器的输出端将会达到一个不确定的状态,当一个触发器进入亚稳态时,无法预测它的输出电平,也无法预测其输出何时才能稳定在某个正确的电平上。在这期间,触发器输出一些中间级电平,或者可能处于振荡状态。并且这种错误的输出电平可以沿信号通道上的各个触发器级联式传播下去,当一个信号跨越某个时钟时,需要对该信号进行同步,用以防止前级信号亚稳态对后级信号产生影响。亚稳态又是不可避免的,下面介绍的方法可以减少其发生的概率。

(1)对读写地址采用格雷码

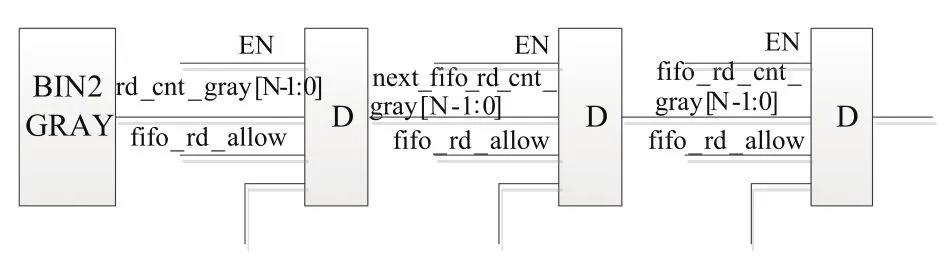

异步FIFO读、写指针如果采用二进制表示指针,地址增1需要多位进行翻转,在同一时钟延采集多位数码会造成逻辑误判。而格雷码编码的相邻两个码组之间只有一位不同,因而在计数时,格雷码只有一位发生改变,这样与其他码相比更为可靠,可以有效地减少亚稳态的产生,也允许电路能够以较少的稳定时间在较高的速度下工作。同时采用三级触发器来同步异步输入信号,信号同步的目的是为了防止上一级的亚稳态信号对下级逻辑造成影响。格雷码模块延时3拍的结构如图2。

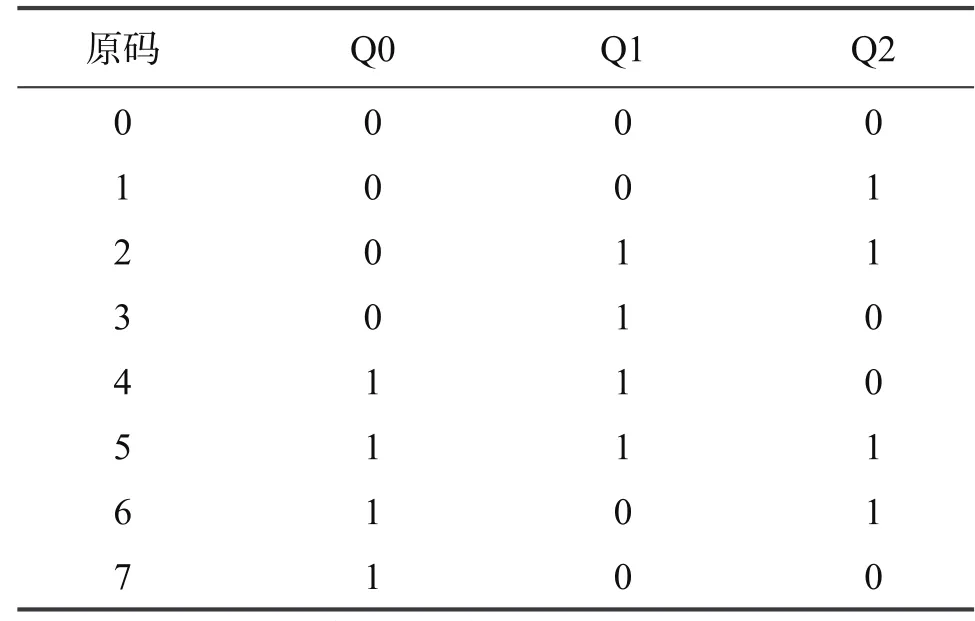

格雷码是一种做加一运算时只变化一位的编码,表1即为一个三位格雷码编码格式。

图2 采用格雷码模块设计延时3拍

表1 三位格雷码编码

可见格雷码每次只在相邻位发生变化,好处是它可避免因线延迟不一致而引起的毛刺现象。

(2)对读写地址采用单步循环码

采用Gray码的设计方式,由于其码长为2N,决定了这种存储器的深度一定要为2N-1,使得这种设计方式存在局限性。采用单步循环码可以设计任意深度的异步FIFO,深度不再限制在2N-1。

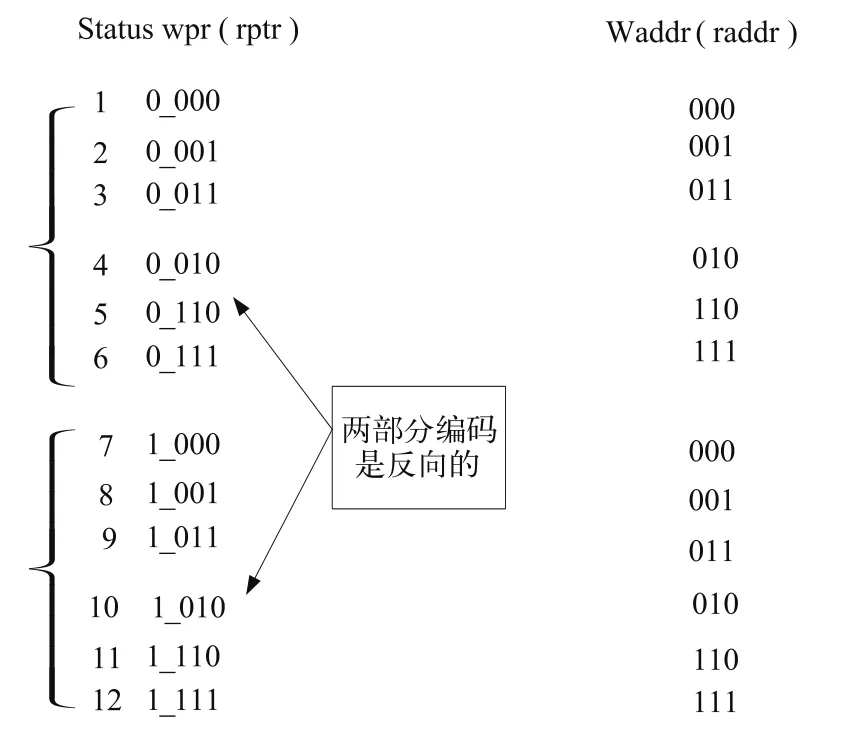

下面简单介绍单步循环码[2],当它采用4位编码时,码的总长度是12,分为上下两部分,编码的前半部分,MSB=0;编码的下半部分MSB=1,两部分编码是反向的,同时当MSB=0时,低N-1位直接作为FIFO地址,当MSB=1时,低N-1位的反码作为FIFO地址,如图3所示,指针每经过一次存储循环,FIFO地址完成两次循环,编码的相邻两个码组之间只有一位不同,即从一种状态到另一种状态的跳转只会有一位翻转,因此具有单步循环码的特性。

图3 单步循环码

但是单步循环码不足之处是所需要的硬件开销较大,时序较之Gray码存储器也要差一些。因此只有当所设计存储器深度需求与2N相差较大时,才会考虑采用这种设计,例如,假设需要存储深度为20,如果采用Gray码设计不得不设计成深度为32的存储器,而采用这种方式至少可以节省37%的面积。

最后对RTL代码进行了综合,读写地址采用单步循环码电路和格雷码电路,性能指标对照表如表2。

表2 不同编码方式比较

由表2可知,由于采用格雷码,提高了系统的稳定性。但是不可避免的较之单步循环码,需要更多的逻辑单元,需要更长的数据传输时间。

2.3 空、满、几乎空、几乎满的标志位的产生

空、满、几乎空、几乎满标志设计好坏直接影响到整个异步FIFO的性能。空、满标志产生的原则是:当整个异步FIFO被写满时而不会溢出,当整个异步FIFO被读空时而不会多读。而要产生精确的几乎空、几乎满标志,可以多做几个格雷码的延时地址,利用这些延时地址距离远近关系灵活产生特定读写间距的几乎空、几乎满标志。

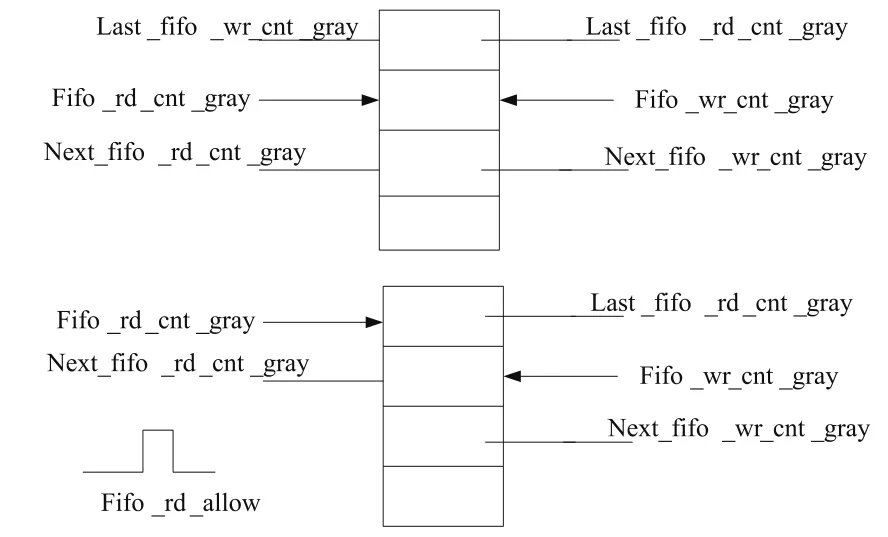

(1)空标志 fi fo_empty_ fl ag

当读F I F O的格雷码地址等于写的格雷码地址时,fifo_rd_cnt_gray= =fifo_wr_cnt_gray或者下次要读的格雷码地址等于格雷码写地址next_fifo_rd_cnt_gray= =fifo_wr_cnt_gray;并且正在执行读操作,此时需要置fifo_empty_flag标志有效,其指针如图4所示。

图4 读空时指针位置

(2)满标志 fi fo_full_ fl ag

当写FIFO的格雷码地址等于上次读的格雷码地址时fifo_Wt_cnt_gray= =Last_fifo_rd_cnt_gray或者下次要写的格雷码地址等于上次读的格雷码地址next_fifo_wr_cnt_gray= =Last_fifo_rd_cnt_gray;并且正在执行写操作时需要置Full标志有效,为了避免复杂的逻辑提高FIFO的整体速度可使用FIFO实际深度-1,写满指针如图5所示。

图5 写满时指针位置

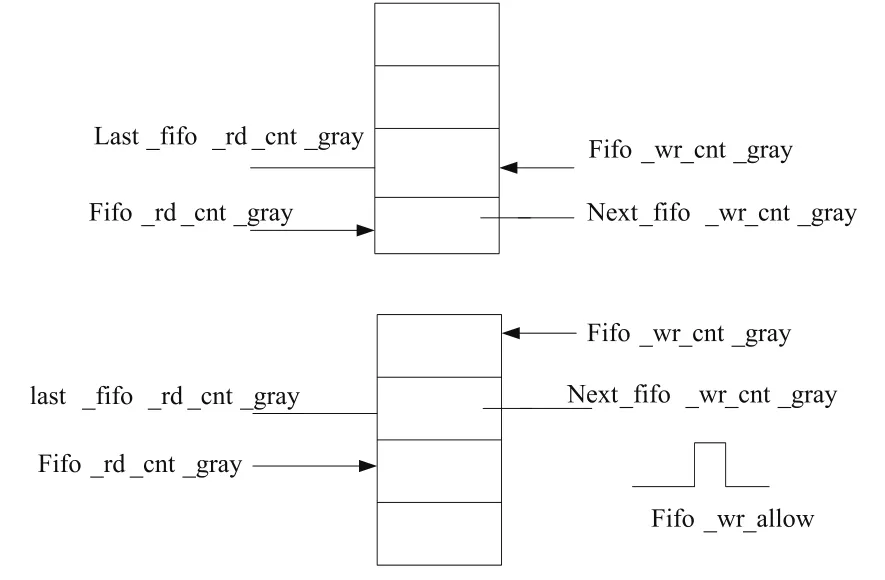

(3)几乎满 fi fo_alfull_ fl ag

几乎满标志,通过格雷码的延时3拍的地址,然后利用读写格雷码地址距离远近来产生特定读写地址间距,电路图如图6所示。

图6 几乎满逻辑电路图

(4)几乎空与几乎满程序类似,由读时钟产生。几乎满和几乎空如用同一个时钟,那么误差与两个时钟的具体大小相关。例如几乎满和几乎空都是用写时钟得到的,那么几乎满比较精确。如果写时钟比读时钟慢,则几乎空误差较大,如果写时钟比读时钟快,那么几乎空的误差会比较精确。

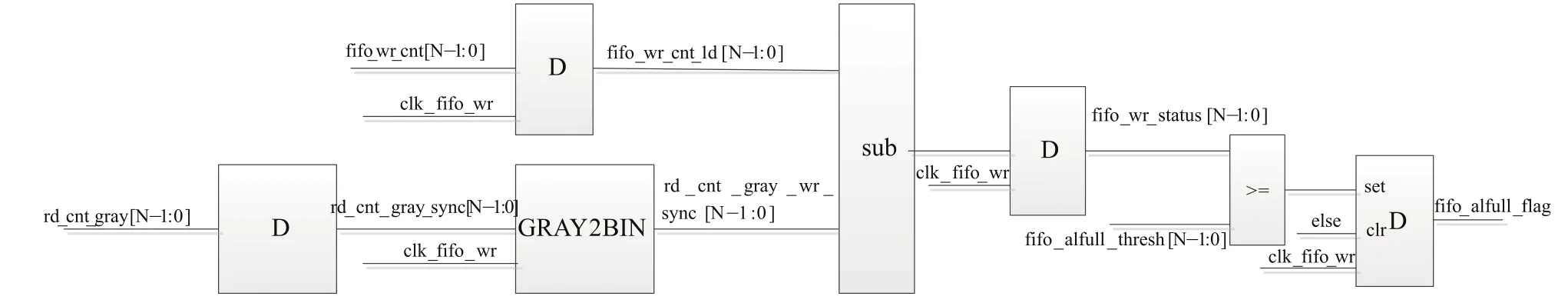

3 Verilog实现与仿真

本设计实现了一个规格可配置的双时钟异步FIFO,随机选择规格为1k×36的双时钟异步FIFO的verilog前仿,仿真工具采用ncverilog编译RTL,进行数字前仿真,并进行了DC综合。从仿真波形可以看到,FIFO控制信号能够准确地产生,并且整个FIFO的工作波形也符合设计要求。

仿真1(图7):写入空FIFO,写满后读空,然后再写。整个FIFO的空、满、几乎空、几乎满的标志位变化。

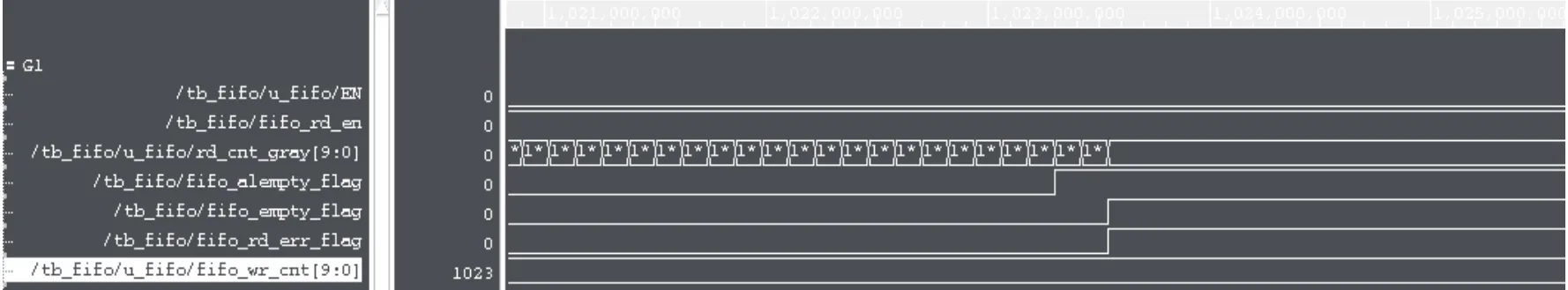

仿真2(图8):从满FIFO中读空数据,当读空且在读使能有效的情况下, fi fo_rd_err_ fl ag有效。

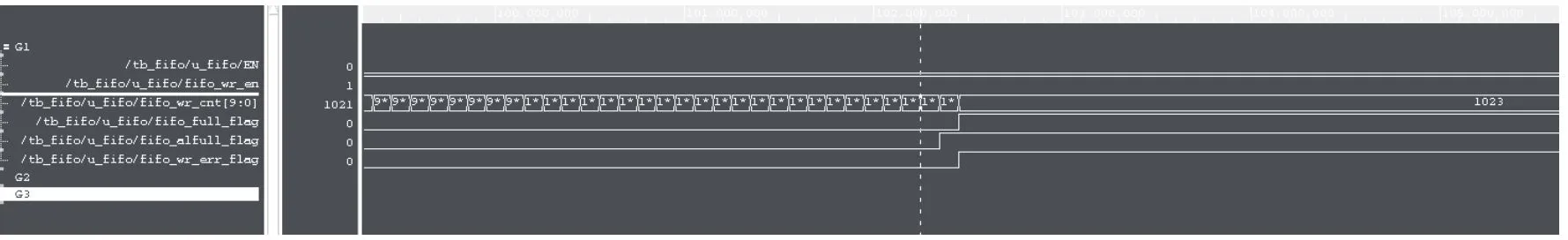

仿真3(图9):写入空FIFO,直到写满时标志位的变化;当写满且在写使能有效的情况下,f fo_wr_err_flag有效。

仿真4(图10):验证二进制读写指针转格雷码读写指针正确性。

图7 仿真1

图8 仿真2

图9 仿真3

图10 仿真4

[1] 汪东,马剑武,陈书明. 基于Gray码的异步FIFO接口技术以及应用[J]. 计算机工程与科学,2005,27(11):58-60.

[2] Clifford E Cumming, PeterAlfke. Simulation and synthesis Technique for Asynchronous FIFO Design with Asynchronous Pointer Comparisons [Z]. SNUG,2012.1218.

[3] 夏宇闻. Verilog数字系统设计教程[M]. 北京:北京航天航空大学出版社,2008.

[4] 周敏. 高速异步FIFO的设计和实现[J]. 计算机工程与科学,2009(2).