一种FPGA中BRAM36k的设计方法

刘 瑛,胡 凯,丛红艳,万 清

(中国电子科技集团公司第58研究所,江苏 无锡 214035)

1 引言

本文采用基于SMIC 40 nm工艺的Artisan Memory Compiler[1]软件编译产生BRAM 18 kB真正双端口RAM来实现最高680 MHz的读写操作速度。根据电路的各项指标要求,用Verilog硬件描述语言对其进行RTL设计和仿真,来实现配置为18 k或者36 k的存储器。

BRAM36k最多可以存储36 kB数据,并且可以配置成两个独立的18 kB RAM或者一个36 kB RAM[2]。每个SRAM36k,作为RAM使用时,可以配置成一个32k×1、16k×2、8k×4、4k×8(9)、2k×16(18)、1k×32(36);作为FIFO使用时,可以配置成8k×4、4k×9(8)、2k×18(16)、1k×36(32)的FIFO。每个SRAM18k作为RAM使用时,可以配置成一个16k×1、8k×2、4k×4、2k×8(9)、1k×16(18)存储器。作为FIFO使用时,可以配置成一个4k×4、2k×9(8)、1k×18(16)的FIFO。同时该模块作为RAM使用时,也支持同一个端口,但是读写位宽不一样的模式。

2 BRAM36k 内部结构与实现

真双口36 kB BRAM 双端口存储器由两个独立的18 kB RAM组成,其具体结构内部图如图1所示。

其中FIFO_U0完成FIFO读写访问控制功能,支持以两块SRAM18k作为一个RAM构成的FIFO读写访问,也支持以SRAM18k_U0作为RAM构成的FIFO读写访问。FIFO_U1只支持以SRAM18k_U1作为RAM构成的FIFO读写访问。SRAM18k_U0完成对SRAM18k_U0以及SRAM18k_U1读写访问控制功能,SRAM18k_U1完成对SRAM18k_U1读写访问控制功能。

由于Memory Compiler编译产生的SRAM18k存储容量为18 kB,定义为SRAM_DP。利用其支持bit MASK写操作,可以根据当前的地址信息产生写使能MASK信号,这样就可以只改变一个地址中某个或者某些bit内容,对外体现为不同的地址深度和位宽组合模式。其具体的组合模式如表1所示。

同时,在读操作时,通过地址信号寄存一拍的信号来选择SRAM_DP的读数据中比特位置(表2)。

另外当两块SRAM18k级联作为BRAM36k使用时,由于支持同一个端口读写位宽不同,在合理的读写位宽组合下,当读位宽或者写位宽为32 bit或36 bit时,需要特别处理。

例子1是以1k×32模式写,以4k×8模式读,此时两块SRAM18k写模式为1k×16,读模式为2k×8,此时用户逻辑发出的写地址和读地址映射关系为:

写地址是X,则读地址X<<2+[0,1,2,3]。

当写入操作时,32 bit数据需要同时写入SRAM18k_U1和SRAM18k_U0,此时SRAM18k_U1和SRAM18k_U0的写地址信号相同,如地址为X。当进行读操作时,需要以2k×8模式先读SRAM18k_U0,要读两次,然后再以2k×8模式读SRAM18k_U1,要读两次;这样交替进行完成32 bit全部读出,此时读出的数据按位拼接后是与写数据相同的。其地址关系如图2所示。

例子2是以4k×8模式写,以1k×32模式读,此时两块SRAM18k写模式为2k×8,读模式为1k×16。此时用户逻辑发出的读地址和写地址映射关系为:

写地址是X、X+1、X+2、X+3,则读地址X>>2。X需要与32 bit地址对齐。

当写入操作时,8 bit数据需要根据写地址关系,如果地址是X、X+1则写入SRAM18k_U0,如果地址是X+2、X+3则写入SRAM18k_U1。当进行读操作时,需要以1k×16模式同时读SRAM18k_U0和SRAM18k_U1;此时读出的数据按位拼接后是与写数据相同的。

进行写操作时,需要以2 k×8模式先写SRAM18k_U0,要写两次,然后再以2k×8模式写SRAM18k_U1,要写两次;这样交替进行完成32 bit全部写入,进行读操作,则以1k×16模式同时读取SRAM18k_U1和SRAM18k_U0,读地址信号相同,将两段16 bit读数据拼接起来,SRAM18k_U1读数据放在高位,这样就读出了之前以4k×8模式写入的数据。其地址关系如图3所示。

表2 读访问操作关系

图2 SRAM18k_U0/U1 地址对应关系

3 BRAM36k整体仿真与实现

仿真1:BRAM36k A口作为1k×32模式写入时,验证功能正确。

仿真条件:实现一个A口按1k×32模式,从初始地址0,以初始写数据32’h9ECAB63D,写数据递增,批量写入BRAM中。其中0地址写入数据为32’h9ECAB63D,1地址写入数据为32’h9ECAB63E,2地址写入数据为32’h9ECAB63F,3地址写入数据为32’h9ECAB640,…。

图4中GROUP14为Testbench中构造的用户逻辑驱动输入激励以及用户的读数据输出。{di_a_u1[15:0],di_a_u0[15:0]}构成32 bit写数据,初始写数据为32’h9ECAB63D,每次写操作依次递增,{do_a_u1[15:0],do_a_u0[15:0]}构成32 bit读数据,en_a_u0信号为BRAM36k访问的片选信号,高有效;{we_a_u1[1:0],we_a_u0[1:0]}构成32 bit写数据的byte写使能,高有效,全零则表示此次访问为读操作;addr_a_u0[13:0]在写操作时为写地址,在读操作时为读地址,初始值为0,每次写操作或者读操作后依次递增。

图3 SRAM18k_U0/U1 地址对应关系

GROUP16为内部SRAM18k_U1 A端口访问的接口信号,ENA表示RAM A端口片选使能,高有效;ADDRA表示A端口访问地址,WENA为18 bit写数据的MASK信息,当某一位置bit为0,表示写数据中对应bit位置的数据需要写入RAM中;DIA和DOA分别为写数据和读数据,实际还有DIPA、DOPA图中未画出,用于承载18 bit高2 bit,用于用户的奇偶校验bit输入和输出;GROUP15为内部SRAM18k_U0 A端口访问的接口信号,信号含义同SRAM18k_U1。

由仿真波形可见,当BRAM36k作为1k×32模式写入时,此时32 bit的写数据需要同时写入SRAM18k_U1、SRAM18k_U0,两块RAM的访问地址是相同的,但数据不同,两块RAM的WENA[15:0]为0,表示要将各自输入的DIA[15:0]写入RAM中。

仿真2:当BRAM作为4k×8模式读出时,验证功能正确性。

仿真条件:A口按4k×8模式,从初始地址0,批量读出BRAM36K中的数据。期望从0地址读出数据为8’h3D,1地址读出数据为8’hB6,2地址读出数据为8’hCA,3地址读出数据为8’h9E;从4地址读出数据为8’h3E,5地址读出数据为8’hB6,6地址读出数据为8’hCA,7地址读出数据为8’h9E;从8地址读出数据为8’h3F,9地址读出数据为8’hB6,10地址读出数据为8’hCA,11地址读出数据为8’h9E…。

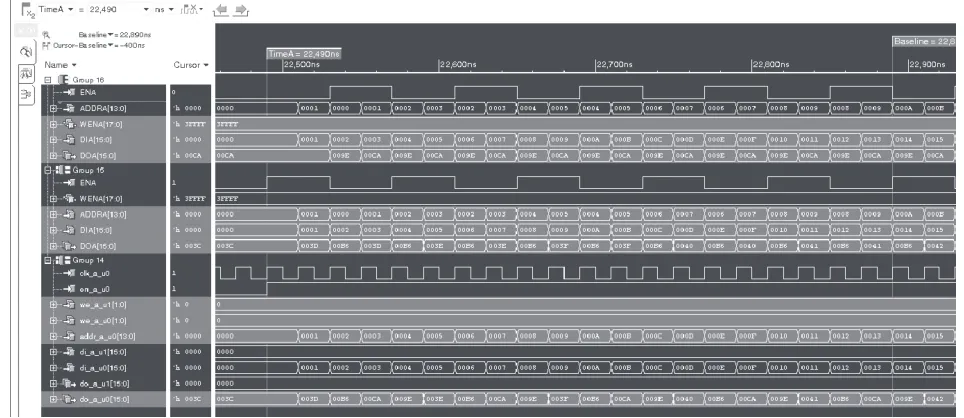

图5中GROUP14为TESTBENCH中构造的用户逻辑驱动输入激励以及用户的读数据输出。{do_a_u1[15:0],do_a_u0[15:0]}构成32 bit读数据,en_a_u0信号为BRAM36K访问的片选信号,高有效;{we_a_u1[1:0],we_a_u0[1:0]}构成32 bit写数据的byte写使能,高有效,全零则表示此次访问为读操作;addr_a_u0[13:0]在写操作时为写地址,在读操作时为读地址,初始值为0,每次写操作或者读操作后依次递增。

GROUP16为内部SRAM18k_U1 A端口访问的接口信号,ENA表示RAM A端口片选使能,高有效;ADDRA表示A端口访问地址,WENA为18 bit写数据的MASK信息,当某一位置bit为0,表示写数据中对应bit位置的数据需要写入RAM中,在读操作时,必须全部为1;读数据在ENA有效后的后一拍输出。DIA和DOA分别为写数据和读数据,实际还有DIPA、DOPA图中未画出,用于承载18 bit高2 bit,用于用户的奇偶校验bit输入和输出;GROUP15为内部SRAM18k_U0 A端口访问的接口信号,信号含义同SRAM18k_U1。

图4 BRAM36k A口作为1k×32模式写入仿真结果

图5 BRAM作为4k×8模式读出时仿真结果

由仿真波形可见,当BRAM36k作为4k×8模式读出时,此时原来按32 bit的写入0地址(1k×32模式的地址0)的数据需要通过四次读0、1、2、3(4k×8模式的地址0、1、2、3)才能全部回读回来。两块RAM的访问是交替进行,先读SRAM18k U0的0、1地址,再读SRAM18k U1的0、1地址。两块RAM的WENA为全1,表示此时进行的是读操作。

仿真3:当B口按4k×8模式写入时,验证功能正确性。

仿真条件:B口按4k×8模式,从初始地址0,批量写入数据。

图6中GROUP11为TESTBENCH中构造的用户逻辑驱动输入激励以及用户的读数据输出。di_b_u0[7:0]}构成8 bit写数据,每次写操作依次递增,以初始写数据8’hDF,实际有效的写数据承载在di_b_u0[7:0]上,批量写入BRAM中。0地址写入数据为8’hDF,1地址写入数据为8’hE0,2地址写入数据为8’hE1,3地址写入数据为8’hE2,…。{do_b_u1[15:0],do_b_u0[15:0]}构成32 bit读数据,en_b_u0信号为BRAM36k B端口访问的片选信号,高有效;we_b_u0[0]构成8 bit写数据的byte写使能,高有效,we_b_u0[0]为零则表示此次访问为读操作;addr_b_u0[13:0]在写操作时为写地址,在读操作时为读地址,初始值为0,每次写操作或者读操作后依次递增。

GROUP13为内部SRAM18k_U1 B端口访问的接口信号,ENB表示RAM B端口片选使能,高有效;ADDRB表示B端口访问地址,WENB为18 bit写数据的MASK信息,当某一位置bit为0,表示写数据中对应bit位置的数据需要写入RAM中;DIB和DOB分别为写数据和读数据,实际还有DIPB、DOPB图中未画出,用于承载18 bit高2 bit,用于用户的奇偶校验bit输入和输出;GROUP12为内部SRAM18k_U0 B端口访问的接口信号,信号含义同SRAM18k_U1。

图6 B口按4k×8模式写入仿真结果

由仿真波形可见,当BRAM作为4k×8模式写入时,此时8 bit的写数据需要根据写地址是属于X、X+1还是X+2、X+3,选择写入SRAM18k_U0还是SRAM18k_U1,其中X为32 bit地址对齐。WENB[17:0]为18’h3FF00表示写入低8 bit,即是18 bit的[7:0],WENB[17:0]为18’h300FF表示写入高8 bit,即是18 bit的[15:8]。

仿真4:当B口按1k×32模式读出数据时,验证功能正确性。

仿真条件: B口按1k×32模式,从初始地址0,批量读出BRAM中的数据。期望从0地址读出数据为32’hE2E1E0DF,1地址读出数据为32’hE6E5E4E3。

图7中GROUP11为testbench中构造的用户逻辑驱动输入激励以及用户的读数据输出。{do_b_u1[15:0],do_b_u0[15:0]}构成32 bit读数据,en_b_u0信号为BRAM36K访问的片选信号,高有效;{we_b_u1[1:0],we_b_u0[1:0]}构成32 bit写数据的byte写使能,高有效,全零则表示此次访问为读操作;addr_b_u0[13:0]在写操作时为写地址,在读操作时为读地址,初始值为0,每次写操作或者读操作后依次递增。GROUP13为内部SRAM18k_U1 B端口访问的接口信号,ENB表示RAM片选使能,高有效;ADDRB表示B端口访问地址,WENB为18 bit写数据的MASK信息,当某一位置bit为0,表示写数据中对应bit位置的数据需要写入RAM中,在读操作时,必须全部为1;读数据在ENB有效后的后一拍输出。DIB和DOB分别为写数据和读数据,实际还有DIPB、DOPB图中未画出,用于承载18 bit高2 bit,用于用户的奇偶校验bit输入和输出;GROUP12为内部SRAM18k_U0 B端口访问的接口信号,信号含义同SRAM18k_U1。

由仿真波形可见,当BRAM作为1k×32模式读出时,此时原来按8 bit写入0、1、2、3地址(4k×32模式的地址0、1、2、3)的数据只需要通过一次读0地址(1k×32模式的地址0)就能全部回读回来。两块RAM的访问同时进行,地址变化相同,两块RAM的WENB为全1,表示此时进行的是读操作。

图7 B口按1k×32模式读出数据仿真结果

[1] Xilinx Inc. Xapp(130). Virtex中块状SelectRAM+特性的使用[Z]. 2000-12-18.

[2] 王睿,刘布民. FPGA中BRAM设计研究[D]. 2009.