一种数据Cache的设计和验证

屈凌翔,袁 潇,王 澧

(中国电子科技集团公司第58研究所,江苏 无锡 214035)

1 前言

近年来,DSP处理器发展速度极快,存储器系统的发展也不慢,但存储器主要在存储空间上提升,其存取速度的提高有限。例如主存储器,其存储空间从最早的KB数量级提高到现在的GB数量级,基本三年就会更新一代,但是主存的访问速度这方面的性能每年只有7%的提升[1]。这就导致中央处理器处理能力的提升速度远远高于存储器存取性能的提升速度,两者之间的差距越来越大。如今存储器已成为制约系统性能的主要瓶颈,必须提高存储器的效率才能更有效地提高系统的整体性能。

因此,Cache应运而生。Cache介于中央处理器和主存之间,其存取所需时间极少,只有0.25 ns到0.5 ns,大概是主存存取时间的1%[2]。Cache的出现有效地解决了主存和处理器速度不匹配的难题。

2 Cache基本原理和组成

在较短时间间隔内,由于程序而产生的地址通常集中在存储地址空间很小的范围内。这种对局部范围的地址频繁访问而对该范围以外的地址访问极少的现象,称之为程序访问的局部性。

由于这种时间和空间的局部性[3],可以在主存和处理器寄存器之间放置一个小容量的高速存储器,将最近一段时间需要的指令或数据放入其中,供处理器快速调用。这个介于主存和处理器之间的小容量高速存储空间我们称为Cache(高速缓冲处理器)。

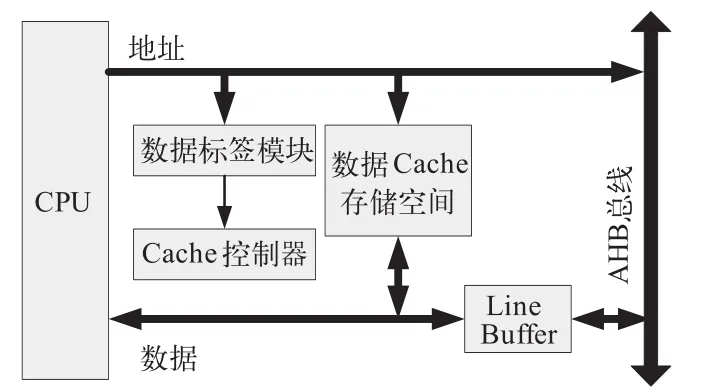

Cache主要由Cache Tag、Cache存储体、Cache控制模块组成。Cache Tag主要用来记录Cache存储体中数据的位置和判断Cache内数据是否命中;Cache存储体主要用来存储片外数据,方便处理器直接调用;而Cache控制模块则控制整个Cache的具体工作,它决定了Cache的工作效率。

3 Cache架构设计

本文设计的数据Cache根据具体功能实现分为了四个模块:Cache控制模块、Cache数据通路模块、Cache Tag模块、Line Buffer模块。

图1 Cache架构框图

Cache控制器是数据Cache的主控制模块,主要用来产生访存控制信号来控制对DMEM的访问,生成并发送给处理器异常、陷阱、访存完成等应答信号,以及数据Cache和总线之间交互的信号,控制整个Cache的工作流程,确保各个情况下Cache都能工作或进入陷阱调试。Cache数据通路模块是传输数据Cache的数据信息的路径,表明处理器、DMEM、总线之间的数据流方向,以及不同类型数据间的转换等。Cache标签为Dcache的标签存储体,与Cache存储体的每个Cache Line一一对应,对Cache是否命中进行判断,并对Dcache的特殊有效位进行维护等。Line Buffer为数据Cache中处理器和总线直接的缓存体,它的作用是作为重装的流Buffer,进行数据重装的工作,用以提高Cache工作效率,减少处理器等待时间,降低功耗。

3.1 数据通路

数据Cache主要完成处理器对内部DMEM的读写访存操作,具体的操作包含处理器对Dcache的读写、Dcache缺失时进行的重装和写回、以及总线对DMEM的读和写。主要有处理器的读数据通路、处理器的写数据通路、Dcache的写回数据通路、Dcache的重装数据通路,通路之间相互连通。

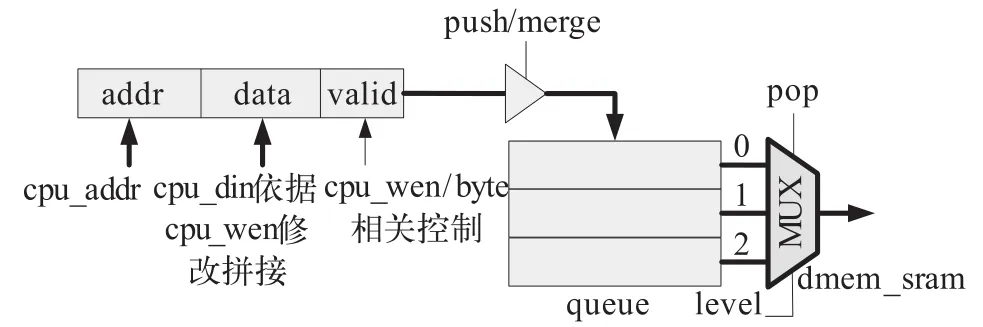

而数据Cache根据数据通路的状态选择数据:选择RAM和AHB送往处理器的数据,或把组合起来的数据送往内部其他模块进行转换对齐等操作。数据Cache与外部主存之间,有存储缓存队列信号,其作用是通过字节操作拼接成半字,进行数据的移位对齐调整,产生RAM0到RAM3相关的存储信号。

写入RAM的数据首先会被放入队列queue中,若队列中已有数据,则替换已有数据。当前实际写入队列的数据实际上是其最顶层的那个数据。

图2 queue模块框图

3.2 Cache Tag

本数据Cache配置大小最大为4 kB,一共有128个Cache Line,每个Line有256位,因此,每个Tag中的Index需要7位,对应每个Cache Line中的128个Line。Tag与数据Cache的Cache Line相对应,也是128行,每行一共46位,其中低44位是由两路每路22位的Tag组成的,而高两位分别是两路Tag的有效位,用来判断哪路Cache Line有效。

数据Cache Tag主要进行判定Cache是否命中,从而产生命中信号。为了加快Tag的比较速度,Cache Tag采用的是并行组织结构。其具体工作流程详见数据Cache命中逻辑流程设计部分。

3.3 Line Buffer

Line Buffer是数据Cache中一块极其重要的组成部分,它是数据通路的一部分,在系统Dcache配置有效时,Line Buffer起到数据暂存等辅助作用,相当于一个流Buffer,当Dcache未进行配置时,Line Buffer则就默认成为一级Nano Cache。当Line Buffer作为Streaming Buffer使用时,主要作用是加快数据Cache向处理器输送数据的速度。若出现重装操作,处理器会把总线上的数据分别送至Dcache和Line Buffer,在Line Buffer中的数据会进行数据对齐操作并被送至处理器,而不需要等到数据进入Dcache后再送入处理器,减少了处理器等待时间,提高了整个系统的运行效率。当Dcache未配置时,Line Buffer就作为最基础的一级Cache使用。

Line Buffer存储的数据有两种,一种是重装操作时总线送来的AHB数据,Line Buffer作为Buffer和Nano Cache时都有;另一种是Line Buffer作为Nano Cache时,CPU送来的存储数据。读出Line Buffer的数据也有两种,一种是作为Buffer或Nano Cache时送往处理器的读出数据;另一种是作为Nano Cache时写回的数据。

图3 数据Cache Tag组织结构图

图4 取址信号、数据Cache Tag和Cache RAM的组织形式

Line Buffer送往处理器的数据需要进行对齐操作,将128位的输出结果拆分组合为256位数据,最终选取出64位送往中央处理器。

3.4 Cache控制模块

数据Cache主要实现处理器对外部数据主存的读写操作,而Cache控制模块掌控着处理器读写操作的具体执行。通过其中的Cache控制模块进行读写操作的具体控制,其主要的控制方面有Cache命中的控制、Cache重装和写回的控制以及总线访问的控制。并且根据读写操作的完成情况生成数据Cache对处理器的反馈信号。

数据Cache命中的控制通过生成Cache命中信号的方式来实现,其中Dcache的命中信号在Cache Tag模块中产生,Line Buffer的命中信号在数据Cache控制模块中产生。当系统获得Cache命中信号后,若Cache命中,则依照命中信息产生访问Cache或Line Buffer的控制信息,选择正确的数据通路;若出现Cache缺失,则会访问总线,进行重装的操作。Cache的重装和写回操作分别由两个不同的状态机实现,而对于总线访问的控制,则是依据总线协议生成的相关信号,由总线相关的状态机控制实现。在Cache控制模块中,系统根据各个状态机的当前状态,生成模块相应的控制信号。

4 仿真验证

4.1 Cache命中仿真

在数据Cache产生命中的情况中,数据Cache首先会在控制模块中确认Cache Line中的数据是否有效,如果有效,那么则将Cache Tag与处理器发出的取址信号中的Tag段进行对比。在这过程中,Cache控制模块会做以下几件事情,检查Cache是否处于有效状态,另外Cache Line中数据是否有效。

如图5所示,处理器正在进行对外部存储器的访问操作。该情况下Cache产生了命中。仿真得出,从Cache命中到将数据发送给处理器,中间只需要一个周期,极大提高了系统效率。

4.2 Cache缺失仿真

Cache缺失一般会在两种情况下产生,一种是当前的Cache Line中数据无效;另一种是取址信号中的Tag值和两路Cache Tag都不匹配,这两种情况下系统会认为Cache产生缺失。图6所示为仿真过程中处理器第一次对外部主存进行读取数据时一定会产生的强制缺失。

图5 Cache命中仿真图

图6 Cache强制缺失仿真图

还有一种缺失是Cache Line数据无效的情况,如图7。同时,仿真测试发现,从Cache发生缺失到重装完成,将数据发送到处理器一共花了19个周期,满足不超过20个周期的设计要求。

4.3 Line Buffer重装操作仿真

在Cache发生缺失的时候,会同时启动重装操作。如图8所示,此时处理器在向数据Cache读取数据的时候,Cache发生了缺失。此时Line Buffer中请求信号收到请求,开始工作。在重装过程中,Line Buffer的工作状态为:首先判定Line Buffer数据是否有效,然后判定两路Line Buffer输入数据哪路有效,需要被发送给处理器,最后将需要的数据输入CPU。

4.4 Cache的逻辑综合以及功耗分析

本设计中,综合时使用的E D A工具是SYNOPSYS公司的Design Compiler。本综合所使用的工艺库是TSMC的65 nm低功耗工艺库。本设计中Cache的工作频率设定为500 MHz。综合后最常路径延时为1.49 ns,满足了约束条件。

图7 数据无效缺失仿真图

图8 重装操作仿真图

表1 综合结果

表2 功耗分析表

表2所示为125 ℃下、电压为0.9 V时的环境下,DSP芯片运行几种常用程序时的功耗分析。从表中看出,本设计中DSP处理器运行这些程序,功耗都在250 mW以内,远低于峰值功耗750 mW。DSP整体功耗保持在0.5 mW/MIPS以内。

5 结论

利用VCS软件对数据Cache完成功能仿真,并通过Design Complier软件进行逻辑综合,使得最长路径延时降低到1.49 ns;并通过基准程序测试,通过功耗分析得出,本设计数据Cache满足项目低功耗需要。

[1] Petrov P, Orailoglu A. Low-power Branch Target Buffer for Application-Speci fi c Embedded Processors [J]. IEEE Proceedings-Computers and Digital Techniques, 2005,152(4):482-488.

[2] Patterson D A, Hennessy J L. 计算机组成与设计-硬件与软件接口[M]. 北京:机械工业出版社,2008.

[3] Hennessy J L, Patterson D A. 计算机系统结构-量化研究方法[M]. 北京:电子工业出版社,2004.