用于锁相环快速锁定的鉴频鉴相器设计

寇先果,高 博,龚 敏

(四川大学物理科学与技术学院微电子学系,成都 610064)

1 引言

锁相环(PLL)在通信系统、微处理机、自动控制的时钟数据恢复、频率合成、时钟同步、调制与解调等领域有着广泛的应用,已经成为电子系统中不可或缺的基本模块。随着现代电子技术的快速发展,对锁相环在高速、快速锁定、低抖动等性能指标方面提出了更高的要求[1]。鉴频鉴相器(PFD)作为锁相环的重要模块,它的好坏直接影响到整个锁相环的性能。传统的PFD通过增加复位延迟可以消除死区,但是较长的复位恢复时间限制了PFD的最高工作频率,另外盲区会造成输入时钟边沿丢失和输出极性错误,严重减缓了锁相环的锁定速度[2]。因此需要设计适当的PFD来提高工作频率并且有效地消除盲区,从而加速锁定。

国内外学者已对此进行了大量的研究,文献[3]中采用了动态PFD,极大提高了工作频率,但是存在盲区现象,严重影响PLL的锁定速度;文献[4]、[5]提出了基于延时单元的两种PFD结构,避免了盲区造成的边沿丢失,然而较长的延时限制了工作频率,同时输入参考频率的变化很难适应延时单元。文献[6]提出了一种基于TSPC D触发器的非线性PFD,实现了无盲区,但是当输入相位差小于某一值时,电路输出UPE/DNE未能激活;文献[7]提出的非线性PFD电路中额外增加了电荷泵模块,极大加速了PLL的锁定速度,然而电路结构复杂,同时两电荷泵的充放电电流需要优化设计,增大了设计难度。

本文设计了一种用于PLL快速锁定的非线性PFD电路,在兼顾了死区和工作频率的前提下,基于传统PFD结构,设计了逻辑控制电路,在相位差超过π的区域抑制了复位脉冲的产生,避免了输入时钟边沿的丢失,从而完全消除盲区,加快了PLL的锁定速度。同时电路结构简单、易实现,可在快速锁定的锁相环中广泛应用。

2 鉴频鉴相器的非理想效应

PFD作为PLL的核心模块,由于具有较好的频率输入范围而得到广泛的应用,然而传统PFD存在一些非理想效应,会恶化锁相环路的性能,因此克服PFD的非理想效应对实现高性能锁相环非常关键。

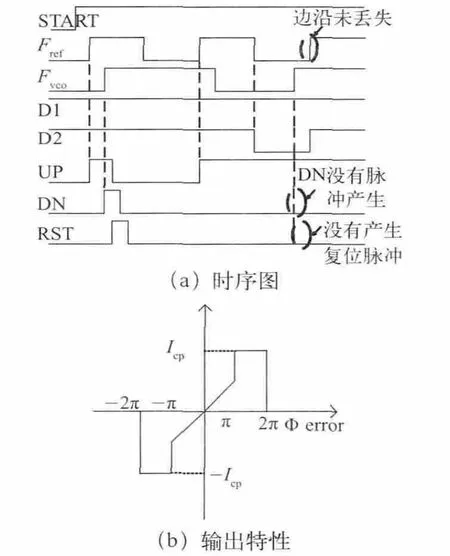

当输入信号相位差很小时,PFD无法鉴别相位差,导致输出电压很小,这种现象称为“死区”。传统PFD可以通过增加复位信号的脉宽来消除“死区”,因此,理想PFD的输出特性呈线性,如图1(a)所示。然而通过增加复位脉宽会使得鉴相范围减小,减慢捕获速度,严重限制了PFD的工作频率[8]。在设计时需要综合考虑“死区”与“速度”的矛盾。

另外,通过增加复位脉宽消除“死区”现象却带来了新的问题。当两个输入信号相位差接近2π时,在复位过程中来临的时钟边沿就会丢失,使得输出极性发生错误,如图2所示,这种现象称为“盲区”。盲区现象使得PFD的输出特性在2π附近出现恶化,如图1(b)所示。对于广泛采用的动态PFD可以工作在较高的频率,但当频率很高时,盲区的存在会严重影响PLL的锁定速度。

3 PFD的设计

3.1 传统PFD

PFD主要用来比较输入参考时钟Fref与反馈时钟Fvco的频率和相位,其输出为UP、DN信号,分别用来控制对电荷泵模块的充电与放电。当UP和DN信号均为高电平时,此时复位信号RST有效,UP和DN变为低电平,其中恢复过程的恢复时间用于消除PFD的死区问题。

图3为广泛使用的传统PFD电路。采用动态D触发器,具有结构简单、晶体管数目少、功耗低且工作频率范围广等优点。

图3 传统PFD电路实现

3.2 本文提出的PFD电路结构

本文提出的PFD电路结构如图4所示,电路结构中采用了反相器、与非门以及起始信号控制端对电路进行逻辑控制。该结构具有两种工作模式:

(1)当输入信号相位差小于π时,设计的PFD的工作模式与传统PFD完全相同。

(2)当输入信号相位差大于π时,和传统PFD不同,此时PFD电路的复位端口受反相器和与非门的控制,不再产生复位脉宽,从而避免了时钟边沿的丢失,完全消除了盲区。

图4 设计的PFD结构

电路具体工作过程如图4所示。初始状态时,信号控制端START置为低电平,经过与非门N4促使动态D触发器高电平复位有效,输出UP=DN=‘0’,D1=D2=‘1’。以反馈频率Fvco相位落后输入参考频率Fref为例,在Fvco上升沿到来之前,输出UP=‘1’,DN=‘0’。

当输入信号相位差小于π时,此时Fvco上升边沿对应的Fref=‘1’,经过反相器I1后Fref=‘0’,同UP=‘1’信号一起经过与非门N2后,输出D2=‘1’,Fvco上升沿到来时,DN=‘1’,产生复位信号,使UP=DN=‘0’,因此,此时PFD的工作模式与传统PFD完全一致。

当输入信号相位差大于π时,此时Fvco上升边沿对应的Fref=‘0’,经过反相器I1后Fref=‘1’,同UP=‘1’信号一起经过与非门N2后,输出D2=‘0’,Fvco上升沿到来时,输出DN维持低电平不变,不会产生脉冲,也就不会产生复位脉冲,所以此时复位信号无效;在这种情形下,时钟边沿将不会丢失,从而完全消除了盲区。同时输出端UP保持高电平不变,直到输入相位差缩小到小于π。设计的PFD结构电路时序和输出特性如图5所示。

图5 设计的PFD结构时序图和输出特性

3.3 设计的PFD结构的电路实现

设计的PFD结构中采用了TSPC D触发器,具有结构简单、工作速度快、低噪声以及低功耗的优点[10],如图6所示。在TSPC D触发器基础上增加P1和P2晶体管实现异步复位。RST高电平复位有效时,P1管导通,A=‘0’,B=‘1’,经过反相器后输出Q=‘0’;RST低电平时,P1截止,P2导通,电路为典型上升沿触发的TSPC D触发器。基于TSPC D触发器和与非门的晶体管级电路,本文设计的PFD电路如图7所示。

图6 TSPC D触发器

4 PFD的仿真与分析

利用Cadence Spectre软件工具,在SMIC 0.18 μm标准CMOS工艺下对设计的PFD电路进行仿真。图8验证了本文设计的PFD电路的两种工作模式。

图7 本文设计的PFD电路

由图8(a)所示,当相位差小于π时,PFD具有很好的鉴频鉴相器功能,其工作方式与传统PFD完全相同。同时PFD输出存在窄脉冲,有效地消除了死区,PFD的复位延迟Drst约为270 ps,根据PFD最大工作频率[11]fmax=1/(2×Drst)=1.852 GHz,保证了PFD较高的工作速度。由图8(b)所示,当相位差大于π时,Fref超前(落后)Fvco时,输出UP=‘1’(DN=‘1’),而DN(UP)不产生脉冲,维持DN(UP)=‘0’,复位端也不再产生脉冲,避免了时钟边沿的丢失和极性错误,从而完全消除了盲区。

为了比较设计的PFD和传统PFD两种电路结构对PLL锁定时间的影响,本文基于Verilog A语言对电荷泵、压控振荡器、分频器等模块进行了行为级建模,并据此设计了两个PLL,如图9所示。

图8 Fref与Fvco的时序图

除PFD模块外,其余模块完全相同。各模块参数如下:电荷泵充放电流Icp=130 μA;环路滤波器R=5 kΩ,C1=135 pF,C2=15 pF;压控振荡器增益Kvco=1 GHz/V;分频器为可编程整数分频。

图9 PLL锁定时间的测试平台

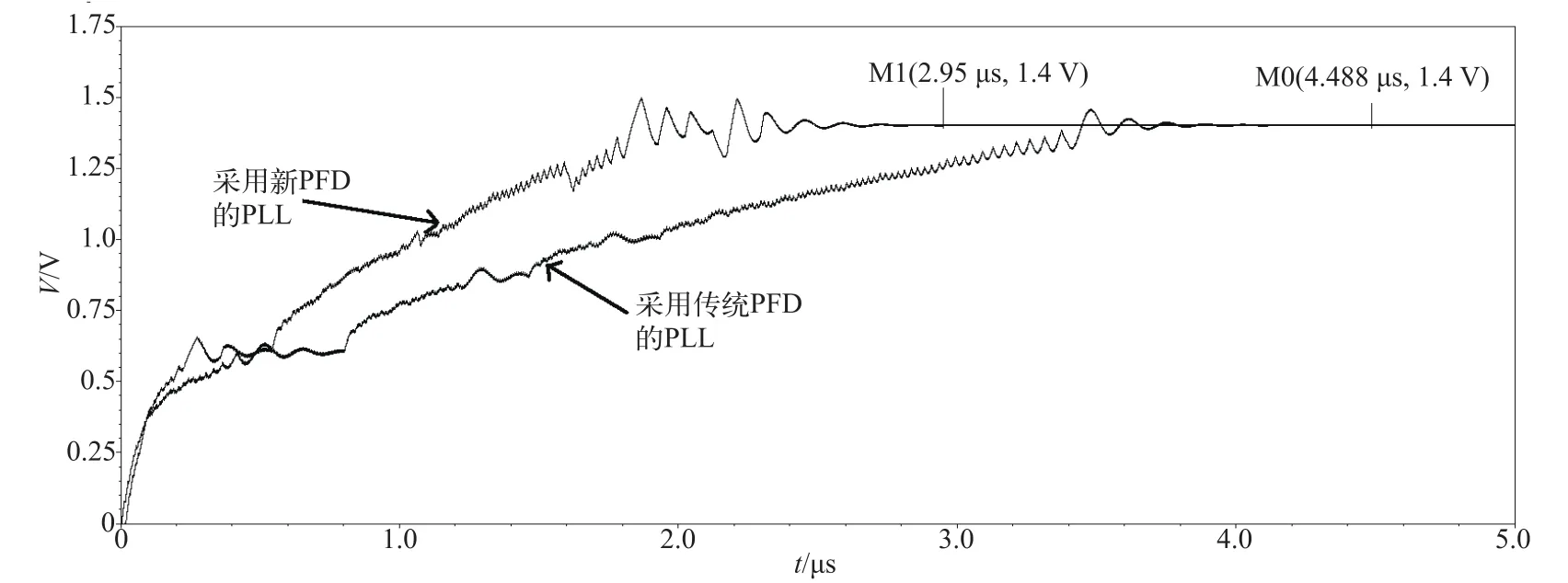

如图10所示为输入参考频率为400 MHz时,PLL环路中电荷泵输出的控制电压Vctrl的波形曲线。反馈频率低于参考频率时,电荷泵充电,Vctrl不断增大,控制VCO改变输出频率,使反馈频率不断接近参考频率,当最终反馈频率等于参考频率时,PLL处于锁定状态,控制电压Vctrl保持不变。由图中可以看出,采用本文设计的PFD的PLL锁定时间为2.95 μs,而传统PFD的PLL锁定时间为4.488 μs,锁定时间减小了34.27%。

图10 锁相环中控制电压Vctrl的波形曲线

表1为采用本文设计的PFD和传统PFD的两种PLL在不同参考频率下的锁定时间。对于传统PFD,输入参考频率越高,PFD复位期间出现盲区现象的可能性就越大,而本文设计的PFD完全消除了盲区,所以频率越高,该PFD减小锁定时间的效果更明显。表中不同频率对应的锁定时间可以说明这一点。

表1 不同参考频率下采用两种PFD的PLL锁定时间的比较

5 结论

本文设计了一种用于PLL快速锁定的PFD电路,其输出特性呈非线性。在相位差超过π时,输出恒定,有效地消除了盲区,加快了锁定速度。仿真结果表明,当输入参考频率为400 MHz时,采用本文设计的PFD的PLL比传统PLL锁定速度提高了34.27%,同时具有结构简单、容易实现、可广泛应用于快速锁定锁相环的特点。

[1] 樊勃,戴宇杰,张小兴,等. SOC用400~800 MHz锁相环IP的设计[J]. 微电子学,2008,38(5):743-747.

[2] Soyuer M, Meyer R G. Frequency limitations of a conventional phase-frequency detector [J]. Solid-State Circuits, IEEE Journal of, 1990, 25(4):1019-1022.

[3] LEE W H, LEE S D. A High Speed and Low Power Phase-Frequency Detector and Charge-pump [C]. Proc Asia South Pacific Design Automation Conf. Hong Kong,China. 1999:269-272.

[4] Zhang C, Syrzycki M. Modifications of a Dynamic-Logic Phase Frequency Detector for extended detection range [C]. Circuits and Systems(MWSCAS), 2010 53rd IEEE International Midwest Symposium on. IEEE,2010:105-108.

[5] Lee K S, Park B H, Lee H, et al. Phase frequency detectors for fast frequency acquisition in zero-dead-zone CPPLLs for mobile communication systems [C]. Solid-State Circuits Conference, 2003. ESSCIRC'03. Proceedings of the 29th European. IEEE, 2003:525-528.

[6] Kuo Y F, Weng R M, Liu C Y. A 5.4 GHz Low-Power Swallow-Conterless Frequency Synthesizer with a Nonlinear PFD [C]. Very Large Scale Integration,2006 IFIP International Conference on. IEEE, 2006:357-360.

[7] Chih J C, Chiu C T, Wu J M, et al. Piecewise-linear phase frequency detector for fast-lock phase-locked loops[C]. Circuits and Systems(MWSCAS), 2011 IEEE 54th International Midwest Symposium on. IEEE, 2011:1-4.

[8] 魏建军,李春昌. 动态饱和鉴相鉴频器[J]. 西北工业大学学报,2010(002):286-290.

[9] Lan J, Lai F, Gao Z, et al. A nonlinear phase frequency detector for fast-lock phase-locked loops [C]. ASIC, 2009.ASICON'09. IEEE 8th International Conference on. IEEE,2009:1117-1120.

[10] 吴昊,吴秀龙. 低抖动的鉴频鉴相器设计[J]. 电脑知识与技术(学术交流),2007,4(20).

[11] Hu W, Chunglen L, Wang X. Fast frequency acquisition phase-frequency detector with zero blind zone in PLL [J].Electronics Letters, 2007, 43(19):1018-1020.