一种具有高线性度MOS采样开关的采样保持电路*

吴楚彬,张 章,於昌虎,解光军

(合肥工业大学电子科学与与应用物理学院,合肥230009)

随着CMOS集成电路工艺的迅速发展,尤其是片上系统SoC(System-on-a-Chip)的发展,对模数转换器(ADC)的要求越来越高。在各种结构的模数转换器中,流水线ADC因其精度和采样率的有效折中而得到了广泛的应用。其中高速、高精度的前端采样保持电路是流水线ADC的重要组成部分,其动态性能直接影响流水线ADC的性能。而采样保持电路的性能受到多种因素的制约,包括运放、开关等。随着采样时钟频率的提高和电源电压的持续下降,传统的MOS采样开关的线性度不断降低,限制了采样保持电路的性能的提高,使之无法满足高速、高精度ADC对采样信号的精度及非线性的要求。

MOS采样开关的非线性主要是由开关导通电阻的非线性引起的。常用的减小导通电阻非线性的两种方法为:采用互补性的CMOS开关[1];采用栅压自举采样开关[2-3]。这两种方法虽然在一定程度上减小了由采样开关的栅源电压随输入信号的变化而产生的非线性,但却无法消除由MOS开关阈值电压的衬偏效应产生的非线性,从而限制了MOS采样开关动态范围的进一步提高。文献[4]中提出了基于运放反馈的采样开关电路,可以显著地消除MOS开关阈值电压的衬偏效应产生的非线性,但是存在两个问题,一是采用额外的运放,极大的提高了开关的功耗,二是该种结构的工作信号范围有限。

本文基于文献[4]中的采样开关电路结构,提出了一种新颖的采样保持电路。通过将采样保持电路中的运放复用,在提高采样开关导通电阻线性度的同时,省去了采样开关中的运放,解决了高线性度采样开关功耗较大的问题;通过增加一个自举电容,提高开关管栅极电压,使得采样开关的信号工作范围显著提高。

1 采样开关中的非线性分析

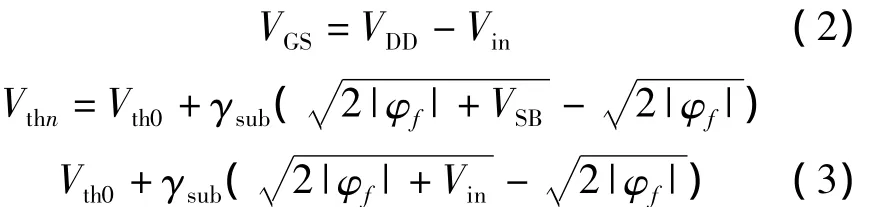

采样保持电路的非线性主要来源于MOS采样开关导通电阻的非线性。对于单个NMOS管构成的开关,当栅极电位为高电平时,工作在线性区,其导通电阻为[5]:

其中:

式中,Vthn为NMOS管的阈值电压,Vth0为NMOS管源和衬底之间电压为0时的阈值电压,γsub为体效应系数,φf为费米势。

由式(1)~式(3)可以看到,NMOS管的导通电阻不但与栅源电压VGS有关,同时还与阈值电压Vthn有关,而这两者又与输入信号有关,所以它们的变化都会在导通电阻上引入非线性。

2 减小采样开关非线性的方法

互补型CMOS采样开关是减小开关导通电阻非线性的常用方法之一,它由一对NMOS管和PMOS管并联组成,其中NMOS管和PMOS管的栅极电压由一对互补时钟控制,在采样开关导通阶段,导通电阻为两管导通电阻的并联,通过选择适当的两管的宽长比,使得互补型CMOS采样开关的导通电阻与输入信号无关。然而,在实际中,由于衬偏效应的影响,NMOS管和PMOS管的阈值电压Vthn,Vthp都会随输入信号的变化而变化,从而在开关的导通电阻中引入非线性,限制了CMOS采样开关的线性度,使得这种开关结构不能适用于高速、高精度的ADC中。

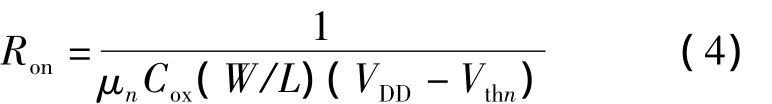

传统的MOS栅压自举采样开关是减小开关导通电阻非线性的另一种常用的方法,如图1所示,它通过自举电容C来固定开关管的栅源电压VGS,有效地解决了栅源电压VGS随输入信号变化的影响。在采样阶段,采样开关的导通电阻为:

这种传统的栅压自举开关消除了MOS管由于栅源电压随输入信号变化而引入的非线性,提高了采样开关的动态范围。然而,阈值电压随输入信号变化而产生的非线性仍然没有得到消除,因此限制了MOS采样开关线性度的进一步提高。

图1 传统的栅压自举采样开关

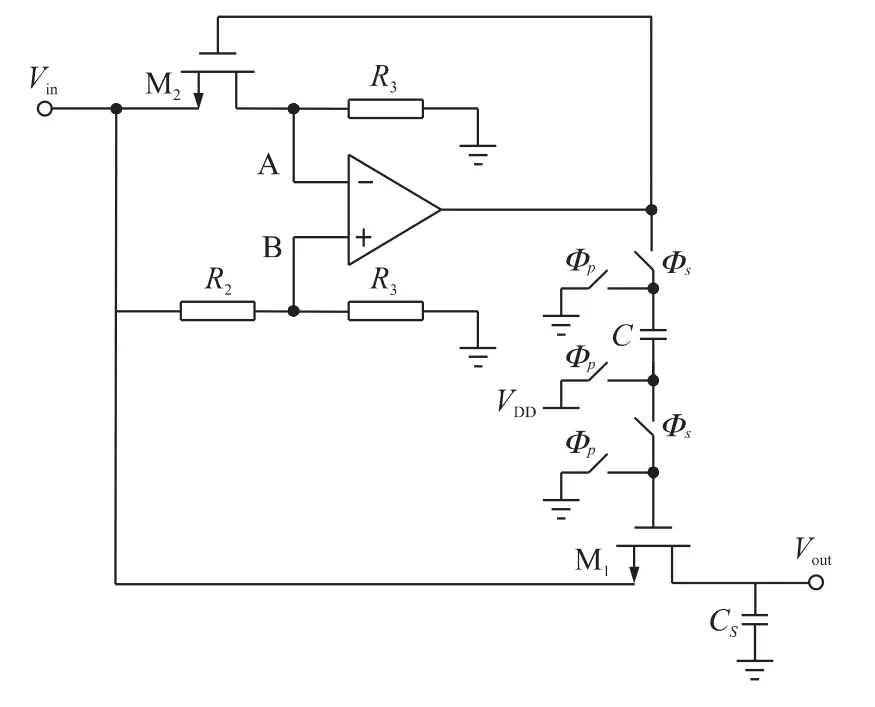

为了消除阈值电压随输入信号变化而产生的非线性,文献[4]提出了一种新型的高线性度MOS采样开关,如图2所示。通过电阻分压,产生一个工作在线性区的“复制”MOS管,它与采样开关管具有相同的阈值电压。这种结构设计的思想是通过固定MOS采样开关的过驱动电压VGS-Vthn,使得导通电阻趋于恒定。

电路的工作原理如下:在 Φp高电平期间,M1的栅极接地,C两端电压充电至VDD;在Φs高电平期间,C两端分别接M1的栅极和M2的栅极,并保持两端电压为VDD,即:

图2中,运放始终在闭环状态下工作,如果增益足够大,则正向输入端电压等于负向输入端电压,即VA=VB。选择合理的宽长比,使得M2工作在线性区,则其电阻可以表示为:

图2 文献[4]中所提出的MOS采样开关

因此,可以得到M2的栅极电压为:

由于M1和M2的阈值电压相等(Vth1=Vth2),并由式(5)~式(7)可得M1的导通电阻为:

由式(8)可知,此时MOS开关导通电阻不再受栅源电压变化以及阈值电压变化的影响,这两个非线性源都得到了有效的抑制,从而得到了一个导通电阻恒定的采样开关。但由于这种开关结构需要使用运放,必然会增加整个结构的功耗和面积。并且为了保证开关管一直工作在线性区,且过驱动电压(Vdsat)不变,则要求运放有较高的共模输出以及较大的输出摆幅,从而增加了运放设计难度。

3 高线性度采样开关的采样保持电路

采样开关是ADC前端采样保持电路的一个关键模块,本节介绍所提出的具有高线性度采样开关的采样保持电路。由于采样保持电路中的运放仅工作在保持相位,而图2所示的采样开关结构中,运放仅工作在采样相位,因此,利用运放复用的思想,可以省去开关中的运放。又图2所示的开关要求运放有高的共模输出以及较大的输出摆幅,而采样保持电路中的运放输出共模电压为有效信号范围的中间值,相对来说不是很高,且摆幅也相对有限。通过在运放的输出端与采样开关之间增加一个自举电容,可以保证在运放输出共模较小的情况下,采样开关处于线性工作区。同时,为了满足此开关结构对运放高的输入输出共模范围的要求,这里需要使用一种特殊的运放结构,即高共模输入输出且跨导恒定的运放[6-8]。

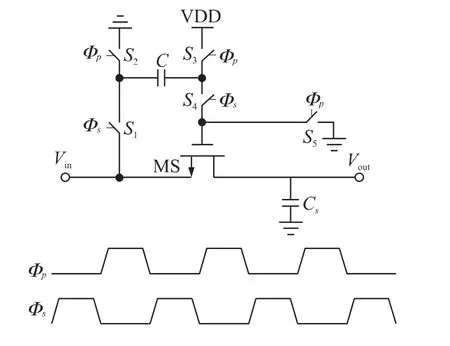

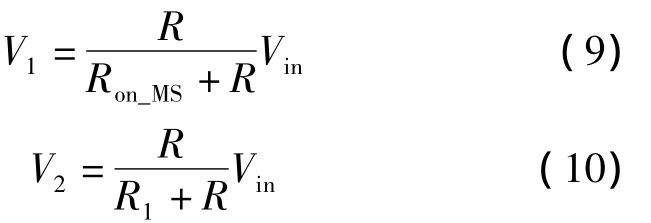

基于图2所示的开关结构,通过运放的复用,将其改进为具有高线性度采样开关的采样保持电路,如图3所示。图4为其不同阶段的工作原理图。

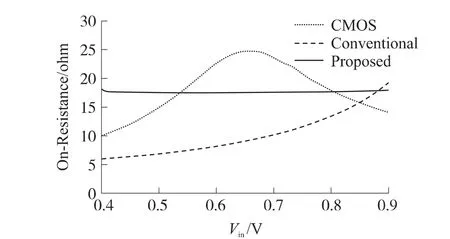

电路的工作原理如下:当Φs为高电平时,电路处于采样阶段,其等效电路如图4(a)所示。运放的同相端接电阻R与R1产生的分压V2,反相端接采样开关MS与电阻R产生的分压V1,输出端接自举电容C的一端,自举电容的另一端接到采样开关的栅极,形成负反馈。通过运放自动调节采样开关的栅极电压,使栅源电压VGS的变化能够抵消阈值电压的变化,从而最大限度地消除导通电阻的非线性,使得采样开关的导通电阻接近于目标电阻。在运放增益足够大的情况下,运放两个输入端的的电压近似相等,即V1≈V2,其中

取R≥R1,则V1≈V2≈Vin,R1的阻值即为采样开关MS导通电阻的目标阻值Ron_MS。通过采样开关后的信号压降受R和R1大小的影响,选取合理的R1值,使得采样开关的导通电阻和采样电容构成的RC时间常数满足所设计的ADC的指标要求。同时采样开关也要选取适当的宽长比,使运放在能提供相应的栅极电压的情况下,导通电阻可以达到目标阻值。

图3 本文提出的新型采样保持电路

图4 不同阶段的工作原理图

当Φp为高电平时,电路处于保持阶段,其等效电路如图4(b)所示。运放的同相端接共模电平(Vcom),反向端以及输出端分别接采样电容Cs的两端,使得采样电容采样到的电压值翻转到输出端,实现保持功能。同时,在这个阶段,自举电容C的两端分别接电源电压(VDD)和地,以提供采样阶段时的自举电压,保证开关管MS工作在线性区。

综上所述,本文提出的新型采样保持电路,通过运放的复用技术,使得在采样阶段,利用运放的负反馈来获得一个高线性度的采样开关,从而消除了开关MOS管阈值电压变化而引入的非线性。

4 仿真结果

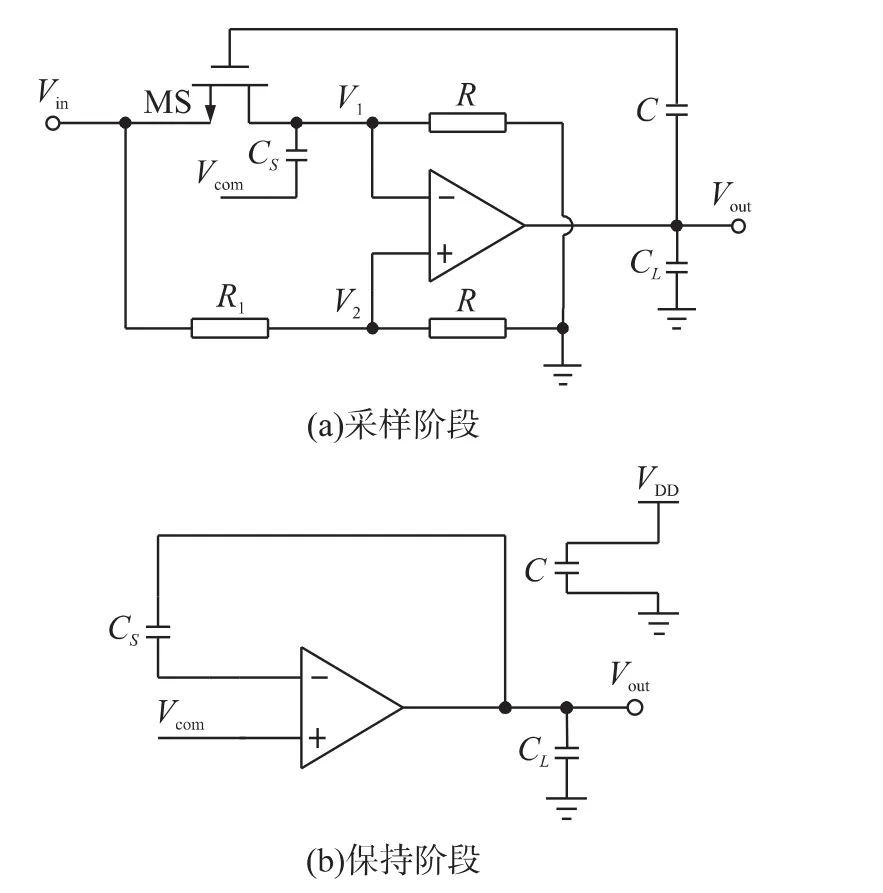

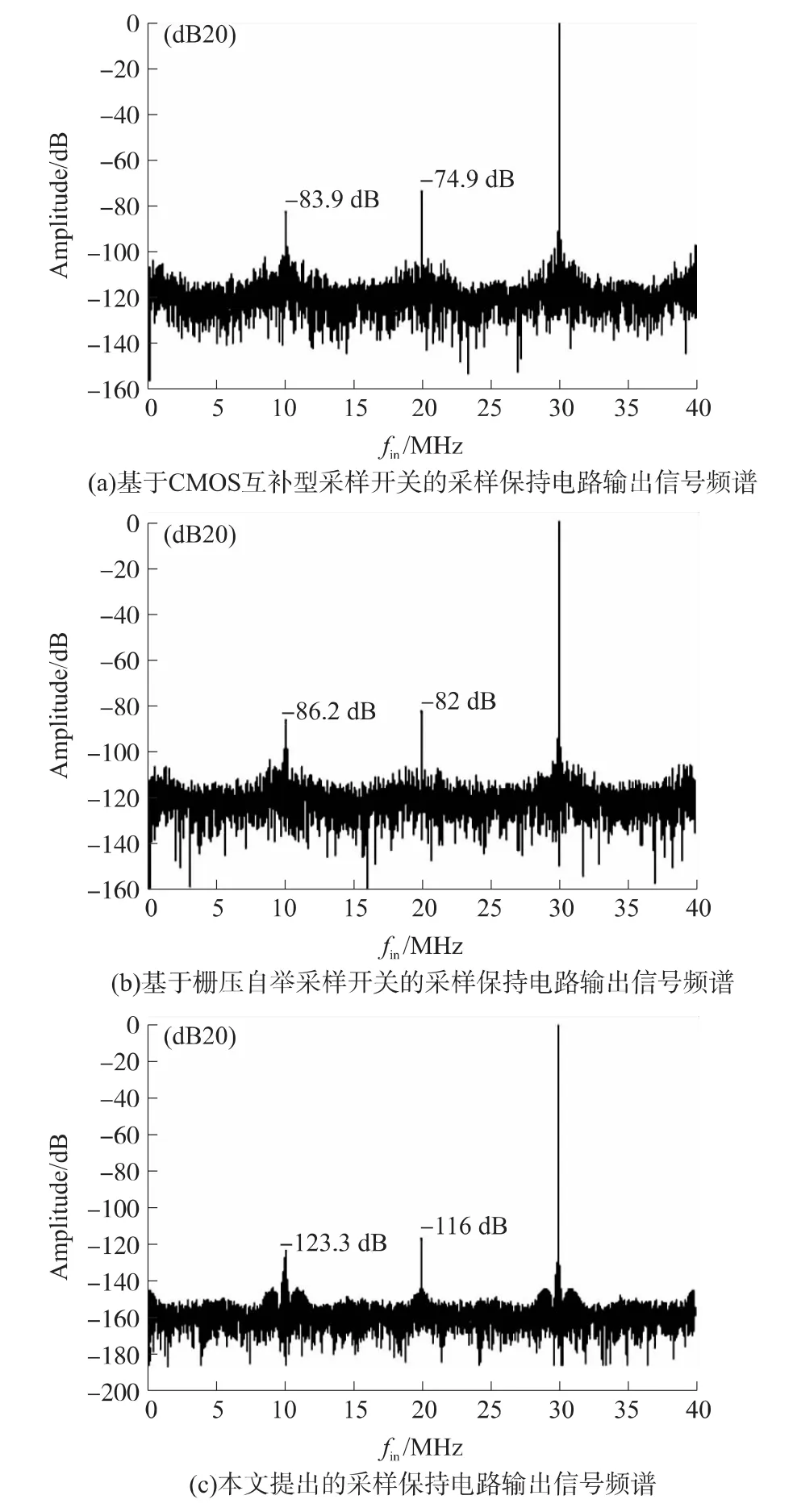

本文电路采用 SMIC 0.13 μm标准 CMOS工艺,在Cadence Spectre软件环境下对电路进行设计和仿真。作为对比,分别设计了基于互补型CMOS采样开关的采样保持电路、基于传统栅压自举开关的采样保持电路和本文提出的采样保持电路。这里为了简单验证所提出的采样保持电路的性能,使用了理想的运放,其性能为:开环增益100 dB,开环带宽600 MHz。电阻阻值的选取为R1=18 Ω,R=10 kΩ。3种结构采样开关的尺寸都选取为:宽为80 μm,长为0.13 μm。3种结构的采样电容和负载电容都为1 pF,栅压自举电路以及本文提出的电路结构中自举电容都为1 pF。电源电压1.2 V。在输入信号为30 MHz、0.5Vpp,采样时钟为80 MHz情况下,分别对三种结构的采样保持电路进行了仿真,比较了它们采样阶段的采样开关导通电阻及保持阶段输出信号的频谱性能,分别如图5、图6所示。

图5 各种结构采样保持电路的导通电阻随输入信号的变化

从图5可以看到,采样开关导通电阻的阻值在整个信号输入范围内都平稳地处于目标电阻阻值18 Ω附近,其中从仿真数据分析得到大约只有0.2 Ω的变化;同样从图4也可以看到,CMOS采样开关以及栅压自举开关的导通电阻变化比较大,有10 Ω以上;因此,本文提出的结构中的采样电阻具有很高的线性度。

从图6可以看到,本文提出的采样保持电路在保持阶段输出信号的无杂散动态范围SFDR达到了116 dB,而采用CMOS开关和栅压自举开关的采样保持电路的SFDR分别只有74.9 dB和82 dB,即这种结构的采样保持电路的性能得到了显著的提高。和文献[4]中的采样开关的性能对比,本文的采样开关导通电阻目标阻值与其相等,从仿真结果分析,本文也达到了这个目标阻值的要求;而对于信号频谱的分析,本文也是在30 MHz、0.5Vpp输入信号,80 MHz采样时钟下进行的,所提出的采样保持电路的频谱性能达到了SFDR=116 dB,而文献[4]在考虑失配的情况下达到了92.7 dB,所以其频谱性能也是相当的。

图6 各种结构采样保持电路输出信号的频谱

这里不同的是,本文的采样保持电路通过运放的复用,在得到高线性度采样开关的同时,也提高了运放的利用率,总体上节省了功耗。因此,这种结构为采样保持电路的研究提供了一种新的思路。

5 结论

本文提出的采样保持电路,通过运放的复用技术,得到了一个高线性度的采样开关,消除了采样开关由于栅源电压VGS以及阈值电压Vthn随输入信号变化而带来的非线性,并且降低了功耗,显著的提高了采样开关的线性度。本文提出的采样保持电路在采样阶段,导通电阻大约只有0.2 Ω的变化,输出信号的无杂散动态范围SFDR达到了116 dB。为实现高性能的采样保持电路提供了一种新的思路。

[1]Allen P E,Holberg D R.CMOS Analog Circuit Design[M].New York:Holt,Rinehart and Winston,1987.

[2]李锋,黄世震,林伟.一种用于流水线ADC采样保持电路的设计[J].电子器件,2010,33(2):170-173.

[3]郑晓燕,王江,仇玉林.低电压低功耗CMOS采样保持电路[J].电子器件,2006,29(2):318-321.

[4]彭云峰,严伟,陈华,等.一种新型高线性度 MOS采样开关[J].微电子学,2006,36(6):774-778.

[5]Razavi B.Principles of Data Conversion System Design[M].IEEE Press,Piscataway,NJ,1995.

[6]夏斯青,高怀.应用于包络跟踪的高线性跨导运算放大器的设计[J].电子器件,2012,35(5):530-534.

[7]余国义,张乐,郑梅军,等.一种新型超宽共模输入范围放大器设计[J].电子器件,2012,35(5):504-508.

[8]李志远,王永生.一种低噪声轨对轨输入CMOS运算放大器设计[J].电子器件,2007,30(6):2023-2027.