MLC型NAND闪存的比特翻转译码算法研究

张 旋,李晓强

(西安理工大学,陕西 西安 710082)

MLC型NAND闪存的比特翻转译码算法研究

张 旋,李晓强

(西安理工大学,陕西 西安 710082)

随着闪存编程/擦除循环次数的增加,多级单元(Multi-Level Cell, MLC)的氧化隔离层被破坏,进而导致闪存的可靠性急剧降低。针对这种情况,在深入分析MLC闪存信道模型和数据保持噪声模型的基础上,提出了一种MLC型NAND闪存的比特翻转译码算法。仿真结果表明,在MLC闪存信道下,该方法既可保证闪存单元的可靠性,又具有较短闪存单元的读取时间,从而实现了译码复杂度和性能间的良好折衷。

多级单元;低密度奇偶校验码;比特翻转译码算法

0 引言

NAND闪存作为一种非易失性存储器,由于其体积小、容量大和功耗低等特点,已广泛应用于各种移动设备中。多级单元(Multi-Level Cell, MLC)技术成为提高NAND型闪存数据容量和降低成本的有效手段。然而,由于MLC单元内部通过增加电压等级(Voltage Level)数量来提高存储密度,使得单元内的阈值电压分布窗口缩小。随着闪存单元编程/擦除(Program/Erase, P/E)次数的增多导致MLC的氧化隔离层被破坏,进而MLC闪存更容易发生读写错误。因此,MLC型NAND闪存的可靠性面临严峻挑战[1]。

BCH码由于具有良好的纠错能力,已经广泛应用于单级单元(Single-Level Cell, SLC)NAND闪存中。但是,随着NAND闪存封装尺寸减小和MLC技术的应用,BCH码已不能满足MLC型NAND闪存的可靠性要求。逼近香农限的LDPC码,由于其在迭代译码下拥有非常好的纠错性能,已成为提高MLC型NAND闪存可靠性的研究方向之一[2-4]。LDPC码的迭代译码算法包括软判决译码算法和硬判决译码算法。文献[5]利用闪存信道的统计信息获得更好的LDPC码软判决译码性能。软信息的精确计算能够为LDPC码译码提供更高的译码性能,但这也导致闪存控制器需要消耗的感知时间和译码时间增多,影响闪存单元的读取速度。本文算法是将LDPC码比特翻转(Bit-Flipping, BF)硬判决译码算法应用到NAND闪存中,该算法不但硬件实现简单,还可以大幅减少译码时延从而加快数据读取速度,为高密度NAND闪存提供更高效的差错控制方案。

1 MLC型NAND闪存

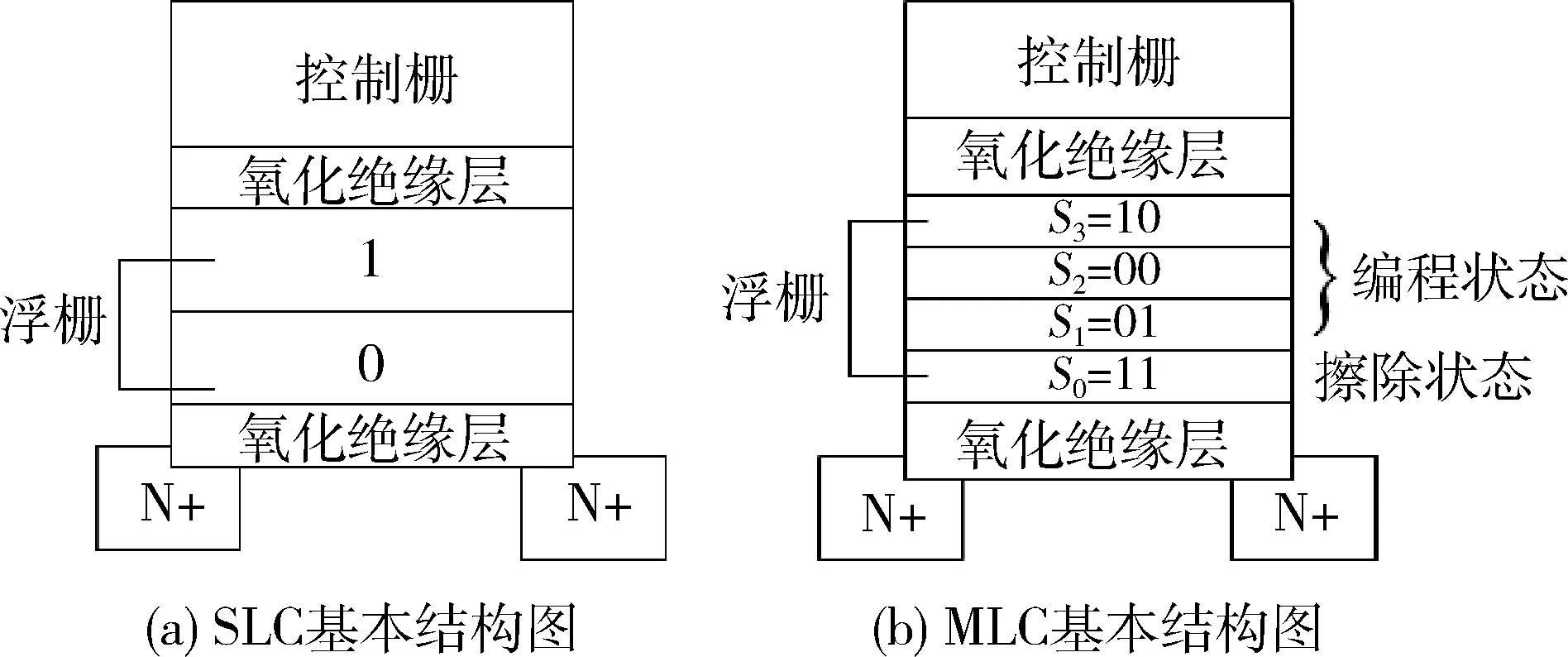

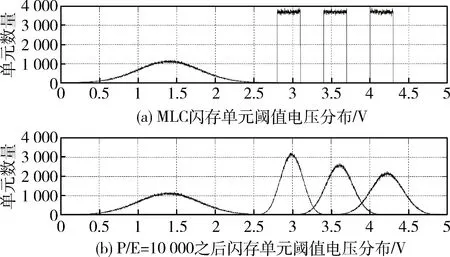

NAND闪存的最小存储单元是带浮栅(Floating Gate)的MOS晶体管。其中浮栅被氧化绝缘层隔离,电荷注入其中可以长期稳定保存。浮栅中电荷数量决定闪存单元的阈值电压,不同的阈值电压可以映射为不同的状态,从而表示不同的数据[6]。传统的闪存单元采用SLC,由浮栅中是否有电荷来表示“0”和“1”,因此,SLC中只存储1 bit信息。MLC包含4个电压等级,不同的阈值电压水平表示不同数据(s0=11,s1=01,s2=00,s3=10),进而存储2 bit 信息(如图1所示)。

MLC型NAND闪存芯片的层级组织结构依次是:阵列(Array)、块(Block)、页(Page)和单元(MLC)。每个块通常由16、32或者64页构成,而每页大小从512 B~8 KB不等,页是闪存编程和读取的最小单位。

图1 SLC和MLC闪存基本结构图

1.1MLC阈值电压模型建立

MLC闪存在擦除操作之后阈值电压服从高斯分布。因此用式(1)表示MLC闪存单元擦除状态(Erase State)的阈值电压分布(s0=11表示擦除状态)[7]:

(1)

其中,μe和δe是删除状态阈值电压的均值和标准方差。

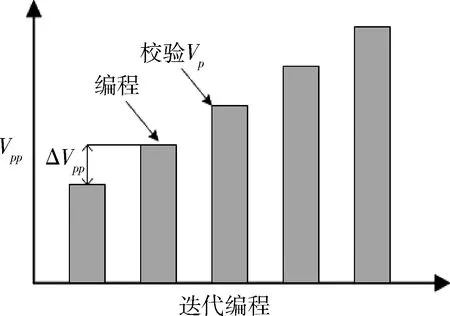

(2)

图2 编程/校验迭代编程操作

1.2噪声模型的建立

μr=Ks(x-x0)KdN0.5ln(1+t/t0)

(3)

(4)

其中Ks、Kd、Km和t0为常量,N表示P/E循环次数,x0表示擦除状态下单元阈值电压的初值,x表示编程后的阈值电压,而t表示时间。

MLC阈值电压模型参数设置为:擦除状态阈值电压分布概率密度函数ps0(x)的均值μe=1.4,标准差σe=0.4,迭代编程步长电压增量ΔVpp=0.3 V,三个编程状态的校验电压Vp分别为2.8 V、3.8 V和4.0 V。数据保持噪声参数分别设置为Ks=0.38,x0=1.4,Kd=4×10-4,Km=4×10-6,t0=1 h,其中P/E循环次数N=10 000,数据保持时间t=1 year。

对10个闪存块,每块32页,每页17 260个MLC进行100次蒙特卡洛仿真,统计得到加入数据保持噪声的单元阈值电压分布直方图统计结果(如图3所示),图3(a)为无干扰的单元阈值电压分布,图3(b)为加入数据保持噪声之后的MLC闪存阈值电压分布。由图3(b)分析可得,NAND闪存在加入随机数据保持噪声后,MLC闪存单元阈值电压会发生波动,编程状态的单元阈值电压会向相邻状态发生偏移,相邻的阈值电压分布出现重叠区域,位于此区域的MLC单元在判决时出错概率较高,进而导致错误读取存储的数据。

图3 MLC闪存加入数据保持噪声后单元阈值电压分布

2 MLC闪存的比特翻转硬判决译码方案

2.1MLC阈值电压的多精度感知

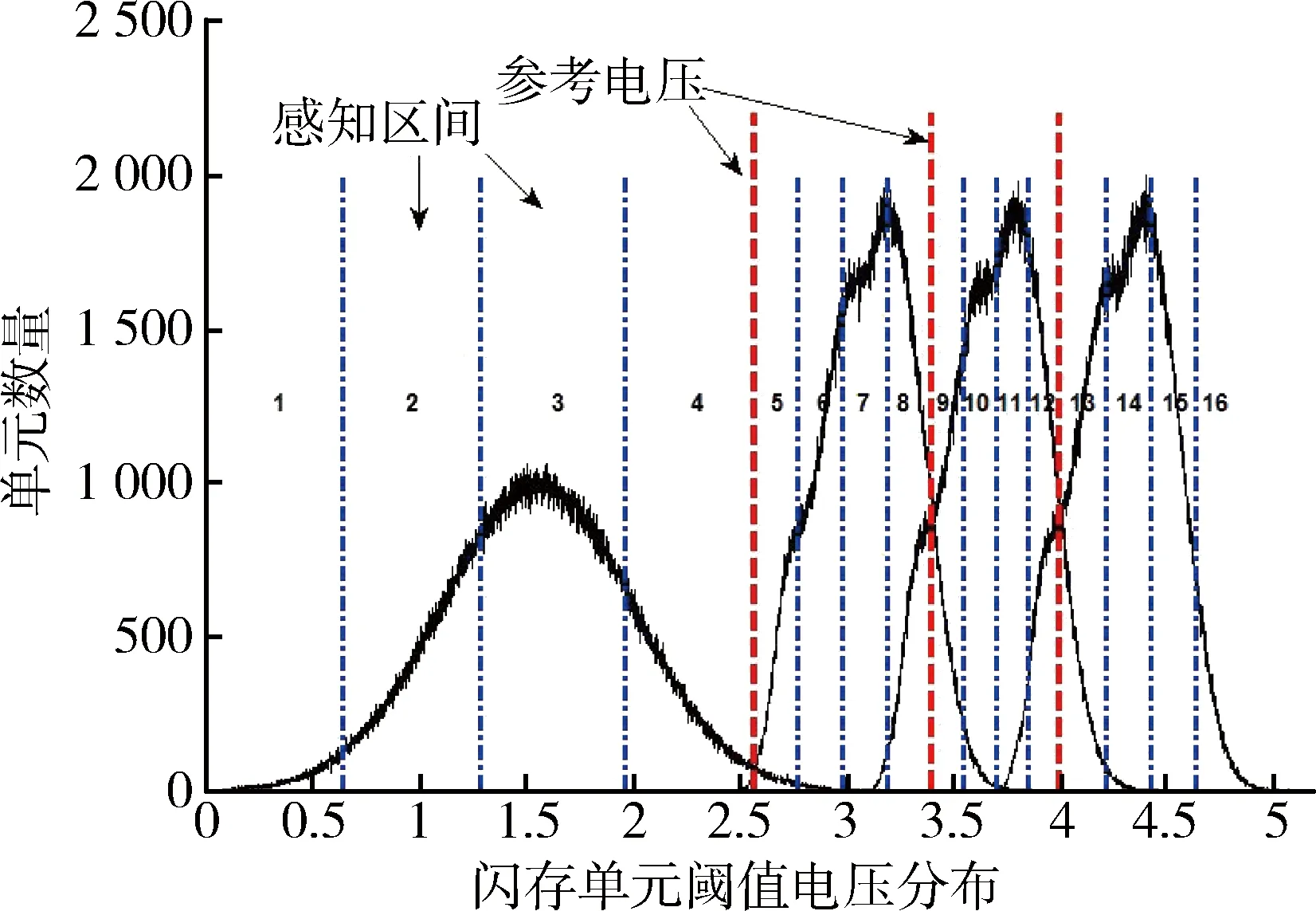

读取闪存单元中数据需要对MLC单元阈值电压感知。为了准确地感知MLC阈值电压,通常采用多精度的软感知方法[7]。将每个阈值电压状态分布用若干个参考电压均分成多个小区间,参考电压越多,划分的区间越窄,感知的阈值电压越精确。通常将感知精度表示为p(p>2),对应的参考电压数量为2p-1,单元阈值电压分布区间数量为2p。图4为感知精度p=4时的阈值电压区间均匀划分。感知时从低电压区间向高电压区间逐个检测,判断MLC阈值电压所在的区间,从而得到一个区间范围[Rl,Rr)。

图4 感知精度p=4时阈值电压区间均匀划分

对于每单元存储2 bit的MLC,每个闪存单元有4个状态(s0=11,s1=01,s2=00,s3=10),左侧的比特称为最高有效位(Most Significant Bit,MSB),右侧的比特称为最低有效位(Least Significant Bit,LSB),分别通过式(5)和式(6)计算出最高有效位MSB与最低有效位LSB的LLR值[7]。

(5)

(6)

2.2MLC闪存的比特翻转译码算法

比特翻转译码算法是基于LDPC码的迭代译码算法,它具有较低的译码时间复杂度,比软判决译码速度快的优点,能有效缩短闪存单元的读取时间[8-9]。同时在不同的数据保持噪声干扰强度下,采用不同的闪存单元阈值电压感知精度,可进一步提升比特翻转译码算法的译码性能。

具体步骤如下:

(1) 根据2.1节方法对MLC闪存单元阈值电压进行感知精度为p的感知,得到MLC的阈值电压Vth。

(2) 通过式(5)和式(6)计算出Vth所对应的MSB和LSB对应LLR值。

(3) 比特信息的硬判决(i=0,1,…,N-1)。

(4) 计算校验和,如果所有的校验方程都满足,则译码成功;否则,重复步骤(5)~(7)。

(5) 计算每一比特对应“不满足校验方程的个数”,记作fi。

(6) 找出fi值最大的比特,对其进行翻转。

(7) 直到所有的校验方程都满足(译码成功)。若达到迭代次数设定的上限,增大感知精度p++(p≤5),转步骤(1);否则译码失败。

3 仿真实验分析

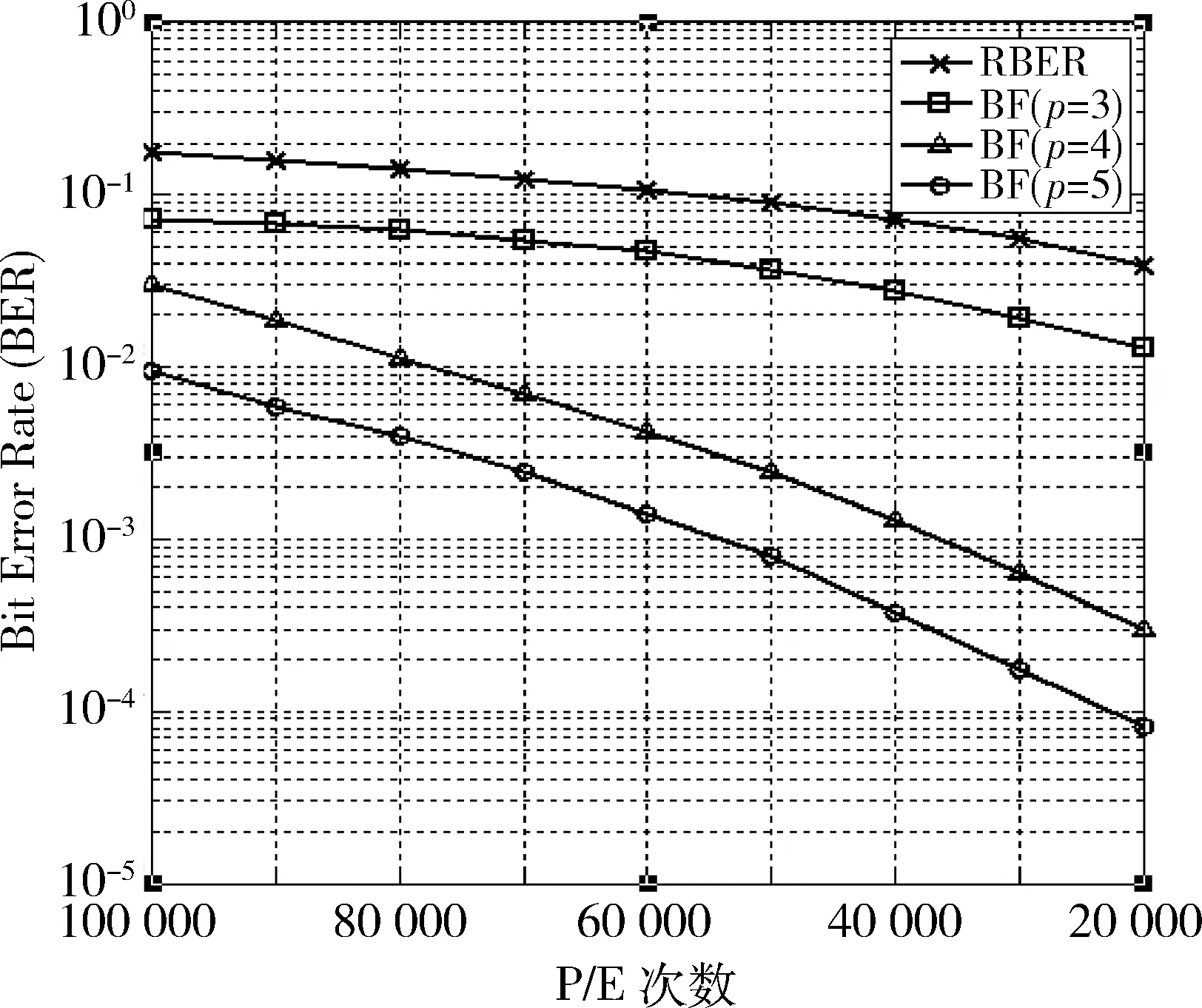

考虑到闪存存储效率,一般选取高码率的LDPC码。为了在闪存信道中对LDPC码比特翻转译码算法进行性能仿真,选取两种码率较大的QC-LDPC码,该仿真实验使用码率为0.95(34 520,32 794)的C1和码率为0.9 (34 520, 32 794)的C2,列重为4,环长为6,该码避免了迭代译码过程中出现的短环,可以提高迭代译码的性能,最大迭代次数为50。MLC信道模型参数和数据保持噪声参数设置与1.2节相同。

图5和图6分别为感知精度p=3、4和5时BF译码算法在不同P/E次数下的性能图,仿真结果表明:

(1) 在闪存信道下对于码字C1和C2,LDPC码比特翻转译码算法能有效降低码字的误比特率,提高闪存存储系统的可靠性。

(2) 在感知精度为p=3、4和5时,对应的阈值电压分布区间分别被划分为8、16与32个小区间。在相同的P/E次数下,感知精度越高,即闪存单元阈值电压分布中参考电压越多,阈值电压分布区间划分越细,相应的LLR值越精确,比特翻转译码算法的译码性能越好。

图5 闪存信道中码C1在BF译码算法下的译码性能

图6 闪存信道中码C2在BF译码算法下的译码性能

4 结束语

对闪存进行P/E循环次数的增多,MLC的氧化隔离层被破坏成为影响MLC型NAND闪存可靠性的主要因素,本文提出了一种MLC型NAND闪存比特翻转硬判决译码方法。该方法具有低的译码复杂度,而且易于工程实现,同时达到译码复杂度和性能间的良好折衷。仿真结果验证了所提出方法的有效性。

[1] CAI Y, HARATSCH E F, MUTLU O, et al. Error patterns in MLC NAND Flash memory: measurement, characterization, and analysis[J]. Seminars in Roentgenology, 2012, 5(3):245-259.

[2] WANG X, DONG G, PAN L, et al. Error correction codes and signal processing in Flash memory[M]. Flash Memories. In Tech, 2011.

[3] SALA F, IMMINK K A S, DOLECEK L. Error control schemes for modern Flash memories solutions for flash deficiencies[J]. IEEE Consumer Electronics Magazine, 2015, 4(1): 66-73.

[4] GUO J, WANG D, SHAO Z, et al. Data-pattern-aware error prevention technique to improve system reliability[J]. IEEE Transactions on Very Large Scale Integration Systems, 2017,25(4): 1433-1443.

[5] WANG J, DONG G, COURTADE T, et al. LDPC decoding with limited-precision soft information in Flash memories[J]. International Journal of Technology in Teaching & Learning, 2012:652-657.

[6] CAI Y, HARATSCH E F, MUTLU O, et al. Threshold voltage distribution in MLC NAND Flash memory: Characterization, analysis, and modeling[C].Design, Automation & Test in Europe Conference & Exhibition. IEEE, 2013: 1285- 1290.

[7] DONG G, XIE N, ZHANG T. On the use of soft-decision error-correction codes in NAND flash memories[J]. IEEE Transactions on Circuits and Systems I: Regular Papers, 2011, 58(2): 429-439.

[8] GALLAGER R. G. Low-density parity check codes[D]. Massachusetts: M.I.T. Press, 1963.

[9] 屠亮亮,徐荣青. 基于LDPC硬判决算法的高效数据协调方法[J].微型机与应用, 2016,35(12):67-69.

Research on bit-flipping decoding algorithm for MLC NAND Flash memory

Zhang Xuan, Li Xiaoqiang

(Xi’an University of Technology, Xi’an 710082, China)

With the increase of the number of program/erase cycles, the oxide isolation layer of multi-level cell(MLC) is destroyed and the reliability of the flash memory is reduced sharply. By making a thorough analysis of MLC channel model and data retention noise, a bit-flipping decoding algorithm is presented for MLC NAND flash memory. The simulation results show that this method can ensure the reliability of flash memory, and has a short access time, so as to achieve a better tradeoff between decoding complexity and decoding performance.

multi-level cell; low-density parity-check codes; bit-flipping decoding algorithm

TP393.0

A

10.19358/j.issn.1674- 7720.2017.19.008

张旋,李晓强.MLC型NAND闪存的比特翻转译码算法研究[J].微型机与应用,2017,36(19):27-29,33.

2017-04-12)

旋(1980-),男,硕士,讲师,主要研究方向:计算机网络与差错控制编码。李晓强(1980-),男,硕士,讲师,主要研究方向:计算机网络。