DICE加固结构触发器的重离子实验研究*

张筱颖,田海燕,于宗光*

(1.江南大学物联网工程学院,江苏无锡214122;2.中国电子科技集团公司58所,江苏无锡214035)

重离子会导致航天器系统中的半导体器件发生单粒子效应SEE(Single Event Effect),随着电路工艺尺寸的降低和集成度的提高,SEE对电子器件的影响已愈发严重,其中的单粒子翻转SEU(Single E-vent Upset)作为导致集成电路出现故障的主要辐射原因已成为现今抗辐照加固研究的热点[1-3]。

D触发器作为CMOS集成电路中使用很广泛的单元,是很容易发生SEE的,当触发器电路受到重离子的干扰,单元中存储的数据会发生错误,并且存储的错误数据会一直保留到该单元下一次被改写,这会影响电路的正常工作[4],因此触发器单元抗辐照能力的强弱会直接影响整个电路的抗辐照性能[5-7]。

实验主要是对DICE加固结构触发器进行重粒子研究,分别选用氯(Cl)、锗(Ge)、碘(I)这3种不同的重粒子在不同频率、不同驱动能力、不同版图结构、不同电压这4种情况下对电路进行单粒子辐照试验,分析电路翻转的次数及翻转阈值,以此来验证电路抗SEU性能的有效性。

1 单粒子效应产生机制

单粒子效应SEE(Single Event Effect)是指高能粒子入射到半导体器件内部时会在穿透路径上发生电离,此时电路中的结点会因为吸收电离所产生的电子或空穴而改变原来自身的电位[8-9],导致电路出现故障,影响器件的可靠性。

作为单粒子效应中的主要内容,单粒子翻转SEU(Single Event Upset)大多发生在存储器件和逻辑电路中,表现为电路中触发器和存储单元的翻转、逻辑错误等[4,10]。它的产生是因为入射的高能粒子对集成电路的敏感结点撞击从而导致硅材料电离,并在重离子运动径迹周围形成大量的电荷,当结点上积淀的电荷达到临界状态时,就会产生瞬态电流来触发逻辑电路,导致逻辑状态发生改变,错误的逻辑电平会导致电路发生“软”失效[11-12]。

2 DICE加固结构触发器

文献[13]和文献[14]中提到,在 0.18 μm 的工艺条件下,双互锁存储单元DICE(Double Interlocked Storage Cell)结构具有好的抗SEU的效果,该电路不但具有高速、低功耗等特点,而且当电路中有单个结点发生电位扰动时,电路不会发生翻转,同时还避免了基于锁存复制和反馈结构的抗SEE单元的缺点。

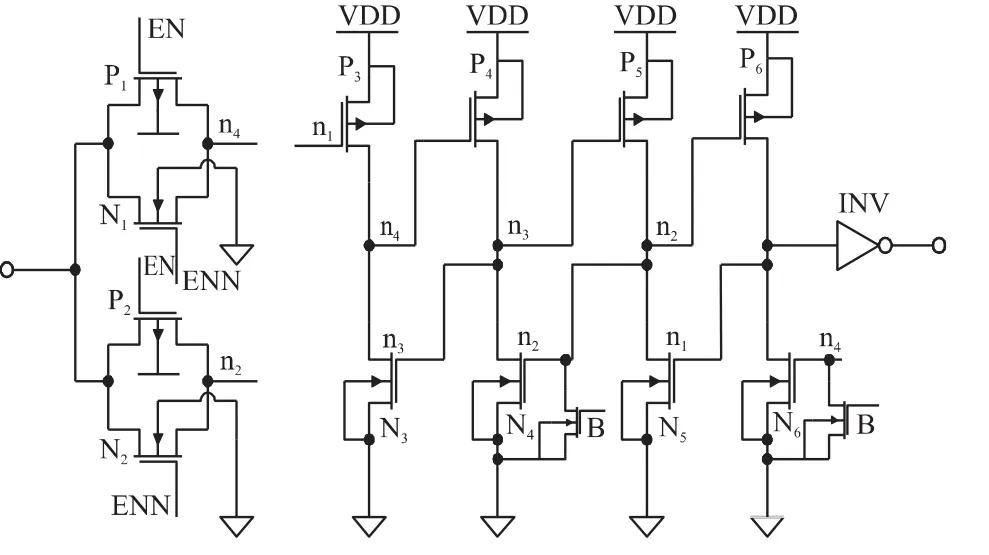

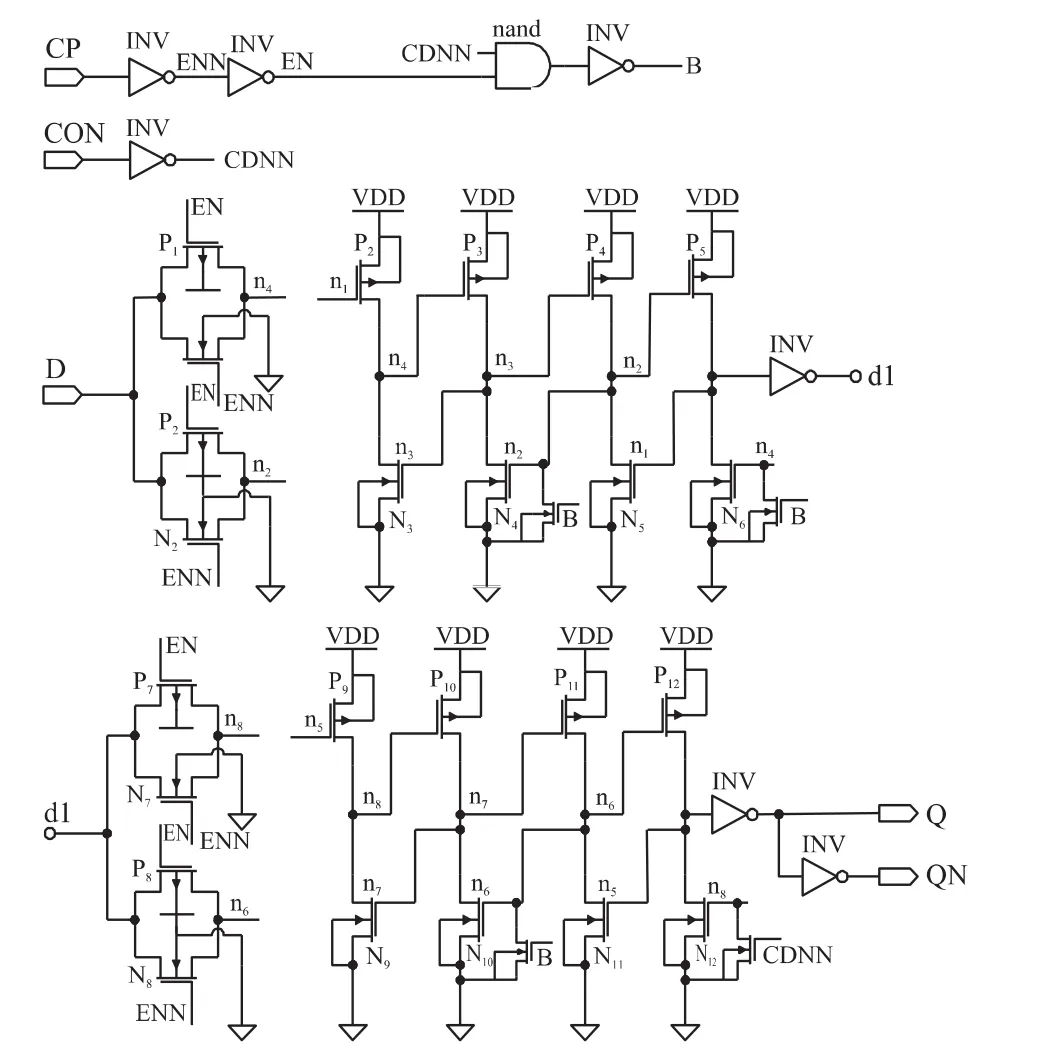

DICE单元结构组成的触发器如图1所示,P型晶体管 P3,P4,P5,P6和 N 型晶体管 N3,N4,N5,N6反向构成反馈环,形成4个互锁的反相器级联,该结构单元中有4个背靠背连接的带有反相器的存储结点:n1、n2、n3、n4用来储存两对互补的数据,其中n2和n4,n3和n1是成对的结点。与传统互锁电路不同的是该电路中每一级的P管、N管栅极分别由前一级和后一级的输出触发,这样一来每个存储结点的状态都由与其相邻的存储结点控制,并且相邻的储存结点间相互独立。当电路中只有一个存储结点的电压发生改变时,受其他结点反馈的影响,DICE内存储的状态不会发生改变。在对DICE结构进行写入时,会要求成对的2个结点的电压同时发生改变,当对4个存储结点同时进行写入时,写入的时间会缩短[15]。

此外,在图1所示的触发器电路中采用了附加晶体管冗余锁存结构,当锁存器不工作时,会强制N管的栅极接地,提高触发器电路的抗SEE的能力,减轻了SEU效应的影响[16]。

图1 DICE核心部分结构图

3 实验方案

3.1 实验装置

本次实验是利用中国科学院串列加速器核物理国家实验室的串列加速器实验靶站对测试芯片进行单粒子实验。实验时,经过加速器加速的离子会通过束运线进入辐照终端的真空靶室内,穿过注量探测器后,均匀地照射在被测器件上,被测器件的电路板放置在一个可以自由上、下移动和旋转的圆盘上,被辐照时,芯片会处于动态偏置的状态。

3.2 实验测试系统

电路单粒子翻转效应的检测系统包括硬件系统和软件系统2个部分。

3.2.1 硬件测试系统

硬件测试系统主要包括:1号计算机NI控制机、2号计算机和实验测试板这3个部分,硬件测试系统的工作原理如图2所示。

图2 硬件测试系统

(1)1号计算机

NI控制机的功能有3个:

①作为实验板的上位控制机:单粒子效应实验的上位机程序会在NI控制机平台上运行,通过串口与实验板进行通讯。

②作为单粒子翻转检测平台:负责收集实验测试板发来的单粒子翻转的情况,并记录翻转的次数和翻转阈值。

③作为单粒子锁定检测及电流控制平台:负责显示实验测试板的电流值,并控制测试板的上电和掉电的情况。

(2)2号计算机

单粒子效应的实验环境恶劣,为了保证实验在可控和安全的条件下完成,另需一台电脑做远程监控,该电脑通过网口连接到NI控制机上。

(3)试验测试板

在辐照时,实验测试板共有2种方式:正常工作模式和测试模式。

3.2.2 软件测试系统

测试系统的软件测试部分是由实验测试板上控制芯片内的下位机控制程序和上位机程序这2个部分。

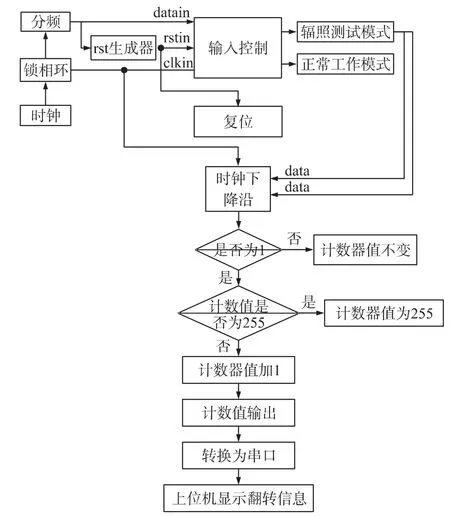

(1)下位机控制程序

控制程序的功能是控制被测芯片与标准芯片的输出复位、信号加载、输出结果传送、并将两者的输出结果进行比较等,其工作流程如图3所示。下位机程序在测试芯片上进行上电复位、时钟信号与数据信号的加载,读出输出信号,通过与标准芯片的对比,将检测结果通过串口发送给上位机。

图3 下位机翻转检测流程图

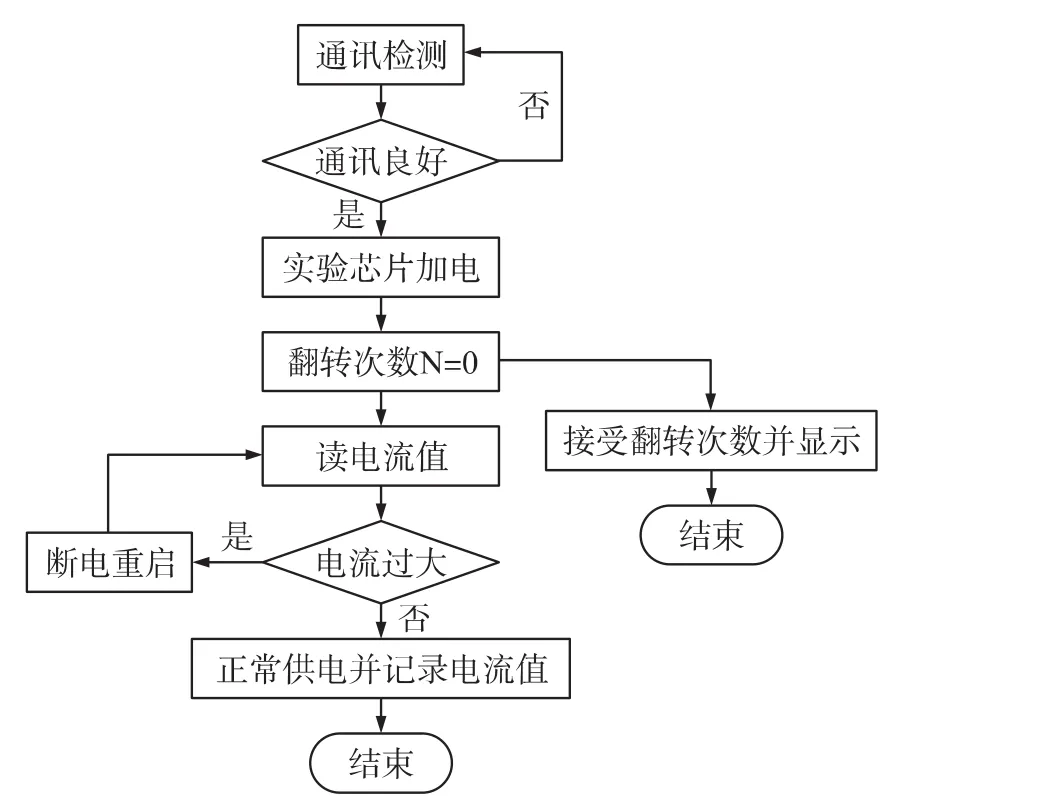

(2)上位机控制程序

上位机程序在NI测试系统中可通过串口对单粒子效应板进行数据读取,通过NI的供电板卡对辐照实验板供电,并采集电源电流大小。如果电流值超过设定的电流阈值,由系统控制被测芯片的电源通断,同时实时显示电流值及翻转次数,其工作流程如图4所示。

3.2.3 测试系统的SEU检测原理

将被辐照的芯片上每一条DFF链的输出与标准芯片的输出进行比较,翻转一次就累计计数一次,出现翻转就记为出错,出错数通过串口发送到上位机显示。

实验时,束流时间为2 h~10 h,针对SEU指标,采用3种离子氯(Cl)、锗(Ge)、碘(I)分别入射实验电路,累计注量达到107n/cm2,记录单粒子翻转效应是否发生和发生的次数。

图4 上位机如软件操作流程图

4 实验内容

4.1 实验内容

在3.3 V和1.8 V两种电压的情况下对DICE加固结构触发器链进行辐照试验,来测试其抗SEE的能力。

图5 DICE单元电路原理图

DICE电路结构如图5所示,每条链的区别是内部关键结点n2和n4在版图上的间距不同,图中的n2-n4,n3-n1,n8-n6,n7-n5都是成对的结点。在设计电路版图时,会将上面这4对结点的间距分开,避免造成结点的同时翻转,因为在DICE结构中,如果相邻的两个结点同时发生翻转,那么输出也会翻转。

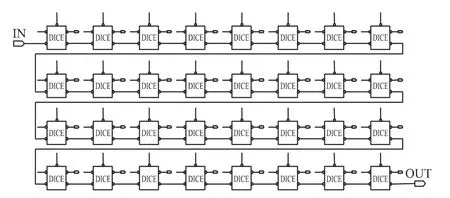

实验中会对整个触发器链进行辐照,我们将对不同工作频率、不同结点驱动能力、不同电源电压的触发器进行讨论,DICE单元结构如图6所示,DFF链由32级的触发器级联形成,DFF触发器链的电路图如图7所示。

图6 DICE电路框图

图7 DICE触发器链

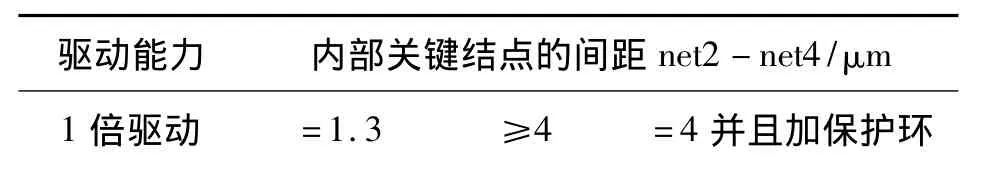

我们还会对不同版图结构的触发器进行讨论,此处的不同版图结构主要是指DICE触发器关键结点之间不同的间距,通过不同的间距可以比较相邻结点的干扰以及电荷分享机理对DICE触发器的影响,不同间距的触发器版图如图8所示。

图8 DICE触发器版图结构

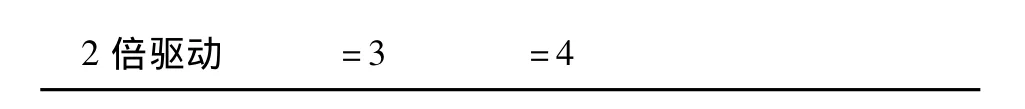

间距分类情况如表1所示。

表1 版图间距分类情况

2倍驱动=3 =4

5 实验结果与讨论

5.1 实验结果

5.1.1 不同的频率

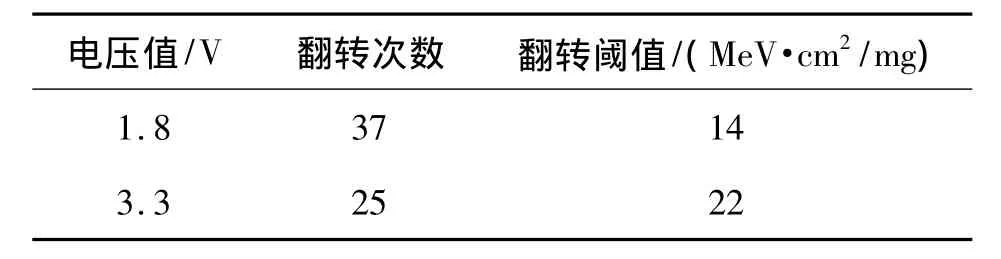

其他条件相同的情况下,在频率分别为25 MHz和50 MHz时进行单粒子实验,得到的SEU情况如表2、表3所示。

表2 频率为25 MHz时的翻转情况

表3 频率为50 MHz时的翻转情况

根据表2和表3的实验结果,我们可以看出:相同电压条件下,随着频率的增加,电路的翻转次数增加,翻转阈值会随之降低。此现象可能是由于单粒子瞬态扰动引起的,触发器在工作时,读入了受扰动的数据,导致输出数据出错。

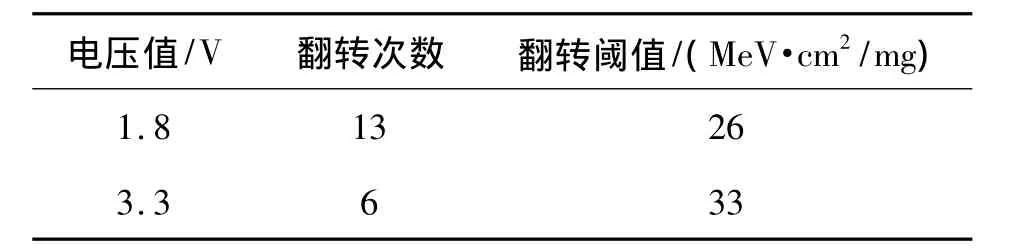

5.1.2 不同的驱动能力

我们将触发器内部采用一倍驱动和两倍驱动能力的电路进行比较,此时电路工作在25MHz,翻转情况如表4、表5所示。

表4 一倍驱动时的翻转情况

表5 两倍驱动时的翻转情况

根据表4和表5的实验结果,我们可以看出:相同电压条件下,随着结点驱动能力的增加,电路的翻转数减小,翻转阈值也会有所提高,此现象是由于结点驱动电流能抵消一部分单粒子扰动对电路的影响,驱动能力越强,抵抗单粒子效应的能力就越强。但盲目的增加结点驱动能力会给电路带来版图和功耗的问题。因此,在提升电路抗辐照能力的同时,还需要折中考虑电路其他方面的性能。

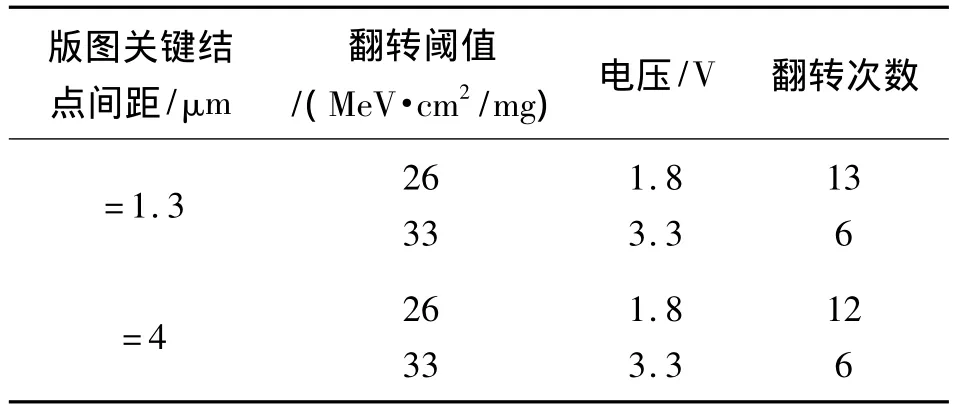

5.1.3 不同的版图结构

对于不同间距的版图结构,测试电路的翻转情况如表6、表7所示。

从表6可以看出,当关键结点之间的距离减小时,会因为相邻结点的扰动以及电荷分享机制的存在,导致触发器抗单粒子效应的能力降低。但增加了关键结点之间的距离后,会提升抗单粒子效应的能力,当间距足够大之后,利用保护环提高单粒子效应能力也不是很明显。所以,增加关键结点的间距对提升触发器抗单粒子效应是有益的。

表7 两倍驱动能力时的翻转情况

两倍驱动能力的电路本身就有较好的抗单粒子效应的能力,此时再利用增加关键结点的间距对提升抗单粒子效应的能力已经不明显。

5.1.4 不同的电压

一倍驱动能力的触发器,工作在25 MHz的条件下,1.8 V和3.3 V两种工作电压的触发器翻转阈值数据如表8所示。

表8 电压不同时的翻转情况

在实验中,随着电源电压的降低,出现错误的翻转阈值也随之降低,错误数增加。这是因为随着电源电压的降低,关键结点存储的电荷减少,而单粒子脉冲扰动产生的扰动电荷并没有减小,所以,扰动对电路的影响随之增大。

5.2 实验结果分析

针对DICE结构的触发器,在不同工作频率、不同驱动能力、不同版图结构以及不同电压的条件下进行辐照实验,观测到以下几种现象:

①随着工作频率的增加,DICE结构触发器抗单粒子效应的能力随之降低。

②随着结点驱动能力的增强,DICE结构触发器抗单粒子效应的能力随之增加。

③随着工作电压的降低,DICE结构触发器抗单粒子效应的能力随之减小。

④通过改变关键结点之间的间距,可以改善DICE结构触发器的抗单粒子效应的能力。但大于一定距离后,抗辐射能力则不再变化。

产生现象①的原因是:随着工作频率的增加,SEE对DICE触发器的扰动不仅只有SEU,还增加了单粒子瞬态扰动效应,错误的数据会从输入端存入触发器中。随着频率的不断增加,单粒子瞬态扰动效应对电路的影响也会越来越严重,最终会超出单粒子翻转效应,成为单粒子效应对电路产生影响的主导因素。

产生现象②的原因是:通过增加结点的驱动能力,可以抵消一部分单粒子效应对电路的影响,当结点受到扰动时,大的驱动能力会迅速补偿关键结点受到的扰动,降低了结点翻转的概率,但盲目的增加结点驱动能力会给电路带来版图和功耗的问题。所以,在提升电路抗辐照能力的同时,需要折中考虑电路其他方面的性能。

产生现象③的原因是:随着电源电压的降低、工艺的改进,关键结点的电容也随之降低,结点存储的电荷减少,但单粒子脉冲扰动产生的扰动电荷并没有减少。所以,单粒子效应对电路的影响会随着工艺关键尺寸和电源电压的减小而增加。

产生现象④的原因是:当某结点发生单粒子效应,其电离的电子-空穴对有一定概率会被相邻结点收集,对相邻结点的状态产生扰动,并且如果粒子大角度入射,会导致电荷分享及单粒子多结点扰动机制的发生,从而导致触发器抗单粒子效应的能力降低。但通过增加关键结点之间的距离或加入保护环则可以降低电荷被相邻结点收集的概率,降低电荷分享及单粒子多结点扰动机制的发生,从而提高抗单粒子效应的能力。

6 结论

基于0.18μm工艺平台,对DICE触发器加固结构进行辐照试验,验证SEU对体硅CMOS工艺器件及电路的影响。通过对实验数据的分析与总结,可以得出:在实际工作中合理考虑各种参数的大小,可有效地提高DICE结构抗SEE的能力,满足航空航天应用的需求。

[1]赵洪辰,海潮和,韩郑生,等.一种抗总剂量辐照的NMOSFETs[J].电子器件,2004,27(4):578-580.

[2]李飞,安海华.0.18 μm NMOS的重离子单粒子瞬态脉冲的仿真模拟[J].电子器件,2011,34(5):558-561.

[3]Maru A,Shindou H,Ebihara T,et al.DICE-Based Flip-Flop with SET Pulse Discriminator on a 90 nm Bulk CMOS Process[J].IEEE Trans on Nucl Sci,2010,57(6):3602-3608.

[4]张英武,袁国顺.一种抗单粒子全加固D触发器的设计[J].固体电子学研究与进展,2009,29(3):404-406.

[5]Baze M P,Buchner S P.Attenuation of Single Event Induced Pluses in CMOS Combinational Logic[J].IEEE Trans on Nucl Sci,1997,44(6):2217-2223.

[6]Ya V,Stenin I,Cherkasov G,et al.Memory-Cell Layout as a Factor in the Single-Event-Upset Susceptibility of Submicron DICE CMOS SRAM[J].Russian Microelectronics,2011,40(3):170-175.

[7]Tsai C H,Wu M H,Chang C F.Quasi-Planar Bulk CMOS Technology for Improved SRAM Scalability[J].Solid-State Electronics,2011,65(184):3551-3561.

[8]沈鸣杰,戴忠东,俞军.一种新型的抗单粒子翻转的D触发器[J].复旦学报(自然科学版),2006,4(4):475-479.

[9]Schwank J R,Dodd.Total Ionizing Dose and Single Event Effects Hardness Assurance Qualification Issues for Microelectronics[J].IEEE Trans on Nucl Sci,2008,55(4):- .

[10]Bhuva B L,Black J D,Massengill L W.RHBD Techniques for Mitigating Effects of Single-Event Hits Using Guard Gates[J].IEEE Trans on Nucl Sci,2005,52(6):2531-2535.

[11]Favrat P.High-Efficiency CMOS Voltage Doubler[J].IEEE J of Solid-State Circuits,1998,33(3):410-416.

[12]沈鸣杰.CMOS工艺集成电路抗辐射加固设计研究[D].上海:复旦大学,2006.

[13]赵金薇,沈鸣杰,程君侠.改进型抗单粒子效应D触发器[J].上海:半导体技术,2007,32(1):26-28.

[14]李鹏,孙永节,陈建军,等.基于Muller_C单元和DICE单元的抗辐照D触发器设计[J].计算机工程与科学,2012,34(3):35-40.

[15]刘真.标准单元抗单粒子瞬态效应版图加固技术与验证方法研究[D].国防科学技术大学,2011.

[16]章凌宇,贾宇明,李磊,等.基于DICE结构的抗辐射SRAM设计[J].微电子学,2011,41(1):107-110.

[17]郭天雷,韩郑生,海潮和,等.PDSOI静态随机存储器的总剂量辐照加固[J].电子器件,2007,30(3):794-798.