ADS-B系统信号纠检错算法及FPGA 实现

高汉昆,高 鹏

(1.山西煤炭职业技术学院 机电工程系,山西 太原 030031;2.山西离柳焦煤集团有限公司,山西 吕梁 033000)

1 ADS-B系统组成原理

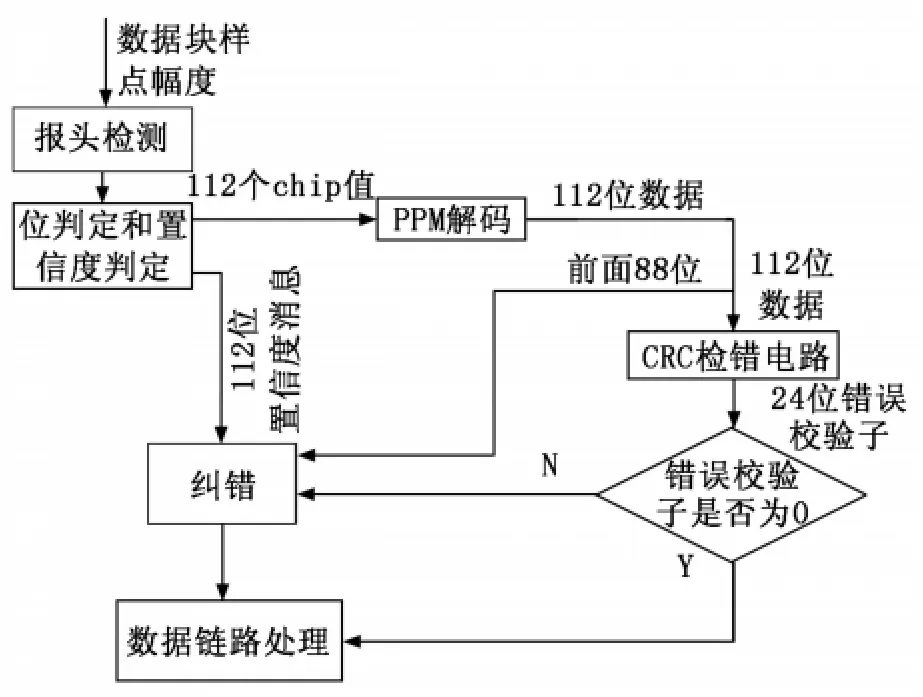

标准ADS-B 机载设备使用二次雷达频率1 090 MHz进行广播,地面站进行接收,广播的数据中包含了飞机的位置等数据。ADS-B系统算法原理框图如图1所示[1]。本文所讨论的纠检错算法主要工作在ADS-B 解码器和数据提取单元,地面站接收到ADS-B广播消息之后,需经过数据处理解码得到相应的参数信息,为了保证数据传输接收的准确性和可靠性,需进行纠检错处理。

图1 ADS-B系统算法原理框图

2 信号纠错检错算法原理

2.1 循环冗余校验(CRC)算法

CRC校验的基本原理是:根据线性编码原理,信号产生端把要传输的m 位二进制码按某种规则产生n位以后要在接收端用到的监督码,并把这n 位信息码附在m 位原码之后,产生一个新的二进制码序列。

在信号接收端,根据原传送码和接收到的CRC码之间的规则进行校验,以确认在传输过程中码位是否发生错误。发送接收双方约定好一个多项式G(x),给定消息为M(x),经过CRC除法电路后得到一串校验码。假设发送端的原始数据经过除法电路后得到的比特序列R(x)为:

发送方发送码字S(x)为:

其中:n、k为码字和消息对应的二进制序列的比特数。则接收端经相同CRC 除法电路得到的比特序列R′(x)[2]为:

判断R′(x)是否为0,若为0,说明信息未发生错误;反之,发生错误。

在本文中,针对ADS-B 下行通信数据链的特点,采用了一种改进的生成多项式,即CRC-24循环冗余校验码:

其中:CRC-24中的24表示表达式中最高次幂的数字。

2.2 CRC校验除法电路设计

本文采用长除法对输入串行码流设计CRC 校验电路,在ADS-B 接收机系统中采用的是CRC 校验除法电路。数据从电路右端串行输入(按时间顺序),异或为Reg3,即上次模2的最高位,当最高位为0时相当于只左移一位;为1时,模2后左移。当数据串行输入完成后,最终四个寄存器中的值即为余数。本文针对ADS-B系统采用多项式CRC-24设计其相对应的校验除法电路,如图2所示。

图2 CRC-24校验除法电路

2.3 置信度判定

在S模式ADS-B接收系统中,下行数据链信号是经过脉冲位置调制的。即对于任意比特位,脉冲能量出现在前一个(chip1)表示1,出现在后一个(chip0)表示0,因此我们可以通过比较每个比特中前后两个chip的能量分布来判定比特及其置信度[3,4]。有多种方法可以实现这种判定,这里采用基线多样点算法,采样点分布如图3所示。从图3可以看出每个信号都分为高低电平两部分,占空比为50%,每个电平各采样5个点,系统时钟用的是10 MHz,每个bit占用1μs,由此也可以推断出一个bit位采样10个点。

图3 ADS-B消息多点采样示意图

3 信号纠检错的FPGA实现

3.1 信号纠错检错处理流程图设计

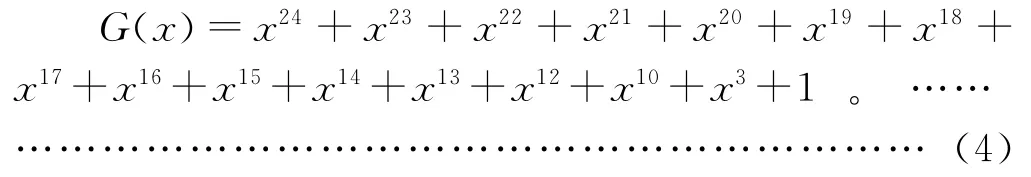

图4为纠错检错算法在FPGA 中实现的流程图。

(1)在接收端,对接收到的ADS-B 消息经过CRC校验电路,得到相应数据的错误校验子。如果该错误校验子结果为0,则表示应答数据中没有错误位。

(2)由步骤(1)得到的组合校验子与经过纠检错电路得到的错误校验子相比对,如果相等,则将对应的低置信度比特位取反(1变为0,0变为1)。

(3)到此,完成纠检错功能,输出正确消息数据。

3.2 FPGA 中实现及仿真结果分析

本文选用Xilinx公司开发的Spartan-6系列中的XC6SLX150,在ISE 11.3集成软件平台上进行编译、仿真和综合[5]。

CRC检错模块仿真波形图如图5 所示。图5 中只保留了关键信号,接收端接收到的ADS-B 信号数据为8C4E6132A4EB0C05CED38BDC2A6D,以串行比特流方式输入,当信号输入完成后,在CRC 寄存器signal_crc_reg中保留的数据即为输入信号的CRC检验码,纠错模块仿真波形图如图6所示(图5椭圆所圈数字C721A6)。

图4 信号纠错检错流程图

图5 检错模块仿真波形图

图6 纠错模块仿真波形图

蛮力纠错模块仿真波形图如图7 所示(由于在testbanch中只产生了一帧ADS-B消息数据,所以图7中无效区域是由于相应信号没有数据)。根据检错模块中输出信号的CRC校验码,通过蛮力纠错算法找出低置信度的组合以及错误的比特位,然后对数据对应的错误比特位取反并输出。测试数据中置信度为低的位都发生错误,因此图7中检测出来的w1~w5都有对应的值,纠错的结果是将其接收端接收到的对应数据位正确取反并输出。仿真结果证明了算法的正确性。

图7 蛮力纠错模块仿真波形图

4 结束语

仿真结果说明此纠检错算法能正确地检测出在传输过程中出错的比特位,并纠正其错误,然后将正确的数据输出。本文所提出的基于置信度分析的蛮力纠错技术大大提高了循环冗余码(CRC)纠错能力,提高了数据传输的准确性和可靠性,保证信息传输的完整性。

[1] Samir Palnitkar.A Guide to Digital Design and Synthesis[M].夏宇闻,译.第2版.北京:电子工业出版社,2004.

[2] 陈士毅,李玉柏.基于置信度判定的循环冗余校验纠错技术[J].电讯技术,2007(1):175-178.

[3] 刘晓斌.基于模式S 的ADS-B 接收机系统算法研究[D].成都:电子科技大学,2011:30.

[4] 周建红.ADS-B系统应答的一种纠错算法设计与实现[J].火控雷达技术,2011(3):91-95.

[5] 吴厚航.深入浅出玩转FPGA[M].北京:北京航空航天大学出版社,2010.