基于VHDL的数字锁相环设计及Modelsim 仿真

赵 玮,齐向东

(太原科技大学 电子信息工程学院,山西 太原 030024)

0 引言

在电力系统数据通信方面,同步性是系统稳定的重要因素,直接决定通信任务的成败,锁相环的出现有效地解决了这一问题。锁相环[1]对接收到的信号进行处理,提取出时钟的相位信息,并根据这个相位信息输出一个与之相干的时钟信号,达到对信号频率的跟踪,保证了系统通信的稳定。

随着数字电子技术的发展,性能更加稳定可靠的数字锁相环DPLL逐渐成为锁相环技术的发展方向。数字锁相环具有数字电路可靠性高、集成度高、可编程控制等优点,有效地避免了模拟锁相环的零点漂移、器件饱和以及抗干扰能力差等缺点,此外,数字锁相环在软件控制方面的优势明显,可以利用软件程序针对不同场合的数字锁相环进行优化设计,大大降低了硬件成本。

本文对数字锁相环的原理进行分析,提出了一种数字锁相环路的简单有效方案,采用VHDL[2]设计语言,运用Modelsim 仿真软件进行设计,并在CPLD 上实现数字锁相环的实际应用。

1 数字锁相环工作原理

数字锁相环工作原理如图1所示,它主要由鉴相器、变模双向计数器、脉冲加减计数器和分频器构成。输入信号进入鉴相器,输出信号取自分频器。各模块之间的信号均为锁相环内部信号。

这里采用的鉴相器是一个异或门鉴相器,输入信号与输出信号的异或作为鉴相器的输出,形成相位差信号,这个信号作为变模双向计数器的控制信号,当鉴相器输出高电平“1”时,变模计数器做减计数,直到产生借位信号;反之,当鉴相器输出低电平“0”时,变模计数器做加计数,直到产生进位信号。计数器的模值可以由程序设定,用来优化锁相环路锁相时间和锁相误差的关系。当相位未锁定时,鉴相器的输出呈现出的波形是一个占空比动态变化的方波信号,环路相位锁定时,鉴相器的输出为占空比50%的方波信号。

图1 数字锁相环工作原理示意图

进位和借位信号作为脉冲加减计数器的输入信号控制对时钟信号的调整输出。当产生进位信号时,脉冲计数器减少一个高频时钟周期宽度的脉冲,导致输出波形后移一个时钟周期。同样,当产生借位信号时,脉冲计数器增加一个高频时钟周期宽度的脉冲,导致输出波形前移一个时钟周期。

调整后的信号最后经过分频器产生输出信号,成为新的鉴相器输入信号。这时一个调整周期结束,经过若干次的调整,最终输出信号与输入信号得到稳定的相位差,进位信号和借位信号在同一周期内产生一次,相互抵消,输出不再发生变化,达到相位锁定。

2 基于VHDL[3]语言和Modelsim 软件的模块实现

2.1 异或门鉴相器

异或门鉴相器由输入信号和输出信号的异或构成,其逻辑波形图如图2所示,VHDL程序设计如下:

图2 鉴相器逻辑波形图

2.2 变模双向计数器

变模双向计数器模值为K,K 的大小决定了锁相时间和锁相精度。K 值越大,锁相时间越长,精度越高;K 值越小,锁相时间越短,但是精度越低。调整K值的大小是对锁相环路系统优化的一项重要措施,变模双向计数器如图3所示。

图3 变模双向计数器

由图3可以看出,加计数器到设定模值时,程序控制计数器归零,并产生一个进位信号inc_a[4]。同理,减计数器溢出时产生借位信号。

2.3 脉冲加减计数器

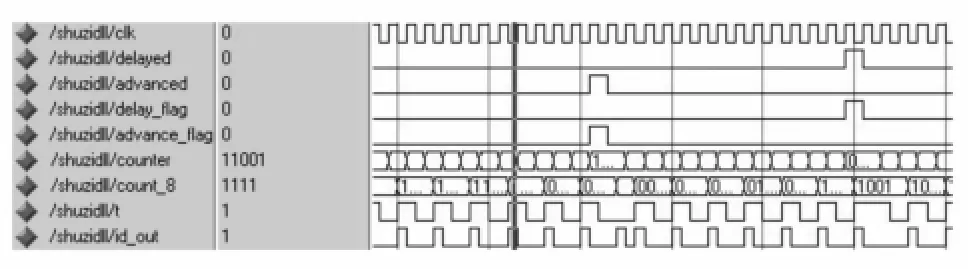

脉冲加减计数器接收到变模双向计数器的进位或者借位信号后,对输出信号进行调整,相应增加或者减少一个系统时钟周期的脉冲波形,使得输出波形向相位差减少的方向移动。脉冲加减计数器如图4所示。

图4 脉冲加减计数器

由图4 可以看出,当收到进位标志信号时,输出id_out增加一个时钟周期的脉冲。相反,收到借位标志信号时,输出减少一个时钟周期的脉冲。

脉冲加减计数器的VHDL设计程序如下:

2.4 分频器

分频器的分频值完全是根据实际频率值来决定,使得脉冲加减计数器的输出分频后匹配输入信号,另外,脉冲加减计数器增加或者减少脉冲后,波形经过分频器后恢复成标准方波形态。

3 利用Modelsim[5]进行总体仿真及分析

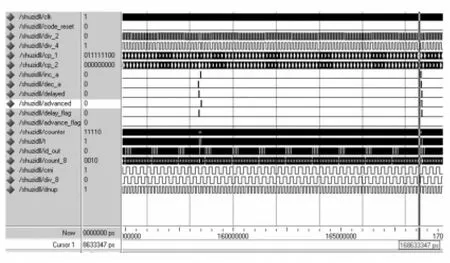

仿真时需要考虑到系统整体的时序问题,单个模块的时序在系统级别需作出调整,这里假设系统高频时钟频率为64 MHz,输入信号的频率为4 MHz。K值为25,分频值设定为8。Modelsim 整体仿真波形图如图5所示。

图5 Modelsim 整体仿真波形图(K=25)

图5中,时间坐标单位是ps。复位信号在时刻10 μs复位,开始锁相过程,经过13μs左右时间,相位误差信号变成占空比50%的稳定方波,相位被锁定。从脉冲加减计数器的内部信号(进位信号和借位信号,仿真图中间部分)来看,在锁相过程中,进位信号和借位信号逐渐相互靠拢,最后在同一个检测周期内同时出现,也就使得输出信号增加和减少的脉冲数相互抵消,输出被锁定(如图5时标所指时刻)。

前面已经分析过,K 值越小,锁相时间越短、锁相精度越低;K 值越大,锁相时间越长、锁相精度越高。K=28时。Modelsim 整体仿真波形如图6所示。

图6 Modelsim 整体仿真波形图(K=28)

与图5坐标相同情况下,从图6可以看出,K 值取28后,锁相时间明显变长,达到158μs左右。

4 结束语

电力系统存在的干扰要求通信能够较快地从扰动中恢复,所以锁相环路在满足精度的前提下,提高锁相速度是有利于系统通信稳定的。当现场干扰较强时,适当增加K 值可以有效地增加锁相判定时间,从而抑制干扰的影响,体现出了数字锁相环的优越性。

[1] 陈世伟.锁相环路原理及应用[M].北京:北京工业出版社,1990.

[2] 侯伯亭,顾新.VHDL硬件描述语言与数字逻辑电路设计[M].西安:西安电子科技大学出版社,2003.

[3] 边计年,薛宏熙.用VHDL设计电子线路[M].北京:清华大学出版社,2002.

[4] 单长虹,陈忠泽,单健.基于双边沿触发计数器的低功耗全数字锁相环的设计[J].电路与系统学报,2005,10(2):142-145.

[5] 于斌,米秀杰.Modelsim 电子系统分析及仿真[M].北京,电子工业出版社,2011.