基于P掺杂SiO2为栅介质的超低压侧栅薄膜晶体管*

朱德明 门传玲 曹 敏吴国栋

1)(上海理工大学能源与动力工程学院,上海 200093)

2)(中国科学院宁波材料技术与工程研究所,宁波 315201)

(2012年11月9日收到;2013年2月3日收到修改稿)

1 引言

最近,一种侧栅结构的新型场效应薄膜晶体管受到了广泛关注[1,2].该器件在制备过程中采用自对准技术,其源,漏,栅极都在同一平面内[2],器件结构得到极大简化,从而降低了制备难度并减小了工艺成本.这种新型的侧栅场效应薄膜晶体管结构,在未来的逻辑电路和存储电路的应用中都极具前景[3,4].然而,其制备工艺中通常需要精准的光刻技术,使得该器件的制备过程仍然比较复杂.并且侧栅结构薄膜晶体管的栅介质的等效电容基于两个电容的串联模型[5],因而电容较小,工作电压高,严重制约了其应用于实际的便携式电子产品中.

为了实现器件在低电压下工作,国内外很多课题组研究采用具有双电层大电容特性的聚合物电解质或离子液充当栅介质[6-8],来增大器件电容,提高栅极与沟道层间的电容耦合,从而降低薄膜晶体管的工作电压.近来,Crispin[9,10]等人报道了一种新型的利用聚合物电解质来作栅介质的有机双电层薄膜晶体管,栅介质单位面积电容高达10µF/cm2,工作电压可降低至1V左右.但有机薄膜晶体管存在迁移率低(<1 cm2/V·s),热稳定性差,制备过程复杂等缺点[11],因此,急需探索研究出具有高迁移率,性能稳定,制备过程简单的薄膜晶体管.

近来,本课题组采用具有双电层效应的P掺杂SiO2作为栅介质,在室温下制备了一种新型的侧栅结构薄膜晶体管.由于采用独特的侧栅结构,在射频磁控溅射过程中,仅仅利用一块镍掩模板,无需复杂的光刻步骤,就可同时沉积出ITO源、漏、栅电极和沟道,其中沟道层通过掩模板衍射自组装形成,溅射出的ITO颗粒通过衍射作用进入并沉积在镍掩模板覆盖的区域,这样在ITO源漏极形成的同时,两极之间由于ITO衍射作用形成一层薄薄的ITO沟道层.并对这种晶体管的电学性能进行了详细的研究,而且对在P掺杂SiO2栅介质层与沟道层界面处形成的超大双电层电容(8µF/cm2)机理进行了着重分析.结果表明,这种P掺杂SiO2薄膜晶体管具有极低的工作电压1 V,小的亚阈值摆幅82 mV/dec、高的迁移率18.35 cm2/V·s和大的开关电流比1.1×106等优良性能.

2 实验

如图1(a)所示,该器件以ITO导电玻璃为衬底.首先,向抽真空至3×10-3Pa的PECVD腔体中通入Ar启辉,5 min稳定后,再以SiH4(其中掺有体积分数为5%的PH3)和O2为反应气体,反应过程的压强为30 Pa,Ar、SiH4(PH3体积分数5%)、O2的流量比为60:10:60,射频电源的功率为100 W,沉积时间为60 min,得到约4µm厚的P掺杂SiO2栅介质层.然后,在已制备好的P掺杂SiO2表面固定一块镍掩模板,在0.5 Pa的Ar气环境中射频磁控溅射沉积一层约200 nm厚ITO源、漏、栅电极,溅射出的ITO颗粒会通过衍射作用进入并沉积在镍掩模板覆盖的区域,这样ITO源漏极形成的同时,两极之间一层薄薄的ITO沟道层就由于衍射同时形成了,沟道层最薄处厚度约30 nm,沉积过程如图1(b)所示.本实验采用ITO靶材(质量分数为90%的In2O3和10%的SnO2),射频电源的功率为100 W,溅射时间为15 min.整个实验过程都在室温下完成.如图2所示,柱状微孔结构的P掺杂SiO2栅介质截面形貌采用场发射扫描电镜测试(HitachiS-4800SEM).器件的电学特性由Keithley4200半导体参数分析仪在室温下无光环境中测试得到.

3 结果与讨论

在本文提到的侧栅结构中,如图1(a)所示,侧栅结构薄膜晶体管的栅介质的等效电容基于两个电容串联的模型得到,每个电容都是一个单独的双电层电容,C1和C2能很好的通过ITO层串联起来[4].

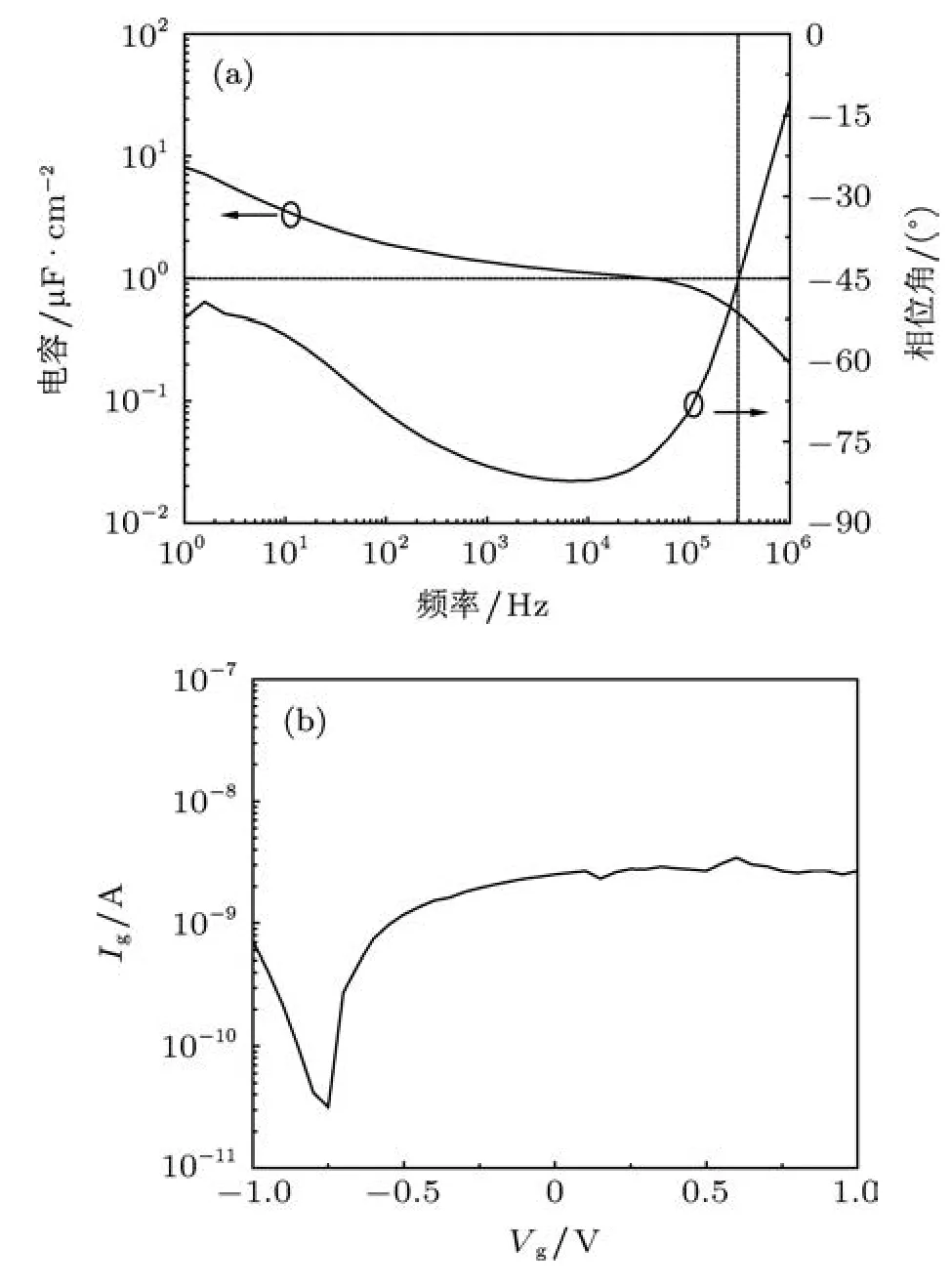

从图3(a)可以看出,电容随频率的减小而增大,并到1 Hz时达到最大值8µF/cm2.然而,根据传统的电容理论:C= εoεr/d(εo是真空介电常数,εr是相对介电常数,d是栅介质厚度)计算得到的电容为8.6×10-4µF/cm2.很明显,理论计算结果比实验结果小了四个数量级.对此,我们提出用双电层理论来解释这种超级大电容形成的原因[12,13]:在本课题组以前的研究中,SiO2栅介质与沟道界面处也能形成双电层电容2.7µF/cm2[14],本文中形成的大电容,是由于P的掺入,栅介质中含有P3+,空气中的H2O分子能渗透到这种疏松的孔隙栅介质结构中(如图2所示),与P3+结合形成H3PO3,相对于传统的SiO2栅介质,它会产生更多的H+;并且P的掺入,会使Si-OH+-Si的键能变弱,因而质子导电性增强[15].从图2可以看出,这种P掺杂SiO2栅介质具有疏松、柱状的排列结构,其间存在很多孔隙,正是由于具有这种疏松的孔隙结构,当给栅极外加正向偏压时,H+通过柱状阵列的间隙向栅介质和沟道层表面移动,在沟道层内产生大量的相反电荷,形成双电层,从而获得大电容.

图1 (a)器件结构示意图;(b)ITO沉积过程示意图

图2 P掺杂SiO2扫描电镜图

图3 (a)电容和相位角随频率变化的曲线;(b)P掺杂SiO2栅介质漏电流曲线

图3(b)为P掺杂SiO2栅介质漏电流曲线.1 V偏压下漏电流约为3 nA,远远小于聚合物电解质的漏电流(∼0.1µA)[9-11].所得的漏电流比沟道电流小5个数量级,这就表明P掺杂SiO2栅介质没有明显的电化学现象,离子电流也很小,具有较好的绝缘特性,能够保证器件的正常工作而不受栅漏电流的影响[13,16].

图4(a)是该器件的输出特性曲线(Ids-Vds).Vds由0 V扫描至1 V,同时,Vgs由0 V扫描至1 V,每次增加0.2 V.由图4(a)可知,较高的Vds下器件显示出了良好的电流饱和特性,而在较低Vds下Ids也具有很好的线性特性,器件具有良好的欧姆接触,在偏压Vds=1 V和Vgs=1 V下具有较高的饱和电流(∼200µA).由于P掺杂SiO2栅介质和沟道界面处的双电层效应,形成了较大电容,所以本器件显示出了超低的工作电压1 V.

图4 (a)该器件的Ids-Vds输出特性曲线;(b)该器件的Ids-Vgs转移特性曲线,以及Vds=1 V下对应的曲线

上式中 L为沟道长度 80µm,W 为沟道宽度1000µm,Ci为 P掺杂 SiO2栅介质单位面积电容.通过计算可得,饱和区场效应迁移率µFE约为 18.35 cm2/V·s.

图5 该器件的脉冲响应曲线

图5为该器件的脉冲响应图.在Vds外加电压1 V,Vg外加-1 V和1 V的脉冲测试信号下,没有明显的电流损失,并且维持稳定的开关电流比,这表明ITO沟道层和这种颗粒膜P掺杂SiO2栅介质之间没有明显的电化学掺杂发生[14],器件显示出了较好的稳定性.

4 结论

采用P掺杂SiO2作为栅介质,应用于侧栅结构的薄膜晶体管中,在栅极外加正压情况下,具有更多的H+等可移动离子移动到栅介质绝缘层的上表面与沟道感应电子形成极强双电层效应,获得大电容(8µF/cm2).使该器件具有超低的工作电压1 V,小的亚阈值摆幅82 mV/dec、高的迁移率18.35 cm2/V·s和大的开关电流比1.1×106.并且采用独特的侧栅结构,在射频磁控溅射过程中,利用一步掩膜法,就可同时沉积出ITO源、漏、栅电极和沟道,因而极大的简化了制备流程,降低了工艺成本.因此,这种P掺杂SiO2侧柵结构薄膜晶体管在未来的低功耗电子器件及新型传感器领域的应用中都极具前景.

[1]Draghici M,Diaconescu D,Melnikov A,Wieck A D 2010 Phys.Status SolidiA 207 229

[2]Chung T H,Chen S H,LiaoW H,Lin S Y 2010 IEEE Electron Device Lett.31 1227

[3]Colinge J P,Lee C W,Afzalian A,Akhavan N D,Yan R,Ferain I,RazaviP,O’NeillB,Blake A,White M,Kelleher A M,McCarthy B,Murphy R 2010 Nat.Nanotechnol.5 225

[4]ZhaoK S,Xuan R J,Han X,Zhang G M 2012 Acta Phys.Sin.61 197201(in Chinese)[赵孔胜,轩瑞杰,韩笑,张耕铭2012物理学报61 197201]

[5]Jiang J,Sun J,Dou W,Zhou B,Wan Q 2011 Appl.Phys.Lett.98 113507

[6]RavalH N,TiwariS P,Navan R R,Mhaisalkar,RaoV R 2009 IEEE Electron Device Lett.30 484

[7]Kim J B,Fuentes H C,Kippelen B 2008 Appl.Phys.Lett.93 242111

[8]Wang G M,Moses D,Heeger A J 2004 J.Appl.Phys.95 316

[9]Larsson O,Said E,Berggren M,Crispin X 2009 Adv.Funct.Mater.19 3334

[10]ChoJ H,Lee J,He Y,Kim B,Lodge P T,Frisbie C D 2008 Adv.Mater.20 686

[11]Liu Y R,Chen W,LiaoR 2010 Acta Phys.Sin.59 8088(in Chinese)[刘玉荣,陈伟,廖荣2010物理学报59 8088]

[12]Sun J,Liu H X,Jiang J,Lu A X,Wan Q 2010 J.Mater.Chem.20 8010

[13]Lu A X,Sun J,Jiang J,Wan Q 2009 Appl.Phys.Lett.95 222905

[14]Jiang J,Sun J,Zhou B,Lu A X,Wan Q 2010 IEEE Electron Device Lett.31 1263

[15]Jiang J,DaiM Z,Sun J,Zhou B,Lu A X,Wan Q 2011 Appl.Phys.Lett.109 054501

[16]Jiang J,Sun J,Lu A X,Wan Q 2011 IEEE Electron Device Lett.58 547

[17]Wee G,Larsson O,Srinviasan M,Bcrggren M,Crispin X,Mhaisalkar S 2010 Adv.Funct.Mater.20 4344