高栅压低漏压条件下FG-pLEDMOS的热载流子退化机理

万维俊 刘斯扬 孙 虎 孙伟锋

(东南大学国家专用集成电路系统工程技术研究中心,南京 210096)

p型横向延伸漏区MOS管(p-type lateral extended drain MOS transistors,pLEDMOS)具有工作电压高、导通电阻小、制造工艺简单以及易于与标准CMOS工艺兼容等优点,在等离子平板显示驱动芯片、电源管理芯片以及半桥驱动芯片等产品中被广泛地应用.其中,pLEDMOS的栅氧化层必须做得很厚,以便在器件开态下能够承受很高的栅源电压.实际工艺中,为了节约制造成本,常利用场氧化层做栅氧化层(field gate oxide,FG)[1].但由于厚栅氧的阻挡作用,在制造过程中很难利用自对准工艺实现源端的P+注入.为了防止器件沟道不开启,在生长厚栅氧以及淀积多晶硅前,在器件源端先以高能量注入硼离子形成一个p型缓冲区(pbuffer region),从而形成了FG-pLEDMOS器件中特有的结构.实际工作中,FG-pLEDMOS主要用作输出驱动电路的上管,工作在开关状态,即低栅源电压(Vgs)和高漏源电压(Vds)或高栅源电压(Vgs)和低漏源电压(Vds)条件下[2].目前,对 pLEDMOS器件的热载流子效应的研究主要集中在低Vgs和高Vds条件下[3-5],而对于高 Vgs和低 Vds应力条件下的热载流子退化至今仍然鲜有报道.文献[6]的研究结果表明,在高 Vgs和低 Vds条件下,nLEDMOS器件中的热载流子退化主要是由于在沟道区靠近源端处的热载流子注入引起的.然而,与nLEDMOS不同的是,在FG-pLEDMOS中,由于源端特有的p型缓冲区结构,高Vgs和低Vds应力条件下的热载流子退化存在新的机理,影响器件性能的退化.

本文研究了高Vgs和低Vds应力下FG-pLEDMOS器件的热载流子退化机理,并揭示了不同p型缓冲区长度影响FG-pLEDMOS器件退化的机制.

1 器件结构

图1为基于0.5 μm体硅工艺制造研究的FG-pLEDMOS器件的剖面结构图,主要结构与工艺参数如下:漂移区长 5 μm,沟道区长 4 μm,p 型缓冲区与栅极的交叠区长A=0.3 μm,栅距源端P+的距离B=0.6 μm,栅氧化层的厚度与场氧化层的厚度相同,均为 400nm.该器件的开启电压为-10.5 V,关态击穿电压为100 V.为了研究器件的退化机理以及不同p型缓冲区长度对器件热载流子退化的影响,对图1中的结构参数A设置了多个不同值,并流片制造.本文所研究的器件均为4端口,以便进行电荷泵(charge pumping,CP)测试.

图1 FG-pLEDMOS的剖面结构图

2 测试方法

2.1 应力退化测试

为了研究高Vgs和低Vds应力条件下的退化,选用的应力条件为Vgs=-100 V,Vds=-10 V,整个应力过程在室温下进行,且周期性地每过一段时间监测一次器件的线性区漏电流 Idlin(在 Vgs=-15 V,Vds=-0.1 V条件下测得)和阈值电压Vt(Vgs从0 V 扫到 -15 V,Vds= -0.1 V,利用最大跨导法求得).总应力时间为5 000 s.

2.2 电荷泵测试

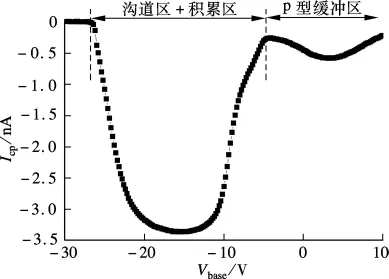

电荷泵技术作为一种目前最有效的研究热载流子造成器件退化的技术手段,能够直接测量MOS器件栅极下方的硅和二氧化硅界面的界面态数量(Nit)及分布,从而反映出器件受热载流子损伤的程度和位置.对于p型MOS器件,器件的源端与漏端短接并与衬底间接一反偏电压,通过给栅极加一脉冲电压,使栅极下方区域在“反型”与“积累”之间不断变化,在“反型”状态时,来自源端和漏端的空穴会被栅极下方硅和二氧化硅界面处的界面态俘获;当处于“积累”状态时,这些被俘获的空穴便会和来自衬底的电子复合,在衬底端产生复合电流即电荷泵电流(Icp)[7-8].Icp与对应栅下的界面态密度(Dit)成正比,因此器件在应力前后差值Icp的大小即可反映出器件界面态密度在应力过程中的增量大小[9].为了提取器件栅极下方不同区域的界面态数量,对器件栅极下方各个区域分别达到“积累”、“反型”状态所需要的栅压进行了仿真,仿真结果如图2所示,并定义达到积累状态的栅压为Vgh,达到反型状态的栅压为Vgl.

图2 栅极下方各区域的Vgh与Vgl的仿真结果

对于本文研究的FG-pLEDMOS,栅极下方区域包括沟道区、积累区、p型缓冲区,总的Icp应为沟道区、积累区、p型缓冲层区3个区域的Icp的叠加,图3为通过变化脉冲基准电压(Vbase)得到的CP曲线.利用图2中的数据,可以区分出3个区域在总的CP曲线上的主要作用区间,也可以得出器件中所关心位置的Icp,通过比较应力前后该位置Icp的差值(ΔIcp)来反映该处在应力过程中界面态的增量.

图3 FG-pLEDMOS的 CP 测试曲线(A=0.3 μm)

3 实验结果与讨论

3.1 高Vgs和低Vds下的退化机理

图4为该器件在高 Vgs和低 Vds下Idlin和 Vt随应力时间的退化曲线,其中,ΔIdlin为漏电流退化量,ΔVt为阈值电压退化量.从图中可以看出,Vt在应力过程中基本没有退化,而Idlin随着应力时间的增加不断减小,在1 000 s之后,退化逐渐趋于饱和,这与文献[10]的结论一致.

图4 Idlin与Vt随应力时间的退化曲线

阈值电压Vt基本没有退化,表明在应力过程中栅氧化层并没有俘获电荷,而Idlin不断减小,表明载流子的有效迁移率不断降低.为了揭示其中的退化机理,利用二维TCAD仿真软件对器件内部垂直于Si/SiO2界面的纵向电场和靠近Si/SiO2界面处的碰撞电离率的分布进行了仿真.图5(a)为高Vgs和低Vds下沿Si/SiO2界面纵向电场的分布,纵向电场为负,表明其方向为从体内指向表面,有利于空穴的注入,另外,纵向电场的峰值出现在沟道区;图5(b)为相同条件下沿Si/SiO2界面碰撞电离率的仿真结果,与纵向电场的结果类似,碰撞电离率主要出现在沟道区,且峰值位置与纵向电场相同.由图5可知,在高Vgs和低Vds条件下,由于严重的碰撞电离,沟道区出现了大量的电子空穴对,其中空穴在纵向电场的加速下,注入到栅氧化层,但空穴并没有被栅氧化层俘获,而是形成大量的界面态,进而造成沟道区中载流子的有效迁移率降低,导致线性区漏电流Idlin的退化.

图5 pLEDMOS中栅极下方SiO2/Si界面的仿真结果

3.2 不同p型缓冲区长度对退化的影响

图1显示出p型缓冲区主要由A,B两段组成,为了研究p型缓冲区长度的影响,这里通过保持B不变、改变A的长度得到了3种不同p型缓冲区长度的器件,其中 A 分别为0.3,0,-0.3 μm.由于Vt在应力过程中基本没有退化,因此这里只比较3个器件的Idlin随应力时间的退化,结果见图4.从图中可以看出,3个器件的退化趋势相同,p型缓冲区长度越小,Idlin的退化量则越大.

图5(a)为3个器件Si/SiO2界面的纵向电场随器件横向位置的分布情况.图中显示,3个器件纵向电场的峰值都出现在沟道区,不同之处在于峰值所对应的器件横向位置以及峰值大小的变化.峰值横向位置的变化由沟道下方的电势分布决定,而电势的分布取决于零电位(0 V)的p型缓冲区、高负电位(-100 V)的栅极以及低负电位(-10 V)的漏极.因此,p型缓冲区相对栅位置的变化必然引起电势分布的变化,从而导致纵向电场峰值位置有相应的偏移.另一方面,电势分布的变化又会引起纵向电场峰值本身大小的改变.在Si/SiO2界面处,纵向电场的大小反映了注入的难易程度,纵向电场越大,就越有利于空穴的注入.图5(b)给出了3个器件中靠近Si/SiO2界面处碰撞电离率随器件横向位置的分布情况.与纵向电场的分布类似,不同器件中碰撞电离率也出现峰值位置和大小的变化.碰撞电离率的大小反映了该处产生电子空穴对的多少,电离产生的电子空穴对越多,就会有越多的载流子经纵向电场的加速对该处界面造成损伤,形成界面态.图5(b)中仿真数据显示,p型缓冲区长度的微小变化导致了碰撞电离率高达3倍的差异.结合图5(a)和(b)可以看出,随着p型缓冲区的减小,沟道区的纵向电场变大,同时,沟道区的碰撞电离率也成倍地增大,这就使得有更多的空穴对Si/SiO2界面造成损伤,形成更多的界面态,从而导致Idlin的更大退化.

为了进一步验证3个器件在应力过程中的退化机理,进行了CP实验.在应力退化实验中,分别在选定的时间点对器件进行CP测试.选择纵向电场和碰撞电离率的峰值位置即退化最严重的位置,测得应力过程中不同器件在该位置处的ΔIcp(用ΔIcp,Emax表示)随应力时间的变化,结果如图6所示.从图中可以看出,p型缓冲层区越小,ΔIcp,Emax随应力时间的增长越快.结合前面给出的CP测试的基本原理可知,CP电流正比于界面态密度,应力过程中CP电流的变化反映了界面态密度的变化.由CP实验的结果可知,界面态数量的增加趋势与器件Idlin退化的趋势一致,从而验证了对器件退化机理的解释.

图6 最大电场位置处的ΔIcp随应力时间的变化

4 结语

研究了高Vgs和低Vds应力条件下FG-pLEDMOS器件的热载流子退化机理以及器件源端p型缓冲区长度对器件热载流子退化的影响.研究结果表明,在高Vgs和低Vds应力条件下,热载流子退化的原因是由沟道区界面态产生的,且增加p型缓冲区的长度,会使沟道区热载流子退化得到一定的改善.实际在设计p型缓冲区的长度时,还要综合考虑到对导通电阻和阈值电压等参数带来的影响.

References)

[1] Sun Weifeng,Wu Hong,Shi Longxing,et al.On-resistance degradation under different stress condition in high voltage pLEDMOS transistors and an improved method[J].Journal of Semiconductors,2008,29(2):214-218.

[2] Sun Weifeng,Wu Hong,Shi Longxing,et al.On-resistance degradations for different stress conditions in high-voltage pLEDMOS transistor with thick gate oxide[J].IEEE Electron Device Letters,2007,28(7):631-633.

[3] Sun Hu,Qian Qinsong,Sun Weifeng,et al.Comparison of the on-resistance degradation in pLEDMOS with the different geometrical parameters[C]//Proceedings of the10th International Conference on Solid-State and IntegratedCircuitsTechnology. Shanghai, China,2010:1619-1623.

[4] Enichlmair H,Park J M,Carniello S,et al.Hot carrier stress degradation modes in p-type high voltage LDMOS transistors[C]//47th IEEE Annual International Reliability Physics Symposium.Montreal,Canada,2009:426-431.

[5] Chen J F,Tian K S,Chen S Y,et al.An investigation on anomalous hot-carrier-induced on-resistance reduction in n-type LDMOS transistors[J].IEEE Transactions on Device and Materials Reliability,2009,9(3):459-463.

[6]Aresu S,de Ceuninck W,Groeseneken G,et al.Evidence for source side injection hot carrier effects on lateral DMOS transistors[J].Microelectronics Reliability,2004,44(9/10/11):1621-1624.

[7] Groeseneken G,Maes H E,Beltran Nicolas,et al.A reliable approach to charge-pumping measurements in MOS Transistors[J].IEEE Transactions on Electron Devices,1984,31(1):42-53.

[8] Heremans P,Witters J,Groeseneken G,et al.Analysis of the charge pumping technique and its application for the evaluation of MOSFET degradation[J].IEEE Transactions on Electron Devices,1989,36(7):1318-1335.

[9] Chen J F,Lee J R,Wu Kuo-Ming,et al.Off-state avalanche-breakdown-induced on-resistance degradation in lateral DMOS transistors[J].IEEE Electron Device Letters,2007,28(11):1033-1035.

[10]Moens P,Tack M,Degraeve R,et al.A novel hothole injection degradation model for lateral nDMOS transistors[C]//IEEE International Electron Devices Meeting.Washington,DC,USA,2001:877-880.