浅谈Proteus VSM在数字逻辑课程教学中的应用

◆邵平凡

(武汉科技大学计算机科学与技术学院)

浅谈Proteus VSM在数字逻辑课程教学中的应用

◆邵平凡

(武汉科技大学计算机科学与技术学院)

本文从数字逻辑课程的特点、现状及教学需求出发,介绍了引入Proteus VSM的必要性及其在实际教学过程中取得的效果,充分说明了Proteus VSM在该课程教学中的作用。

组合逻辑 时序逻辑 虚拟系统模型

一、前言

数字逻辑是数字电路逻辑设计的简称,是计算机及相关专业的一门必修的专业基础课,其主要内容是用数字电路进行数字系统逻辑设计,包括组合逻辑电路、时序逻辑电路及其混合逻辑电路的分析与设计技术。不管是什么样的电子数字计算机,无非是由具有各种逻辑功能的逻辑部件组成的,但在设计过程中一定需要进行各种单元电路和系统整体的实验和测试,以确保逻辑正确,时序无误,并且性能良好。

需要实验和测试,就需要相应的逻辑元器件来构建电路,还需要测量、测试及辅助分析用的仪器设备,当然也需要相应的电源、信号源等。如果一切都需要真材实料,毫无疑问是一般学习者无法解决的问题。因为学校的教学资源有限,即使是在校的大学生,实验室的资源也不可能满足其所有需求,对于校外的其他学习者就更加困难。因此,寻找一种接近实际的虚拟系统作为实现数字逻辑电路的分析与设计、实验和测试的工具,会对学习者有很大的帮助,只有通过理论与实践的结合,才可能加深学习印象,提高学习效果,减少设计错误,明确电路的设计性能。

Proteus VSM(Virtual System Model,虚拟系统模型)正好可以满足学习者的这些需求,它是由英国Labcenter Electronics公司开发的一款EDA软件,是目前世界上最先进、最完整的仿真平台。Proteus软件具有多种元件库,其中的元器件大多均可直接用于实际电路的搭建,而且该软件提供了多种与实际仪器仪表用法相似的虚拟仪器设备,还有各种信号源,几乎可以完成各类数字逻辑电路的设计、测试和辅助分析工作。由于这些虚拟元器件、仪器设备和信号源可以随意取用,既不需要花钱购买,又接近实际实物的效果,而且不需要维护,不会因为学习者的误操作或使用不当而造成元器件和仪器设备的损坏,更不会影响到人身安全,而且仿真效果非常逼真。因此,不仅使任课老师可在课堂上以形象生动的仿真演示提高学生的学习兴趣,而且可引导学生将相应实验推广至课外的任何地点。学习者可根据自己的需要,自行设计实验项目,从系统提供的元件库中找到相应的虚拟元件,形成自己的实验电路,从系统提供的虚拟仪器中找出自己需要的仪器设备,从系统提供的信号源中随意取得所需使用的各种信号源,从而实现对所需电路进行设计、测试和分析,有效地解决学习过程中的各种疑难问题,提高自己的实际设计能力。

二、组合逻辑电路的分析与设计

组合逻辑电路是由与门、或门和非门等门电路组合形成的逻辑电路,对于一些常用的组合逻辑电路,许多IC芯片制造商已经提供了相应的集成电路芯片,即使是一些复杂的组合逻辑关系也可以通过常用IC芯片和一些辅助门电路组合而成。

1.组合逻辑电路的分析

所谓组合逻辑电路的分析,就是根据已知逻辑电路图,找出组合逻辑电路的输入与输出关系,确定在什么样的输入取值下对应的输出为1。当然,输入通常是多个逻辑量,而输出可以是1个或多个。

在对组合逻辑电路进行分析时,Proteus VSM提供了很好的仿真手段,如图1(a)所示的组合电路,如果需要分析其输入与输出的逻辑关系,可以设计一些辅助电路如图1(b),通过三个开关的按下与弹起为电路的三个输入端A、B、C提供不同的输入组合,观察不同输入所对应的两个输出端的逻辑电平,可列出真值表如表1所示。图中所示的情况是:输入A、B、C的值是1、0、1,而输出 F2 的值是1,F1 的值是0。

图1 组合电路及其分析方法

表1 图1电路真值表

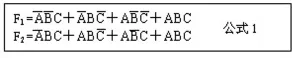

根据真值表可以写出逻辑表达式:

从公式1可见,F1是在奇数个输入为1时才输出为1,而F2是两个或三个输入为1时才输出1,这正是一位全加器的逻辑表达式。其中,F1为本位和,F2为向高位的进位。对以上逻辑表达式进行化简可得:

这样就与电路完全一致了。

2.组合逻辑电路的设计

组合逻辑电路的设计是组合逻辑电路分析的逆过程,即根据输入与输出的逻辑关系要求,设计出满足符合要求的组合逻辑电路。

常用的组合逻辑电路包括译码器、编码器、多路选择器、比较器、加法器等,这些电路通常都有多种型号的IC芯片可供选择。在实际应用中,组合逻辑电路的设计通常都采用常用的IC芯片来构建,必要时再配合一些辅助门电路,这样的设计简单可靠,设计方法可按常规方式进行,但对于设计出的组合逻辑电路是否正确,就必须通过实验测试才能进一步确认,有了Proteus VSM,只需按设计电路图将所设计的电路在Proteus的ISIS(Intelligent Schematic Input System,智能原理图输入系统)中绘制出来,再配合一些辅助电路进行仿真,就可实现正确性的验证了。

比如,设计一个8位二进制加法器,可以用两片74LS283来实现,如图2(a)所示,具体电路的仿真结果如图2(b)所示,在图2(b)中两个8位二进数分别为:A=00001111B=0FH,B=10011111B=9FH,相加的结果通过两个数码管显示为AEH。用鼠标点击构成数据输入端的每一个LAGICSTATE图标,就可以像改变图1(b)的输入开关状态一样,使每一位的值在0和1之间切换,从而实现对不同的两组8位二进制数据进行相加运算,并将相应结果通过LED数码管显示出来。其实,即使不用LED数码管,通过仿真电平的颜色显示也可判断其值(红颜色为1,蓝颜色为0)。比如,从图2(b)可见,其输出引脚8位的值,其从高位到低位的二进制数为1010 1110,所以显示的十六进制值为AEH。从U2的C4脚输出电平可见(用LOGIC PROB)显示,没有向高位进位。

图2 8位加法器的设计与仿真

三、时序逻辑的电路分析与设计

时序逻辑电路是由触发器和门电路组成的具有记忆功能的逻辑电路,对时序逻辑电路的分析与设计采用Proteus VSM作为辅助手段,更能起到事半功倍的效果。

下面以设计一个六十进制计数器为例,简要介绍其分析与设计过程。首先已知常用IC中有BCD计数器功能的IC芯片,如74HC160是同步预置数,异步清0的十进制加法计数器,对于六十进制计数,只需用两片74HC160再配以少量辅助门电路即可完成。但在设计过程中,方式方法可以有多种,比如两个BCD计数之间的计数过程是同步还是异步、如何处理进位等。

图3 六十进制计数器设计之一

以图3(a)为例,其计数过程就是异步方式,其十位的计数脉冲单纯由个位的进位提供。这种方式在仿真时,有可能出现错误。其原因有二:一是由于个位的进位RCO经反相后给十位作为计数脉冲。刚开始工作时,由于个位的RCO为0,所以经反相后为1,这就使得十位得到一个不应有的进位而产生了一个误计数,其仿真如图3(b)所示,还没有按过按钮时,其计数显示结果居然是10,显然这就是由于十位的误计数造成的;二是由于个位的进位RCO=D3&D0&T,当计数值由0111(1000时,因电路中的竞争冒险可能存在短暂的D3=D0=1的时刻,也可能导致十位计数器误计数。因此需要对电路进行改进,将十位的计数脉冲改成同步方式,即计数脉冲同时供给个位和十位,而十位的计数使能信号由个位的RCO输出提供,十位的回零装入信号LOAD设置为个位的RCO和十位的Q2、Q0三者的与非提供。改进后的电路如图4所示,在刚开始仿真时,计数结果显示为00,每按一次按钮,计数值加1,计到59时,再按一下按钮,则计数显示回零,这样就达到了预期的设计要求。

图4 六十进制计数器设计之二

四、数字逻辑课程设计

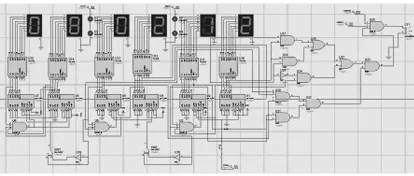

课程设计是数字逻辑课程的一次综合应用实训,是对本课程的各个知识点的溶汇贯通,在以往的课程设计中,由于实验箱的数量有限,元器件也不可能满足所有课程设计者的要求,所以学生的课程设计大多停留在理论设计上,无法进行真实的正确性验证。通过引入Proteus VSM后,可以满足所有愿意参与在该虚拟平台上进行课程设计的学生要求。在课程设计的验收过程中,十多个题目都有人参与,设计结果多种多样,但都可以保证在虚拟系统环境下的运行正确,学生的兴趣很大,设计完全可达到预定的要求。如图5所示为某个学生设计的数字时钟的仿真运行效果。

图5 数字时钟设计方案之一

五、结语

数字逻辑是一门实践性很强的课程,以往由于实验器材和实验设备的不足,使学生的动手能力不能得到充分的发挥。采用了Proteus VSM后,可以很大程度弥补这一缺失,使教学过程与实践环节有效结合,既提高了学生的学习兴趣,同时也锻炼了学生的实践操作能力。这得益于Proteus软件拥有丰富的元器件库、强大的原理图绘制功能、逼真的仿真效果和品种齐全而且精确可靠的各种虚拟仪器仪表,因此大大地提高了教学效果,缓解的实验室的压力。特别是对于改善电类课程的远程教育和多媒体教育效果,更是有着不可估量的好处。

实际上,Proteus VSM不仅可以实现诸如数字逻辑这样的硬件电路的设计与仿真,而且可以软、硬件结合,因为Proteus软件还提供了对多种系列的单片机系统的支持,并且还支持第三方软件的编译和调试环境,如KeilμVision2~4。因此,在数字逻辑课程中就掌握了Proteus软件的应用,也就为诸如计算机组成原理、单片机技术、接口技术、嵌入式系统等后续课程打下了良好的基础。