控制器局域网位时序处理器的设计与实现

胡越黎, 徐晓勇

(上海大学机电工程与自动化学院,上海 200072)

控制器局域网位时序处理器的设计与实现

胡越黎, 徐晓勇

(上海大学机电工程与自动化学院,上海 200072)

在控制器局域网 (controller area network,CAN)总线通信中,位时序的处理关系到 CAN能否正确地收发数据.基于总线标称位时间的周期结构及位同步的工作原理,提出 CAN 2.0协议标称位时间的一种优化方法,即将传统的标称位时间由 4个互不交叠的段简化成 3个互不交叠的段,并在此基础上提出一种基于同步状态机的 CAN总线位时序处理器的设计方法,提供可编程的时间段来补偿传播延迟时间和相位漂移,并对设计的电路进行仿真与验证.结果表明,相对于 CAN协议规范标称位时间的 4个互不交叠的段,减少了整个位时序处理过程使用的寄存器,简化了执行位同步的步骤,能更简便地处理 CAN总线通信的位时序,实现了 CAN总线协议中对位定时和位同步的控制,更好地优化了 CAN网络的性能.

标称位时间;同步;位时序处理器;控制器局域网总线

位时序处理器 (bit timing p rocessor,BTP)用来实现对 CAN总线协议中位定时和位同步的控制,并对 CAN总线通信中每个位的传输时间进行控制,该时间称为标称位时间,又称为位周期.BTP在发送数据时按照标称位时间对每个发送数据位进行定时;在接收数据时,同步于总线上的数据,执行同步 (硬同步和重新同步)功能[3].

为了更简便地处理 CAN总线通信的位时序,本研究针对 CAN 2.0协议的标称位时间提出了一种优化方法,对标称位时间的定义及概念与同步的工作原理进行了阐述.同时,本研究提出了一种基于同步状态机的 CAN位时序处理器的设计方法,说明了同步状态机的工作过程,并对设计进行了仿真与验证.

1 位时序相关概念

1.1 标称位时间

标称位时间即位周期,是总线传输过程中每个位的传输时间.CAN 2.0协议的标称位时间由 4个互不交叠的部分组成,详细内容可以查看 CAN 2.0协议[4].本研究根据 CAN协议的位定时要求,提出了不同的标称位时间构成.在本研究中,标称位时间由 3个互不交叠的段 (同步段 (SYNC)、时间缓冲段1(TSEG1)和时间缓冲段 2(TSEG2))组成,即

TBIT=TSYNC+TTSEG1+TTSEG2. (1)

SYNC段用于同步总线上的各个节点,此段内要有一个跳变沿.TSEG1段和 TSEG2段用于补偿沿的相位误差,通过重新同步,这 2个时间段可被延长或缩短.

位周期中,这 3个段都用整数个基本时间单位即时间额数 (TQ)来表示.时间额数 (TQ)的持续时间为 CAN系统时钟周期 (TSCL)[5-6].

计算 CAN位定时,一个很重要的时间段是同步跳转宽度 (synchronization jump w idth,SJW),持续时间为 TSJW.SJW段不是位周期的一段,只是定义在重新同步事件中被延长或缩短的位周期的最大 TQ数量[7-8].

与位值息息相关的总线电平采样点是读总线电平并转换为相应位值的一个时间点.振荡器周期、系统时钟周期和位周期的关系如图 1所示.

图 1 位周期结构Fig.1 Bit cycle structure

1.2 与传统法的对比

新的标称位时间划分方法,不仅不会影响 CAN数据通信的可靠性和稳定性,而且还拥有以下几个优点:①减少了时序处理时间,原来传播段处理或者计算的时间减少了,使得 CAN总线通信的位时序处理更简捷;②降低了设计硬件实现的开销,不再需要原来传播段相关处理的相应硬件;③加强了CAN控制器的通用性,原来传播段长度要么根据使用环境作为专用芯片使用,要么就需要重新设置传播段的长度,而新的标称位时间的三段划分省略了这些步骤,显得更加实用.例如:MCP2515的位时序处理的标称位时间是四段划分的,在使用时需要设置 3个 8位寄存器,而使用本研究方法只需设置 2个 8位寄存器;相应的MCP2515因为四段处理而带来的硬件开销比本研究方法多,但使用起来却是后者更加方便与简单.

1.3 同步

为了保证报文可以完整地解码,CAN总线规范引入了 CAN总线同步,该技术可以清除节点之间相位误差的积累[9].为了补偿由振荡器漂移、节点间的传播延迟或者噪声干扰等情况所产生的相位误差,依照 CAN总线协议,在此定义两种类型的同步——硬同步和重新同步[9-10].

在一个位时间内仅允许一次同步.在空闲周期后,总线传输在一条报文的开头出现从隐性到显性的跳变时,处于 CAN网络中的每一个总线控制器同步于总线上的位流,则这个同步是硬同步,它只在报文帧的开始执行,并且一个报文帧内只执行一次.

在随后的报文剩余部分,每接收到一个隐性到显性的跳变沿就执行一次同步,这时的同步称为重新同步.由于 CAN编码中使用了位填充,所以最多相隔 10个位周期 (即 5个显性位和 5个隐性位)就执行一次重新同步,以使相位误差不形成积累[10-11].

2 位时序处理器的设计

2.1 总体结构设计

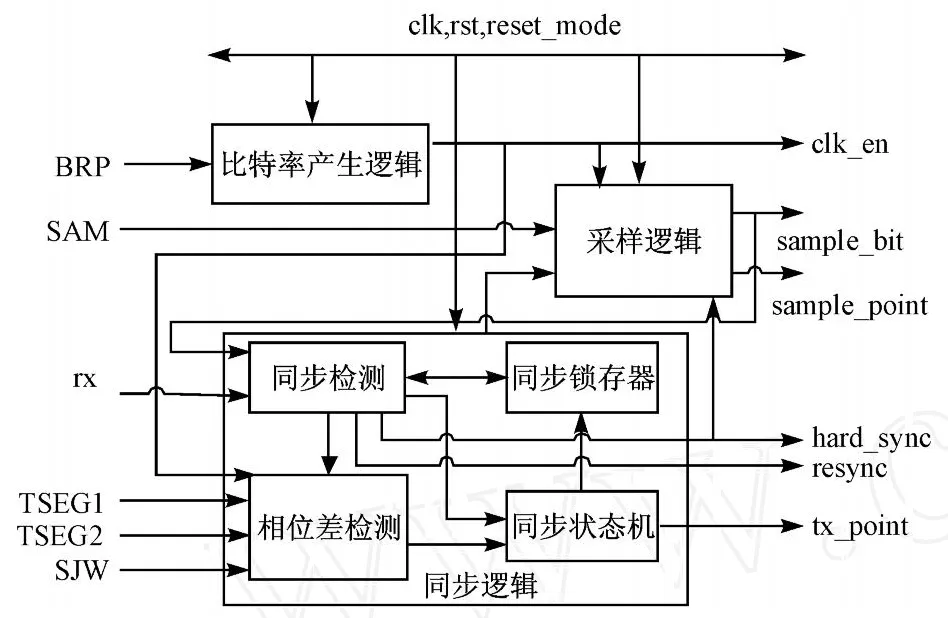

根据 CAN 2.0协议,BTP的工作流程可分为 3个步骤:①完成协议中各位定时段的设定;②检测跳变沿,根据同步类型 (硬同步或重新同步)执行同步;③进行采样[12].因此,可将 BTP划分为比特率产生逻辑、同步逻辑和采样逻辑,其结构如图 2所示.

图 2 位时序处理器结构Fig.2 BTP arch itecture

比特率产生逻辑根据位时序寄存器所定义的比特率,由振荡器周期分频得出系统时钟周期,即一个时间份额长度.再根据位时序寄存器所定义的位定时段,由时间份额计数得出各位定时段长度.

同步逻辑由同步检测电路、同步状态机、相位差检测电路和同步控制锁存器组成.在执行同步之前,首先要由同步检测电路来检测同步类型.

同步状态机控制同步逻辑执行对位同步的操作.当同步检测电路检测到的同步为重新同步时,相位差检测电路计算同步延长或同步缩短的相位差.同步延长与同步缩短的最大宽度由位时序控制寄存器的 SJW位给出.当相位差大于或等于 SJW时,同步延长或缩短 SJW;当相位差小于 SJW时,同步延长或缩短计算所得到的相位差值.

同步控制锁存器在执行同步的时候执行同步锁存,以达到 CAN规范在一个位时间内仅允许一次同步的要求.

采样逻辑在 TSEG1段到 TSEG2段的转换处进行采样,采样模式通过位时序控制寄存器的 SAM位控制.

2.2 同步状态机的设计与实现

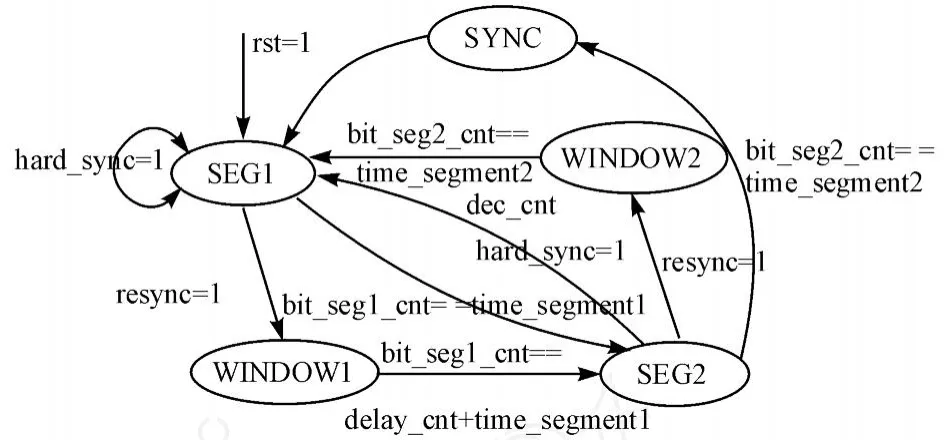

同步状态机定义了 5种状态,即 SYNC,SEG1,SEG2,W INDOW1和 W INDOW2,其中 SEG1和W INDOW1为采样前段周期 (TSEG1),SEG2和W INDOW2为采样后段周期 (TSEG2),W INDOW1状态为同步延长的状态,W INDOW2状态为同步缩短的状态.同步状态机状态跳转如图 3所示.

图 3 同步状态机状态跳转图Fig.3 Sync statemachine state sw itch d iagram

在接收到复位信号后,状态机进入 SEG1状态,初始化当前的位周期定时参数.在没有同步产生时,状态机在 SEG1,SEG2和 SYNC三个状态之间依次循环执行,即在 SYNC,TSEG1和 TSEG2这三个时间段依次循环执行,SYNC占一个时间额数 TQ,TSEG1和 TSEG2的大小由位时序控制寄存器 BTR1输入,其中 TSEG1段等于 SEG1,TSEG2段等于 SEG2.

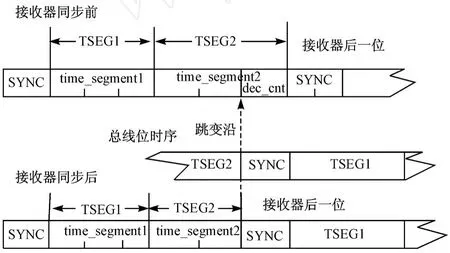

在 SEG1状态,如果没有同步信号产生,则在计数器满时进入 SEG2状态,此时 TSEG1段等于SEG1.如果在空闲周期后,总线传输出现从隐性到显性的跳变,接收器会将其解释成报文帧的起始符,执行硬同步“hard_sync=1”,接收器同步于总线上的位流,状态机重新进入 SEG1状态.如果接收报文帧时,检测到由隐性到显性的跳变沿,即跳变沿发生在 TSEG1段内,则在 SYNC后,但在接收器的采样点前,接收器会将其解释为一个慢速发送器发送的滞后边沿,执行重新同步“resync=1”,需要延长TSEG1段,即同步延长,状态机进入 W INDOW1状态.在该情况下,TSEG1段等于 time_segment1加上delay_cnt,TSEG2段等于 time_segment2,如图 4所示.

图 4 重新同步之同步延长Fig.4 Re-synchron ization extend ing

在 SEG2状态,如果没有同步信号产生,则在计数器满时进入 SYNC状态,此时 TSEG2段等于SEG2.如果检测到报文开头隐性到显性的跳变沿,执行硬同步“hard_sync=1”,状态机进入状态SEG1状态.如果在接收报文的过程中检测到隐性到显性的跳变沿,即跳变沿发生在 TSEG2段内,则在采样点之后,接收器会将其解释为一个快速的发送器发送的下一个位周期的提前边沿,需要缩短 TSEG2段,即同步缩短,执行重新同步“resync=1”,状态机进入W INDOW2状态.在这种情况下,TSEG1段等于time_segment1,TSEG2段等于 time_segment2减去dec_cnt,如图 5所示.

图 5 重新同步之同步缩短Fig.5 Re-synchron ization shor ten ing

W INDOW1状态是执行同步延长的状态,在TSEG1段延长后进入 SEG2状态,最大延长长度为SJW.W INDOW2状态是执行同步缩短的状态,在TSEG2段缩短进入 SEG1状态,最大缩短长度为SJW.在 SYNC状态,只要下一个 CAN系统时钟沿来到,则进入 SEG1状态.

3 仿真与验证

采用 Verilog语言对 CAN位时序处理器进行设计,且适用于 CAN 2.0协议所定义的所有传输情况.使用ModelSim SE 6.0对设计的 CAN位时序处理器进行功能仿真,并使用 Synopsys公司的综合工具Design Compiler对 CAN控制器进行综合设计(CHART0.35μm工艺库),最后使用 Cadence公司的ASTRO工具对 BTP进行布局布线,并再次进行仿真验证.图 6给出的是后端 (布局布线后)的仿真波形,其仿真的初始化设置如下:BRP=“000100”,SJW=“01”,TSEG1=“0100”,TSEG2=“011”,标准模式下接收数据端口“rx”接收数据长度为一个字节的标准数据帧,通信比特率为 100 kbit/s.

在总线空闲或者帧间空闲最后一位,接收数据端口“rx”出现隐性“1”到显性“0”的跳变沿时 ,执行硬同步“hard_sync=1”(见图 6中椭圆标注),原来同步状态机处在 SEG1状态“state=0”,硬同步后重新进入 SEG1状态,bit_seg1_cnt清零,重新计数.

图 6 BTP执行硬同步的仿真波形Fig.6 Simulation of BTP hard synchron ization

在 SEG1状态,即在 TSEG1段接收数据“rx”出现隐性到显性的跳变沿时,执行重新同步“resync=1”的同步延长 (见图 7中竖椭圆标注),同步状态机进入W INDOW1状态“state=1”,延长的宽度“delay_cnt”为 2个时间额数 TQ(见图 7中横椭圆标注).

图 7 BTP执行同步延长的仿真波形Fig.7 Sim ulation of BTP synchron ization extend ing

在 SEG2状态“state=2”,TSEG2段出现隐性到显性的跳变沿时,执行重新同步“resync=1”(见图 8中椭圆标注)的同步缩短,缩短 1个时间额数 TQ,使得同步状态机下一个 CAN系统时钟时进入 SEG1状态“state=0”.

图 8 BTP执行同步缩短的仿真波形Fig.8 Simulation of BTP synchron ization shor ten ing

数据的采样在 TSEG1段和 TSEG2段的交界处执行.TSEG1段出现重新同步时,在同步延长后再执行数据的采样,如图9所示 ,在TSEG1段出现重新同步,同步延长 2个时间额数后采样,即“bit_seg1_cnt==6”时 ,执行数据采样“sample_point=1”(见图 9中椭圆标注),采样值与接收值相同.

图 9 BTP执行采样的仿真波形Fig.9 Sim ulation of BTP sampling

4 结 束 语

合理地划分标称位时间的周期结构,准确地监测和处理总线上的位时序,关系到 CAN能否正确地收发数据.本研究提出了 CAN 2.0协议标称位时间的一种优化方法,将传统的标称位时间由 4个互不交叠的段简化成 3个互不交叠的段,并在此基础上提出了一种基于同步状态机的 CAN位时序处理器的设计方法.对所设计的 CAN控制器进行了一系列的功能和时序仿真,并使用 ASTRO工具对位时序处理器布局布线进行了后端仿真验证.结果表明,所设计的 CAN位时序处理器符合 CAN 2.0协议规范,能正确地接收数据,且适用于 CAN 2.0协议所定义的所有传输情况.相对于 CAN协议规范标称位时间的 4个互不交叠的段,减少了整个位时序处理过程使用的寄存器,简化了执行位同步的步骤,处理速度略有提高,更好地实现了 CAN总线协议中对位定时和位同步的控制,进一步优化了 CAN网络的性能.

[1] CORRIGAN S.Introduction to the controller area network(CAN)[R]. Texas Instruments Application Report SLOA101A,2008.

[2] JOHANSSON H K,TORNGREN M,N IELSEN L.Vehicle applicationsof controller area network[EB/OL].[2009-05-26].http:∥www.md.kth.se/RTC/Papers/Vehicle Applications Can 2005.pdf.

[3] RANGANATHAN K.RTL system design of CAN 2.0A controller[D].Texas:Texas Tech University,2005.

[4] BOSCH.CAN specification version 2.0[R].Postfach:Robert Bosch GmbH.1991.

[5] JIANG C R,CHEN W P,XU B S.Research and design on CAN bus bit time and synchronization[J].Low Voltage Apparatus,2009(3):39-42,55.

[6] TONGW M,CHEN P Y,GAO HW,et al.Research on CAN bit timing and synchronization mechanism [J].Chinese Journal of Electron Devices,2007,30(4):1499-1502.

[7] HARTW ICH F,BASSEM IR A.The configuration of the CAN bit timing[C]∥The 6th International CAN Conference.1997:1-10.

[8] KRISHNAMOORTHY S.Design of an ASIC chip for a controller area network(CAN)protocol controller[D].Texas:Texas Tech University,2006.

[9] SHAN L N,XU B S,CHEN W P.Research and design on CAN bus bit time and synchronization[J].Modern Electronics Technique,2009,32(12):142-145.

[10] DONCHEV B,HRISTOV M. Implementation of CAN controller with FPGA structures[C]∥ The 7th International Conference CADSM.2003:577-580.

[11] KIM N S,CHO K Y,KIM D W,et al.Design and verification of a CAN controller for custom ASIC[C]∥Proc 10th International CAN Conference on Semiconductor Solutions.2005:13-18.

[12] DZHELEK P,ZERBE V,ALEXIEV D,et al.FPGA implementation of bit timing logic of CAN controller[C]∥The 27th International Spring Seminar on Electronics Technology.2004:214-220.

Design and Realization of Controller Area Network Bit Tim ing Processor

HU Yue-li, XU Xiao-yong

(School of M echatronics Engineering and Automation,Shanghai University,Shanghai200072,China)

Theway in which the bit timing of controller area network(CAN)buscommunication isdealt with determineswhether the CAN controller can receive or transmit data correctly.Thispaper presents a structure of nominal bit time and the principle of bit synchronization.We give an optimized method of nominal bit time of CAN 2.0 p rotocol that the four non-overlapp ing segments of traditional nominal bit time is simp lified to 3 non-overlapping segments.Based on this,we p ropose a design method for bit timing processor(BTP)of CAN buson the synchronized state machine.We also provide programmable time segments to compensate for the propagation delay times and phase shifts,and show simulation and verification of the design.The results show that the design in line w ith the CAN 2.0 p rotocol can more easily deal with the CAN bus communication bit timing.Control of CAN bus protocol on the bit timing and bit synchronization is realized,which better op timizes the CAN network.

nominal bit time;synchronization;bit timing processor(BTP);controller area network(CAN)bus

TN 402

A

1007-2861(2011)01-0085-05

10.3969/j.issn.1007-2861.2011.01.014

2009-07-20

上海市科委集成电路设计专项资助项目 (09706201300);上海市信息化专项资助项目 (090344);上海市新能源汽车高新技术产业化基金资助项目(09625029)

胡越黎 (1959~),男,教授,博士生导师,博士,研究方向为汽车电子、机器视觉、IC设计等.E-mail:huyueli@shu.edu.cn

(编辑:刘志强)

控制器局域网 (controller area network,CAN)是 由 ISO定义的串行通信总线[1],最早由德国 Bosch公司提出.CAN具有可靠性高、无破坏仲裁性、多主、易实现等优点,在工业控制和汽车行业中得到了广泛使用,已成为现今应用最广泛的现场总线之一[2].