一种7GHz~20GHz宽带频率综合器的设计

覃洁琼,朱良凡,丁玉宁

(南京电子器件研究所,南京 210016)

1 引言

随着微波电子技术的发展,在21世纪以信息战为大背景的前提下,频率源作为现代电子系统的心脏,其指标要求自然越来越高。现代频率源除了要求低相位噪声、低杂散之外,高频率、宽频带、高功率、小体积、捷变频、小型化、数字化等性能也越来越重要。

频率综合器是利用各种频率合成技术来产生所需要频率的一种器件,其频率合成形式一般分为以下四大形式:直接频率合成(DS)、锁相环频率合成(PLL)、直接数字合成(DDS)、DDS+PLL形式。其中DS由于成本高、体积大、难集成等缺点已经很少应用;PLL因其极宽的输出频带、优良的频谱纯度等优势有着比较广泛的应用,缺点是频率捷变困难,频率分辨率不高;DDS则有着超快的捷变速度和极高的频率分辨率,不足之处为输出带宽有限和杂散指标不高;DDS+PLL则综合了前两者的优点,但一般在特定要求下应用。

2 性能指标分析

7GHz~20GHz宽带频综器的主要指标如下:

(1)工作带宽:7GHz~20GHz;

(2)变频间隔:10MHz;

(3)输出功率:>16dBm;

(4)杂波抑制:>60dBc;

(5)相位噪声抑制:<-65dBc/Hz@1kHz~1MHz;

(6)变频时间:<100 μ s;

(7)体积:<55mm×70mm×16mm。

综上所述,由于其工作频率占据了X波段、Ku波段和K波段三个波段,工作带宽达到了13GHz,对杂散抑制和相位噪声抑制的要求高,但是对变频时间的要求(100μs)PLL合成法也可以达到,所以只能运用锁相环频率合成形式才能兼顾以上所有指标。

3 系统电路设计

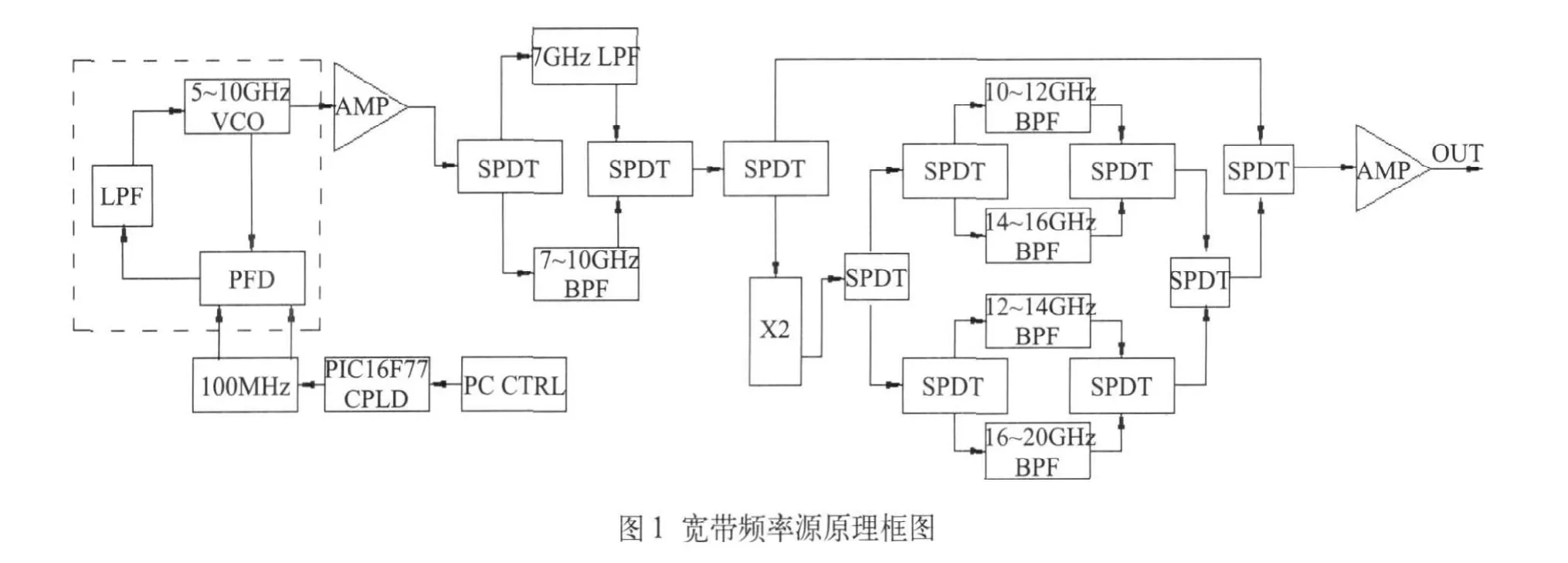

考虑到设计指标中的超宽带和小体积,本文所采用的方案为采用一个宽带的VCO和一个可编程小数N分频器产生一个宽频带的本振频率,然后进行倍频滤波从而得到7GHz~20GHz的频率。其具体的原理框图如图1所示。

3.1 PLL设计

系统采用Hittite 公司生产的5GHz~10GHz的宽带VCO HMC587LC4B,选用这款VCO的目的是为了直接产生5GHz~10GHz的频率,进行一次倍频就可以得到7GHz~20GHz的频率。

鉴相器也是选择同一公司的HMC702LP6C,此鉴相器是采用SiGe BiCMOS 工艺制造的一款小数分频锁相芯片,内部包含带Σ-Δ调制的小数分频器、低噪声鉴相器及可精细控制的电荷泵。

其主要特性及参考指标如下:

(1)射频端口带宽:14GHz;

(2)参考端口带宽:220MHz;

(3)整数小数分频模式可选;

(4)最大鉴相频率:75MHz(小数分频模式),150MHz(整数分频模式);

(5)噪声基底:-221 dBc/Hz(小数分频模式),-227dBc/Hz(整数分频模式);

(6)小数分频模长度:24bit;

(7)具有周期滑步预制功能。

系统提供的晶振参考频率为100MHz,本设计采用单环小数分频的模式,可以根据不同的频点选择使用小数分频模式或者整数分频模式,使得输出的相位噪声得到最优体现。

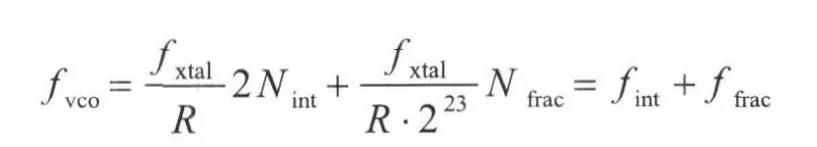

输出频率与小数N分频器的关系为:

其中VCO的输出频率fvco由晶振频率fxtal进行倍频产生,Nint为鉴相器分频比中的整数分频部分,而Nfrac为小数分频部分,R为晶振的分频比。整数分频比可从36~65533之间取值,小数分频可从1~224之间选择,R的取值也可以从1~214之间选择。主要是由编程控制鉴相器中Nint、Nfrac和R这三个值从而控制电荷泵输出达到控制频率的目的。

在小数分频模式,取R=2,则鉴相频率为50MHz,当输出频率为20GHz时,倍频次数为400,这样鉴相器片内分频器及鉴相频率带来的噪声为:

-221+10 log(50×106)+20 log(400)≈-92dBc/Hz@10kHz

再加上VCO、环路滤波器和倍频链路带来的相位噪声,最终达到<-65 dBc/Hz@10kHz应该是没问题的。

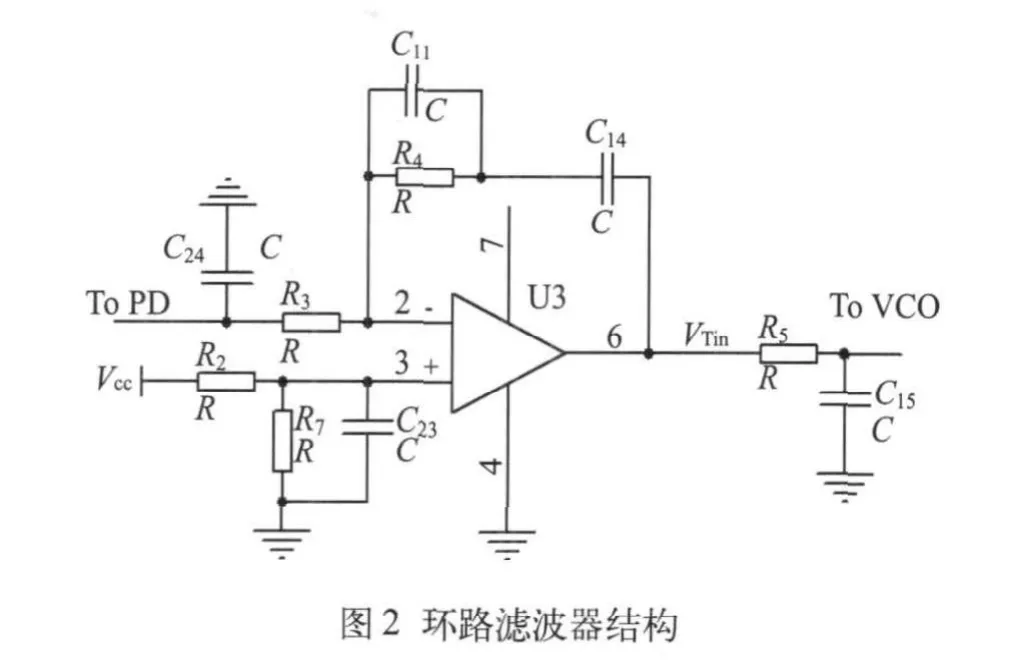

环路滤波器是设计的核心部分,考虑到VCO产生10GHz频率的时候,需要的调谐电压为0~13.5V,必须用运放才能提供足够的调谐电压,所以综合考虑选择四阶有源环路滤波器,其结构如图2所示。

环路带宽选在VCO和鉴相器相位噪声相等的地方,比较HMC587LC4B和HMC702LP6C发现,环路带宽选在200kHz左右比较合适,这样环路内的噪声取决于鉴相器,环路外的噪声取决于VCO。相位裕度选择在经典的45°~55°之间,本设计选择在48°。

鉴相器的鉴相电流从运放的反向输入端进入,正向输入端为电路提供参考电压,需要注意的是在编程时要将鉴相器中电荷泵的极性设置为反向才能使进入VCO的电压为正电压。同时需要注意通过Vcc来提供参考电压的时候有可能理论计算的电阻值R2、R7并不一定能恰好使参考电压等于偏置电压,这样就会使输出端的近端杂散变差,所以实际测试时要进行微调,以便提高杂散抑制。

环路滤波器参数的具体选择用Hittite公司研发的仿真软件进行仿真,并通过ADS2008进行仿真论证,得到了比较合理的参数。

3.2 倍频滤波设计

倍频滤波主要滤除的是由本振频率产生的2次谐波(5GHz~10GHz)以及倍频之后的本振频率及3次谐波。

由于通过VCO直接产生了5GHz~10GHz的频率,10GHz处的频点有5GHz的谐波频率,必须滤除。所以将5GHz~10GHz频率分为两路5GHz~7GHz、7GHz~10GHz分别滤波,再通过开关合为一路(如图1)。

5GHz~10GHz倍频之后产生10GHz~20GHz的频率,但是也同时会产生15GHz~30GHz的3次谐波,而且本振频率也要滤除,所以也要采取分段滤波的结构。将滤波器分为10GHz~12GHz(抑制6GHz和15GHz),12GHz~14GHz(抑制7GHz和18GHz),14GHz~16GHz(抑制8GHz和21GHz),16GHz~20GHz(抑制10GHz和24GHz),这样就很好滤除了各段的3次谐波和本振频率。

方案设计中滤波器全部选择由中电集团55所研制的MEMS小体积的滤波器组结合高速开关,并且合理划分了频段,各段独自调整功率,从而实现最终输出的平坦度要求,也可实现系统的小型化要求。

3.3 结构考虑

为了保证系统的杂散特性和相位噪声特性,除了环路滤波器要精心设计之外,电源的滤波也很重要,每一路接入射频电路的源电压都要做好滤波。由于使用了单片机和CPLD等中低频电路,所以要做好中低频电路和高频电路的信号隔离,截断任何一个信号串扰的可能性。在此设计中发现一个比较好的办法就是运用电容和磁珠做成π型的低通滤波器对电源进行滤波,达到了很好的滤波效果,测试结果显示此方法使输出频率的近端杂散抑制提高了10dBc左右。

同时,各路滤波器要做好相互之间的隔离工作,最好要用隔墙隔离,阻断频率间的空间传播。为了保证宽带特性和驻波性能,要尽量减少微带线的传输损耗,微带线的加工精度要高,微组装工艺严格、金丝的长短要合适。微带线的长度越短越好,接地性能要做到位。

为了实现小体积,除了选择合理的器件和MEMS滤波器之外,在设计的时候也要将腔体的正反面充分利用。并且将射频电路安排在腔体的正面,中频电路及电源电路安排在腔体的反面。

4 实测结果与分析

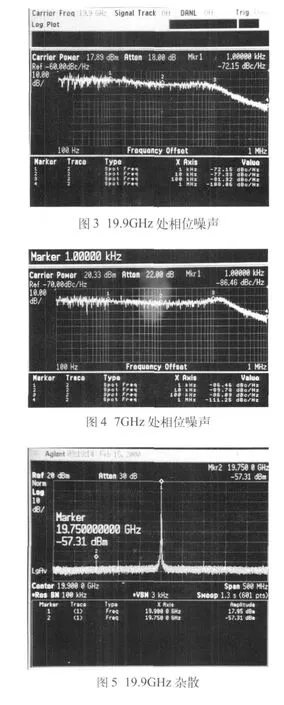

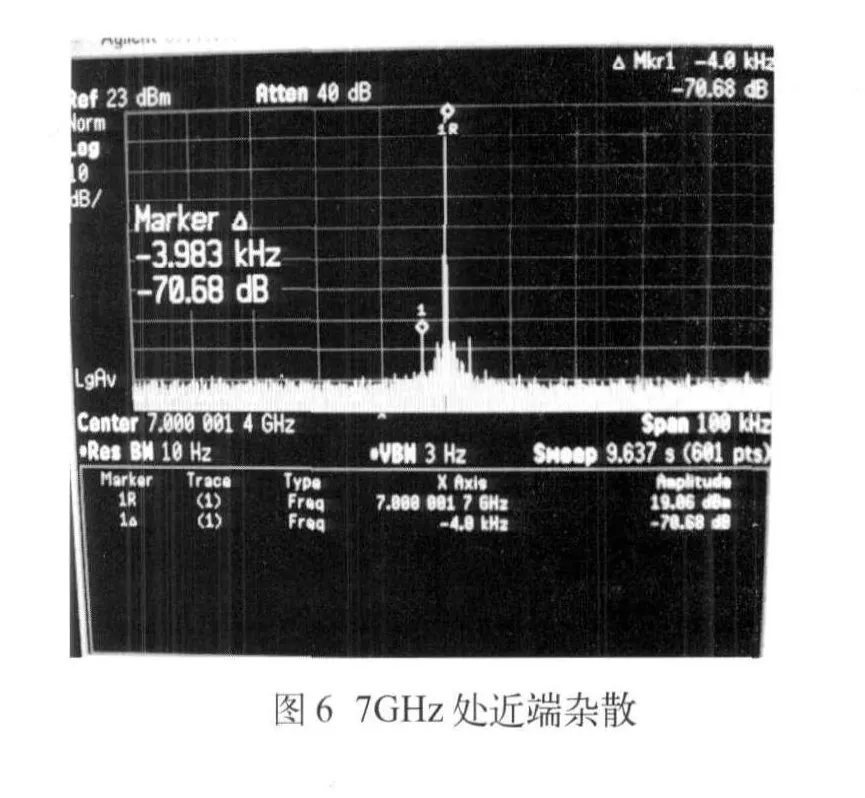

运用锁相环频率合成技术,通过精心设计和调试,已经研制出符合以上所有性能指标要求的频率合成器。如图3、图4所示,相位噪声最差的点在19.9GHz,分别为-72.15dBc/Hz@ 1kHz,-77.33 dBc/Hz@ 10kHz,达到了相位噪声的要求。而相位噪声在7GHz处为-86.46dBc/Hz@ 1kHz,-89.78dBc/Hz@10kHz。由于环路参数设计时环路带宽远小于鉴相纹波的带宽,在各个电源入口用电容和磁珠共同作用进行滤波,使得全频段的杂散都得到了比较好的抑制 。如图5、图6所示,全频段的杂散抑制可以达到杂散为17.95dBm-(-57.31dBm)=75.26dBc以上,符合要求。对全频段的输出点做了测试,其测试结果显示输出功率最小的点在19.2GHz处(为17.95dBm),达到了功率输出>16dBm的要求。在对变频时间的测试中发现,无论两个相邻频点之间的跳变(如从7GHz跳变到7.001GHz)还是跨度比较大的两个频点的转换(如从7GHz跳变到20GHz),其变频速度都可以达到<100 μ s,也达到了要求。

5 结束语

高科技迅速发展的今天,无论是雷达、通信、电子对抗技术还是数字电视技术等,都对系统的可靠性和小型化提出了更高的要求,相对于同类产品的研究水平,本产品在设计中最突出的优点在于在宽频带的前提下很好地实现了产品的小型化,体积达到了类似产品的一半。

希望在以后的研究中,在保证小型化的基础上能进一步提升系统的性能,改善系统的相位噪声、功率平坦度等指标。

[1]远坂俊昭,何希才.锁相环(PLL)电路设计与应用[M].北京:科学出版社,2006.

[2]Vadim Manassewitsch,何松柏,宋亚梅,等.频率合成器原理与设计[M].北京:电子工业出版社,2008.

[3]Floyd M.Gardner,姚剑清.锁相环技术[M].北京:人民邮电出版社,2007.

[4]涨厥盛,郑继禹,万心平.锁相技术[M].西安:西安电子科技大学出版社,2005.

[5]赖益,蔡竟业,杨远望,等.3-16GHz宽覆盖频率合成器的研制[J].电视技术,2009,49(11).