共漏极双功率MOSFET封装研究

毕向东

(广东省粤晶高科股份有限公司,广州 510663)

1 引言

共漏极双N沟道或者双P沟道功率MOSFET的两只寄生体二极管反向串联,当一只MOSFET关闭时,其寄生体二极管可以传导电流,所以共漏极双功率MOSFET具有双向电流传输特性,因而特别适用于锂电池和锂电池组的充放电保护电路。锂电池能量密度大的优良特性仍不断提升,锂电池的体积也越来越轻薄短小,继而要求其充放电保护电路模组体积相应地缩小。

所以近年来应用于锂电池市场的共漏极双N沟道或者双P沟道功率MOSFET的封装外形也越来越小,封装效率越来越高,而封装的电、热性能也有所提高。

2 共漏极双功率MOSFET及应用特点

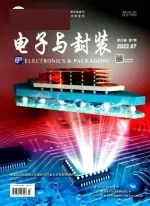

一般负极保护原理的锂电池保护电路示意图如图1,使用共漏极双N沟道功率MOSFET。若是正极保护原理,则使用共漏极双P沟道功率MOSFET。共漏极双功率MOSFET分别控制锂电池的充电和放电回路的通断,还起着隔离电池保护系统负载的作用。由于共漏极双功率MOSFET与系统负载串联且具有一定的导通电阻RS1S2(ON),即相当于单个功率MOSFET导通电阻的2倍(RS1S2(ON)=2×RDS(ON)),在大负载电流条件下,将消耗大量无用功率,损耗较多的电池电量,缩短电池单次充电的使用周期。同时,双功率MOSFET的导通电阻消耗无用功率导致电路模组和电池包温升和发热,损害电池使用的可靠性和安全性。所以,缩小器件的导通电阻成为提高共漏极双功率MOSFET性能指标的关键因素。

3 传统封装技术及其缺陷与克服

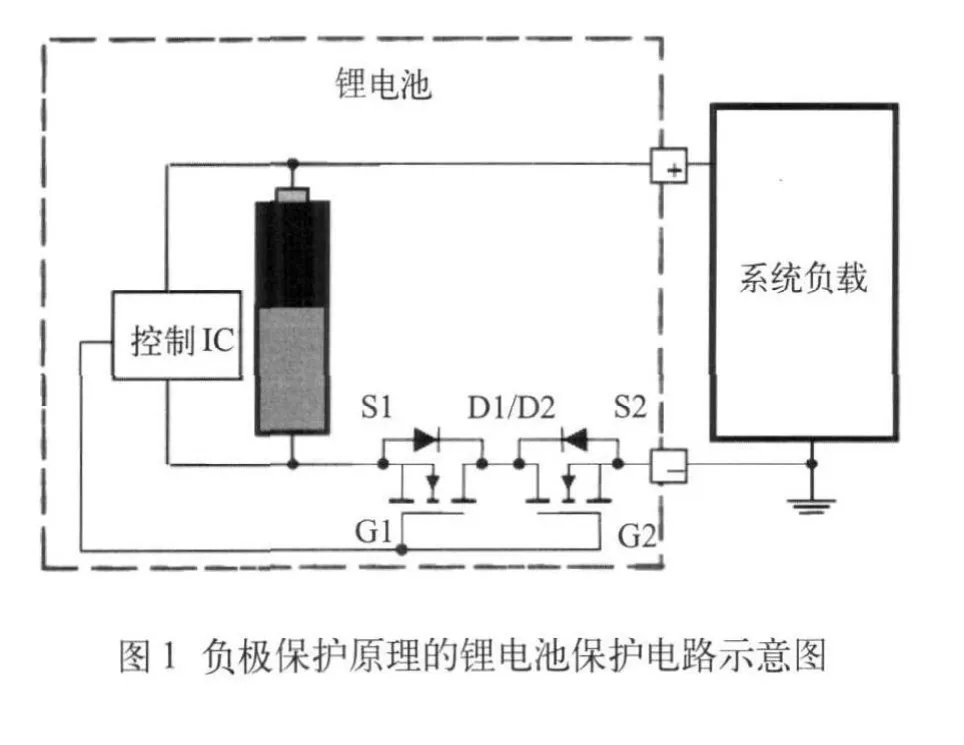

目前传统的共漏极双功率M OS F ET多采用TSSOP-8封装,其封装外形、内部互连结构如图2所示。以耐压20V、额定电流7A的功率MOSFET为例,双芯片面积一般不超过1.20mm×0.95mm,TSSOP8封装占位面积为6.4 mm×3.0mm,所以封装效率即芯片/封装面积之比仅为6%。共漏极双功率MOSFET一般属于高密度沟槽栅极工艺器件,芯片导通电阻可低至20mΩ以下,此时封装电阻就不容忽略。由图2(b)可直观看出,由于芯片小、封装框架大,源极焊线较长,长度约为1.6mm,以45.7μm铜线计算,单条焊线电阻高达17m Ω,导致封装电阻较大,最终器件的导通电阻RDS(ON)增加。

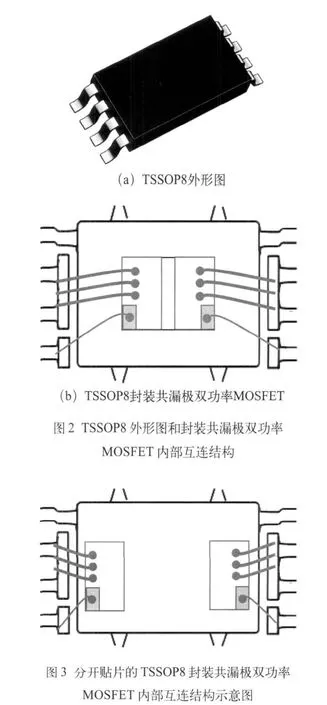

为克服长焊线引入较大封装电阻的问题,可采用分开划片、再分开贴片的方式,使两只芯片对称地靠近两侧焊脚位,见图3,可缩短焊线长度至0.91mm,以45.7μm铜线计算,单条焊线的电阻为10mΩ,减小了7 mΩ。此外,焊线缩短减少了原材料消耗,降低了成本。高可靠性场合需求的共漏极双功率MOSFET常采用金焊线,若焊线长度由1.6mm缩短为0.91mm,长度缩短43%,以源极焊3条45.7μm金线计算,可节省成本40%以上,若以源极焊5条45.7μm金线计算,可节省成本60%以上。焊线缩短的另一个优点是抗焊线漂移和焊线坍塌能力增强,提高了产品可靠性和封装良率。

但是分开划片、再分开贴片的封装方式需要增加划片次数、点胶次数和贴片次数,降低了生产效率,也降低了产品质量的一致性和稳定性。

4 替代改进型封装技术

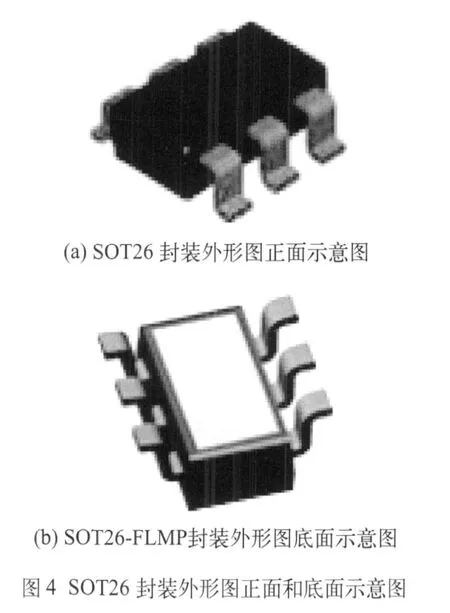

针对TSSOP8封装效率偏低和生产效率降低的问题,又相继开发出了小型化的SOT26和共漏极焊盘暴露的SOT26-FLMP,如图4。SOT26和SOT26-FLMP的封装占位面积都是3.0mm×3.0mm,封装上述1.20mm×0.95mm双芯片,封装效率与TSSOP8相比提高了1倍多,达到了13%。SOT26-FLMP封装底部漏极焊盘外露,更有利于散热,提高系统的可靠性和安全性。

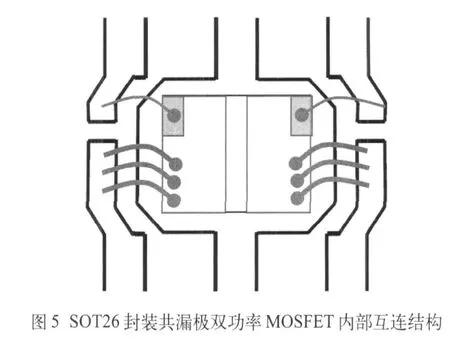

图5 是SOT26封装共漏极双功率MOSFET内部互连结构示意图,封装的引线架进行了重新设计,仍然保持两只芯片划在一起,单次点胶再完成贴片工艺,提高了生产效率、产品质量一致性和稳定性。同时,封装外形体积紧凑,较短的源极焊线长度不引入额外的封装电阻。

5 封装技术发展趋势

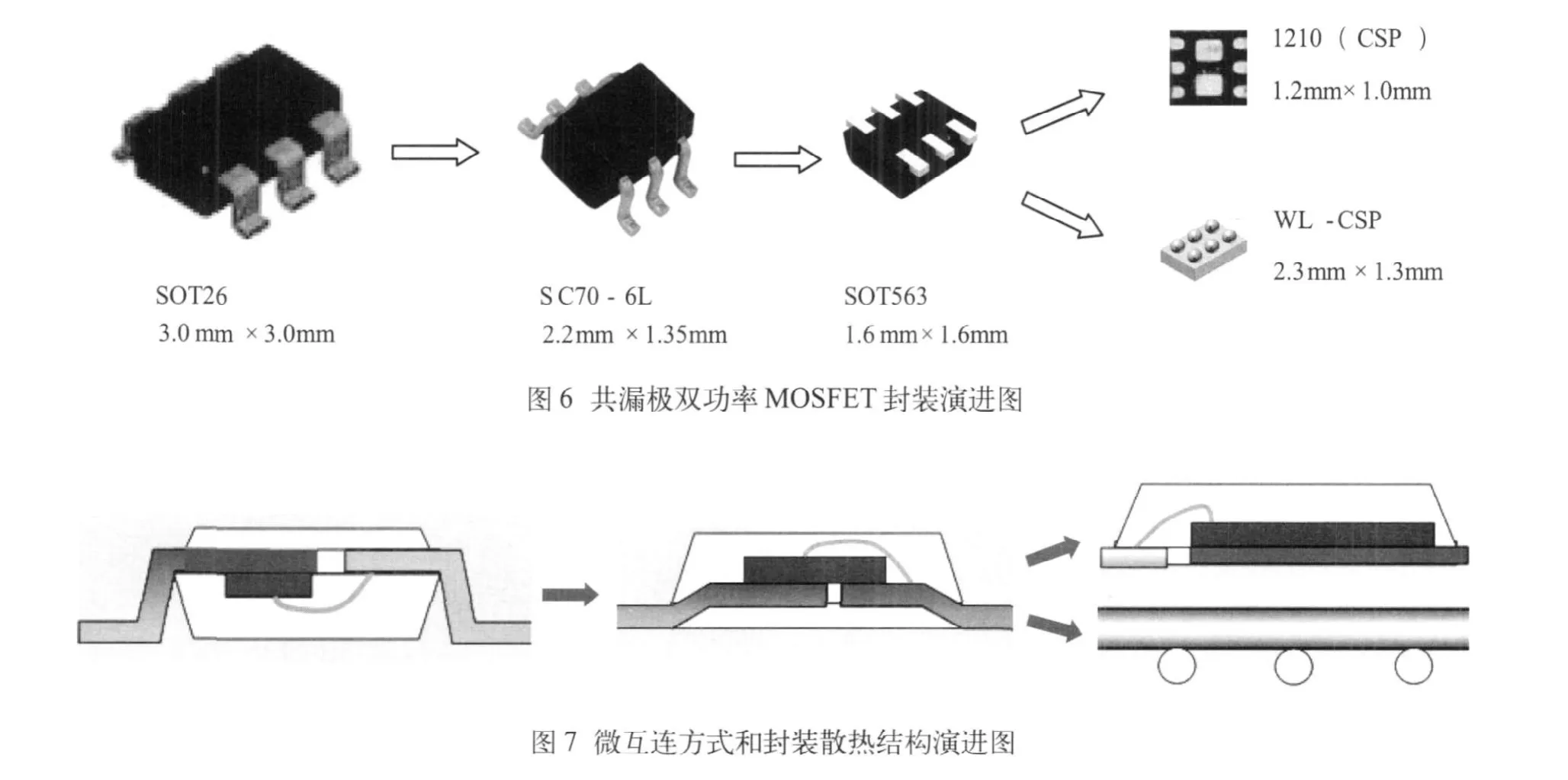

未来共漏极双功率MOSFET的封装将向着微型化、先进微互连方式和良好散热结构方向发展。图6是共漏极双功率MOSFET封装演进图,可以看出封装外形更加微小,封装效率越来越高,直到CSP/WLCSP级别,封装效率可接近100%。

从图6中还可以看出,微互连方式和散热结构仍在改善和提高。低弧度焊线和焊球倒装互连使得导通电阻降低。从传统的翅形引脚到缩短的平坦引脚、超薄型封装再到漏极焊盘暴露的封装结构,使得器件热阻抗降低,散热效果增强,如图7所示。

6 结束语

传统的共漏极双功率MOSFET采用TSSOP8封装,分开划片和分开贴片的方式与单次划片和单次贴片的方式相比,具有较短的源极焊线长度,降低了物料成本,具有更低的导通电阻,提升了器件的关键电性能指标,但是降低了生产效率,损害了产品质量的一致性和稳定性。而采用小型化的SOT26、SOT26FLMP替代封装,则很好地解决了这两方面问题。随着锂电池的小型化,未来的共漏极双功率MOSFET将继续朝着微型化封装方向发展,同时采用低弧度焊线和焊球倒装微互连方式使得导通电阻大大降低,平坦式引脚、超薄型封装和漏极焊盘暴露的封装结构有利于良好的散热,使得器件热阻抗降低,提高了器件、电路系统和电池包的可靠性和安全性。

[1]LI Zhibo, CHU Huabin, CHEN Supeng, et al. Thermal stress analysis and optimization for a power controller SiP module[C]. The 11th International conference on electronic packaging technology & high density packaging. Xi’an, China, 2010.

[2]褚华斌.表面贴装功率MOSFET封装技术研究进展[J].半导体技术, 2010, l35:65-67.