ASIC电路中时钟驱动的抗单粒子加固

王 栋,徐 睿,罗 静

(中国电子科技集团公司第58研究所,江苏 无锡 214035)

1 引言

CMOS工艺制成的ASIC电路在太空中应用时,常常会因为受到总剂量效应(TID)、单粒子翻转效应(SEU)、单粒子瞬态效应(SET)等辐射效应的影响,导致数据出错,影响整个系统的可靠性。在原先大尺寸工艺条件下,由于栅氧化层较厚、场氧存在“鸟嘴效应”,在辐射环境中,电路的总剂量效应影响十分严重。其次,单粒子翻转效应(SEU)也会影响电路中的锁存结构,使得被锁存数据出错。随着工艺尺寸的不断缩小,栅氧化层的厚度不断减薄,到了深亚微米工艺条件下,原先的局部氧化隔离(LOCOS)优化成潜槽隔离(STI),外加利用版图加固等手段,大大缓解了总剂量效应对电路的影响。

但是,随着CMOS关键尺寸的不断减小,使得节点电容不断减小,并且系统的电源电压也在不断降低。这样,电路就更容易受到单粒子效应的影响。值得注意的是,随着电路工作频率的增加,电路中由单粒子瞬态效应(SET)引起的错误数不断增加,对系统的影响越来越大[1,2]。其中,时钟驱动电路(CLK)受SET效应影响对整个电路而言最为严重。本文首先分析了SET效应对时钟树的影响,然后提出了几种加固方案,接着对几种方案的原理和性能进行了分析。

2 单粒子瞬态效应对时钟电路的影响

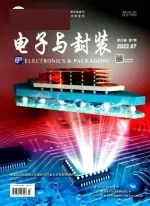

一个简单的H型时钟树电路如图1所示。

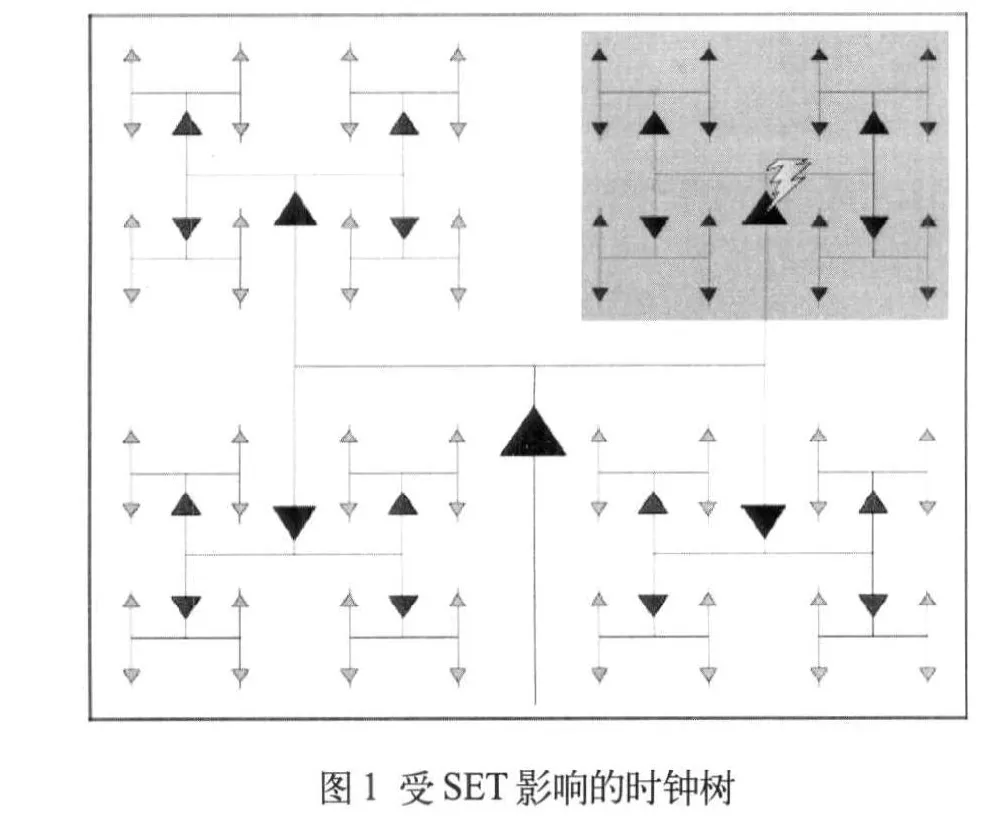

假设时钟树在一个二级驱动上受到了单粒子效应的影响,在该级上产生的瞬态扰动将依次传递给第三级和第四级。如果由单粒子扰动产生错误的时钟信号传递到触发器,将使触发器锁存错误的信号[3,4]。简单的波形如图2所示。

图2(a)为正常情况下时钟信号和对应的数据信号波形。在时钟CLK信号的上升沿,电路将输入信号D的数据锁存,使Q端的状态从低电平变为高电平。但当CLK信号受到单粒子效应影响后,产生了一个与时钟信号可比拟的扰动脉冲,其波形如图2(b)所示,此扰动会引起触发器错误翻转,锁存错误的数据,从而影响整个电路的工作状态。同样,如果RESET复位信号受到扰动,将会错误地使触发器置位或清零,也导致整个芯片出错。

随着关键尺寸的缩小、电源电压的降低、电路工作频率的增加,单粒子瞬态效应对电路的影响越来越大。在深亚微米条件下,时钟电路的单粒子效应已经成为制约芯片在辐射条件下正常工作的主要因素。因此,如何对时钟电路的单粒子效应进行加固,是我们此次研究的重点。

3 时钟电路的加固设计

针对CLK电路,本文提出了四种电路级的加固方案,包括加入Schmitt 电路、延时滤波器、三模冗余结构、增加结点电容。

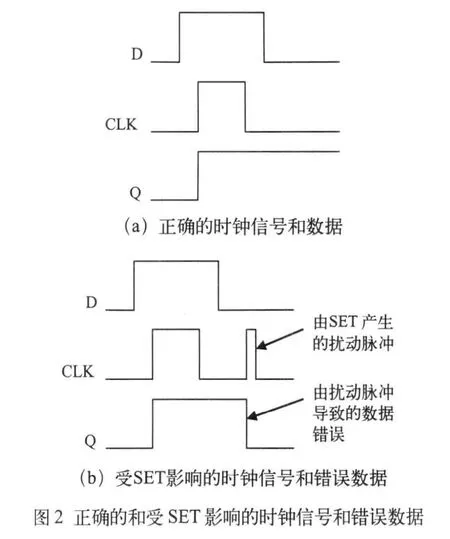

3.1 采用Schmitt电路加固设计

Schmitt电路原理图如图3所示,由PMOS管Tp1~Tp3,NMOS管Tn1~Tn3组成。设PMOS管的开启电压为VTP,NMOS管开启电压为VTN,输入信号VI为三角波。

当VI=0时,Tp1、Tp2导通,NMOS管截止,输出VO为1。VO的高电平使得Tp3截止,Tn3导通且工作于源极输出状态。Tn2的源极保持高电位,为VDD-VTN。

当VI电位逐渐升高、VI>VTN时,Tn1首先导通,由于Tn2的源极保持高电位,即使VI>VDD/2时,Tn2仍然不能导通,直到VI继续升高直至Tp1、Tp2趋于截止时,随着内阻的增加,VO才开始相应地减小。当VI-Vsn2≥VTN时,Tn2导通。并引起正反馈,使得Tn2的导通电阻下降。随之,Tp1和Tp2迅速截止。VO转换为低电平。VO的低电平使得Vn3截止,Tp3导通并工作在源极输出状态,Tp2的源极电压Vsp2=0 -VTP。

同理可知,当VI逐渐下降时,电路工作过程与VI上升过程类似,只有当|VI-Vsp2|>|VTP|时,电路又变为输出为高。

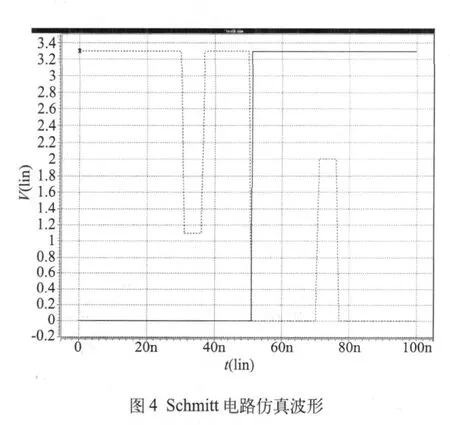

综上所述,Schmitt电路有两个不同的阈值电压,正向阈值电压会比VDD/2大很多,而负向阈值电压会比VDD/2低。正是利用了该特性,使CLK电路能够滤除一些不需要的毛刺,从而具有了抗SET效应的能力。电路仿真图如图4所示,当扰动使高电平从3.3V降低至1.1V,或将低电平从0V抬高至2V,经过Schmitt电路后的波形还能保持不变。设计时将Schmitt作为时钟树的末级驱动,可滤除CLK信号中不必要的干扰。

3.2 采用延时滤波器的加固设计

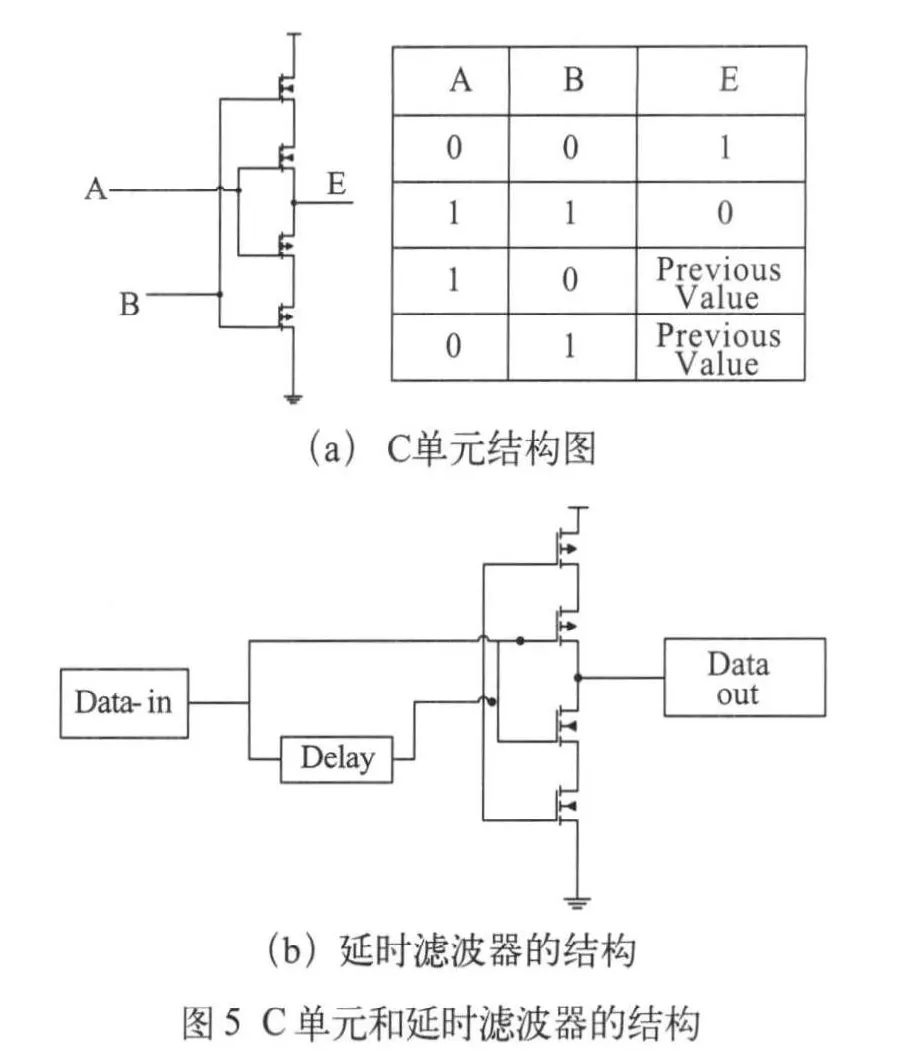

延时滤波器是基于C单元[5]而设计的,C单元的结构如图5(a)所示。C单元相当于一个反相器,但只有当两个输入端A和B状态相同时,输出端E的状态才会改变,而如果A和B的状态不相同,E则保持原有的状态不变。将延时单元加入C单元中的一个输入端,如图5(b)所示,使同一信号在两个时间内进行运算[6],这样就构成了一个延时滤波器。

延时滤波器是在时间域上对CLK电路进行加固,要求延时单元的时间要大于SET对CLK信号扰动的时间,通过对两个不同时间点的数据进行操作,输出最后的信号。

3.3 三模冗余的加固结构

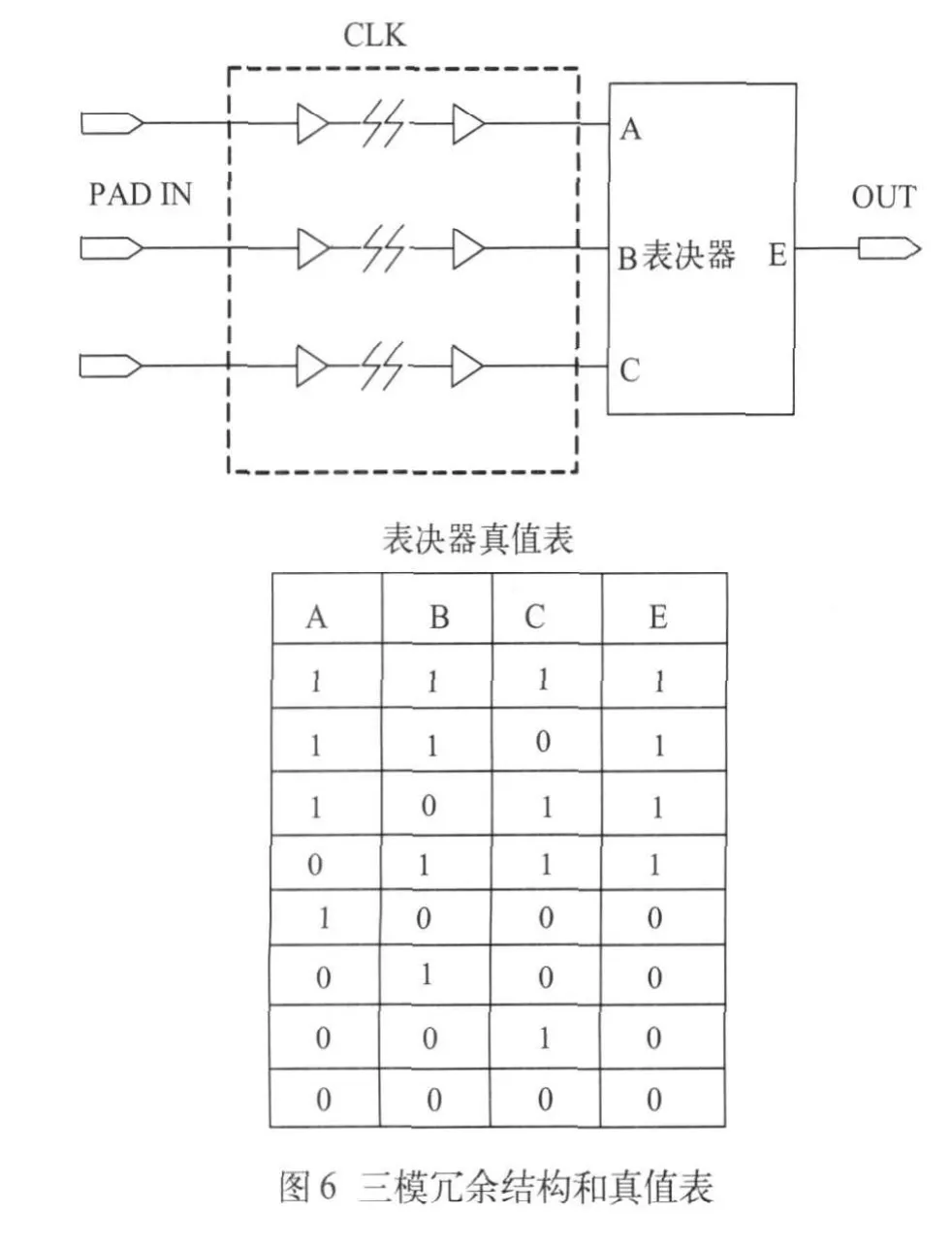

三模冗余结构是将一个CLK信号扩展为三路信号,然后通过一个表决器将最终的CLK信号提供给电路。只要其中两路或以上信号有效,则输出的信号有效,其电路结构和真值表如图6所示。在设计输入时,要求同时有三个时钟信号输入。在内部布局布线时,要求三路信号排布上分开,以避免单粒子同时扰动两路信号。利用三模冗余结构,只要保证三路中有两路信号正确,就可以将正确的CLK信号输出至所需的时序逻辑。

3.4 增加结点电容的加固设计

通过增加结点电容来对时钟信号加固,最简单的方法就是增加反相器的W/L,以起到保护CLK数据传输的作用。研究表明,在90nm工艺条件下,当反相器的驱动能力大于18×时,其有很好的抗单粒子效应的能力[7]。因此,我们也将增大反相器W/L作为一种加固方案。

以上介绍了四种CLK电路的加固方案,接下来将对每种方案的特点进行分析。

4 加固方案的性能分析

利用0.18μm工艺库,对以上几种加固方案进行了Hspice仿真分析,以比较各个加固方案的优缺点。

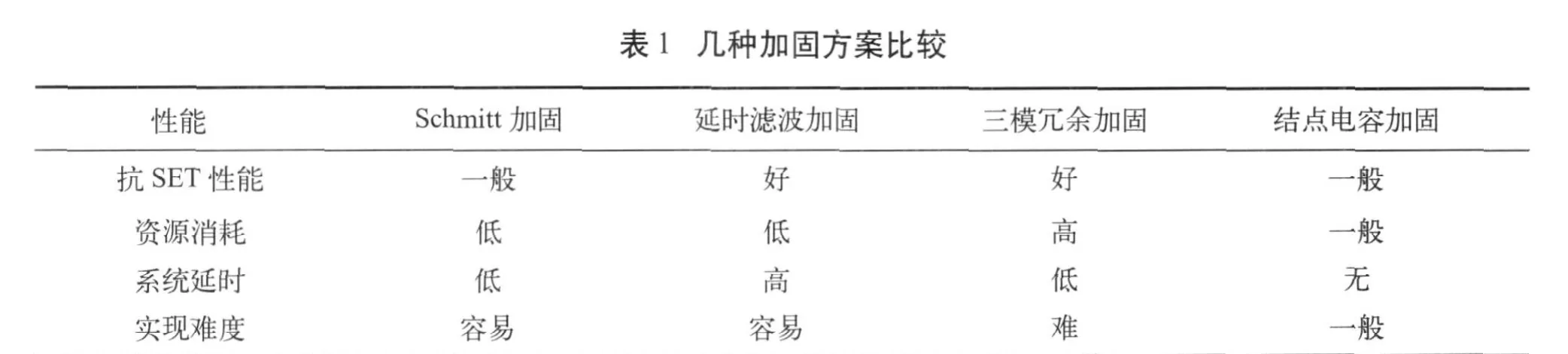

(1)利用Schmitt电路对CLK加固后,可以减轻SET效应对CLK的影响。其对系统的延时影响很小,可以控制在100.s-1以内,功耗增加也不是很大。而且,Schmitt电路输出端的结点电容较大,也会在一定程度上抑制辐射效应对下一级电路产生的影响。但是问题在于,当电源电压降得很低、而辐射引起的SET效应产生的扰动达到与电源电压可比拟的量级时,Schmitt电路加固的作用就完全丧失了,它会将与CLK信号摆幅相似的大扰动信号输出至系统,导致系统出错。

(2)利用延时滤波器对CLK电路加固后,可以消除SET效应对CLK的影响,对系统功耗增加不是很大。但延时滤波器的缺点在于:为了达到加固的目地,增加了CLK端的延时,限制了电路在高速情况下的应用。为达到CLK和数据信号在时序上的统一,需要在数据输入端也增加延时滤波单元,限制了整个芯片的工作速度,也给系统增加了额外的资源消耗。

(3)利用三模冗余结构对电路加固后,也可以消除SET效应对CLK的影响,同时不会对系统造成很大的延时影响。但此加固方案的缺点在于严重加剧了系统的功耗开销和芯片面积。由于需要将原本一路的CLK信号复制成三路,再通过表决器表决,其方案将CLK信号所需要的资源增大了数倍。对于超大规模系统芯片而言是难以接受的。所以,利用此方案加固,需要综合考虑到对系统功耗和版图面积的影响。

(4)利用增加结点电容的方法对CLK信号加固后,可减轻SET对电路的影响,同时不影响系统工作频率。缺点就是,太大的后级驱动管,给前级驱动管的W/L提出了很高的要求,很可能需要上百的宽长比,对系统的功耗和面积也提出了挑战。

综上所述,几种加固方案的优缺点比较如表1所示。

5 总结

文章针对ASIC电路中CLK驱动抗SET效应加固进行了探讨。分析了深亚微米工艺条件下,SET效应对CLK电路的影响。对此,提出了四种加固设计方案,分析了四种加固方案的机理,并比较了四种加固方案的优缺点。经研究得出:在对ASIC电路的CLK进行抗SET加固时,需要折中考虑规模、功耗、延时等因素。在电路复杂度不高的情况下,可考虑用三模冗余结构加固,在电路工作频率不是很高的情况下,可考虑用Schmitt或延时滤波结构进行加固。如果电路的复杂度和频率都比较高,则可以考虑使用增加结点电容的方式,局部采用三模冗余或滤波延时进行加固。此研究为以后研制抗辐射ASIC电路提供了良好的借鉴和基础。

[1]J. Benedetto, P. Eaton, K. Avery, et al. Heavy Ion-Induced Digital Single-Event Transients in Deep Submircon Processes [J]. IEEE Transactions on Nuclear Science, 2004,51(6):3 480-3 485.

[2]J.M. Benedetto, P.H. Eaton, D.G.Mavis, et al. Digital Single Transient Trends with Technology Node Scaling [J]. IEEE Transactions on Nuclear Science, 2006, 53(6):3 462-3 465.

[3]J.M. Benedetto, P.H. Eaton, D.G.Mavis, M.Gadlage, T.Turflinger. Variation of Digital SET Pulse Widths and the Implications for Single Event Hardening of Advanced CMOS Processes [J]. IEEE Transactions on Nuclear Science, 2005,52(6):2 114-2 119.

[4]Jih-Jong Wang, Richard B. Katz, Fethi Dhaoui, et al. Clock Buffer Circuit Soft Error in Antifuse-Based Field Programmable Gate Arrays [J]. IEEE Transactions on Nuclear Science,2000, 47(6):2 675-2 681.

[5]S. V. Devarapalli, P. Zarkesh-Ha, S. C. Suddarth, SEU-hardened Dual Data Rate Flip-Flop Using C-elements [C]. 25th International Symposium on Defect and Fault Tolerance in VLSI Systems, 2010. 167-171.

[6]P. Mongkolkachit, B. Bhuva, Y. Boulghassoul, J. Rowe, L.Massengill. Mitigation of Single-Event Transients in CMOS Digital Circuits [C]. Proceedings of Radiation and its Effects on Components and Systems, Noordwijk, Netherlands,2003.

[7]Manuel Cabanas-Holmen, Ethan H. Cannon, AJ Kleinosowski, et al. Clock and Reset Transients in a 90nm RHBD Single-Core Tilera Processor [J]. IEEE Trans. Nuclear Sci., 2009, 56(6): 3 505-3 510.