面向高性能众核处理器的超频DDR4访存结构设计

高剑刚,李 川,郑 浩,王彦辉,胡 晋

(1.国家并行计算机工程技术研究中心,北京 100190;2.江南计算技术研究所,江苏 无锡 214083)

0 引 言

存储系统是高性能计算机系统结构中的重要组成部分。国内超算系统神威·太湖之光[1]、天河2A[2]采用DDR3/4内存技术,接口速率2133 Mbps~2400 Mbps。国外超算系统Summit[3]、Sierra[3]采用处理器芯片DDR4与加速芯片HBM2[4](high-band width memory)的内存组合方式,DDR4接口速率2666 Mbps。TOP500排名第一的超级计算机Frontier[5]内存系统为DDR4和HBM2e,DDR4接口速率3200 Mbps。作为传统存储并行互连技术,DDR4在高性能计算机中应用广泛。

DDR4应用于超算系统主要有两种方式,一是标准内存条插装[6],二是存储颗粒嵌入PCB(printed circuit board)表面贴装。嵌入式贴装典型系统是神威·太湖之光[7],该方式可以释放贴装高度方向空间,也有助于减少由接插器件导致的信号畸变,但是,对DDR4访存结构设计和信号完整性设计[8]要求很高。

业界关于DDR4的研究有访存分析[9]、接口电路物理设计优化[10]、链路串扰分析[11,12]等,针对嵌入式互连结构[13]的研究偏少。在信号完整性问题分析中,DDR4地址组总线和数据组总线眼图仿真较少联合分析两大类信号以及数据码型对信号传输的影响[14,15]。本文以DDR4嵌入式表面贴装应用为背景,设计了一种高密度串推结构,根据结构特点进一步提出了基于码型的仿真分析方法。并对仿真发现的地址组信号概率性出错问题进行了结构优化分析和测试验证。

1 串推结构设计

DDR4信号可以分为命令地址控制信号(后文简称为地址组信号)和数据信号两大类[16],以单端信号为主,只有时钟信号和数据选通信号是差分方式。地址组信号经处理器驱动后,依次经过多片存储颗粒,最后到达端接器件。数据信号采用点到点拓扑结构,即处理器与每片存储颗粒直连,信号双向传输。

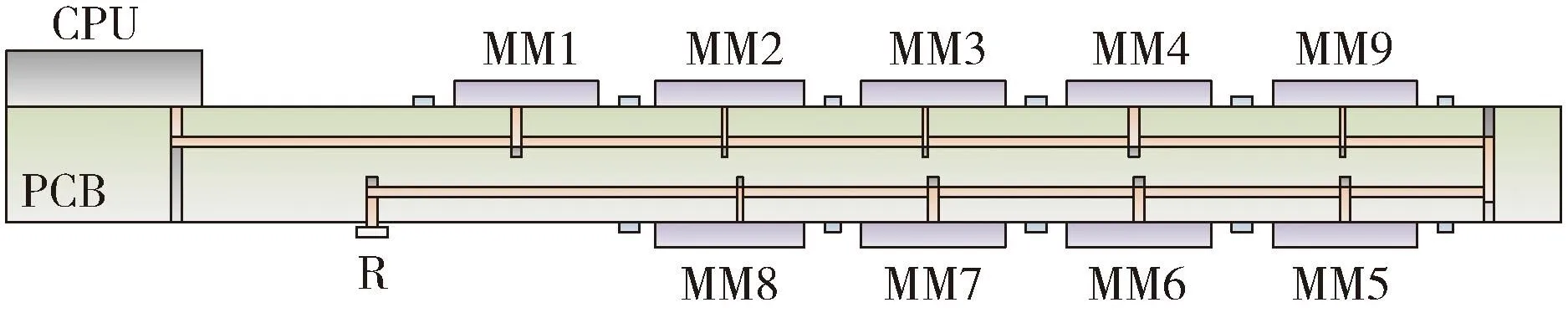

根据信号拓扑特点,针对高性能处理器高频应用,即一套存储控制器与9片存储颗粒(8片信息存储+1片传输校验)互连,考虑高效利用板面布局空间,同时控制数据信号点到点互连长度,设计如图1所示串推结构。

图1 串推结构及管脚阵列俯视图

在该串推结构中,地址信号从处理器出发,依次连接印制板上、下表面的存储颗粒MM1和MM2、MM3和MM4……最后到达端接电阻R。印制板上、下表面存储颗粒管脚阵列重合,以MM1和MM2的管脚俯视图为例,MM1管脚A1至N1与MM2管脚A9至N9完全重合,管脚A2至N2与A8至N8重合,以此类推。同一地址信号在MM1和MM2之间存在两种互连方式:单孔互连和双孔互连。单孔互连结构中,信号通过同一个孔与两片存储颗粒信号管脚相连,共孔的管脚主要为两个颗粒的第3列和第7列。因为3、7两列管脚引盘至共孔,空间充足。双孔互连结构中,信号先经过MM1和MM2中靠近处理器一侧的引盘孔,再印制线互连至远离处理器一侧的引盘孔。图中虚线把存储颗粒管脚分为上下两个区域,颗粒上半部分是数据组信号管脚(DQ标识区域),颗粒下半部分是地址组信号管脚(AC标识区域),地址组和数据组两类信号管脚在空间上无交叠。

采用该串推结构,存储颗粒在印制板两侧面对面贴装,可以提高布局密度,同时有效控制数据信号布线距离。由于地址组信号引盘孔阵列与数据组信号引盘孔阵列无交叠,地址组与数据组可以实现同层无交叉布线,布线密度大幅提升。

根据该结构进行布局布线设计,9片存储颗粒数据组线长各颗粒组等长,最长线组为180 mm。地址组信号以时钟信号为目标进行等长设计,处理器至到首片颗粒段线长等长。印制板板厚3.5 mm,信号孔孔径0.25 mm,盘径0.45 mm,隔离盘大小为0.65 mm,信号孔连接盘只在印制板两个表面和布线层保留。

2 码型仿真

2.1 传统总线仿真

DDR4总线设计仿真分析中,常用做法是:基于三维电磁场仿真分析软件建模提取包括封装段和PCB段的地址总线、数据总线物理通道的散射参数(S参数)模型,然后在电路仿真软件中搭建包含通道S参数、存储控制接口电路IBIS(input/output buffer informational specifation)模型以及存储颗粒接口电路IBIS模型的链路拓扑,并根据数据地址信号类别以及信号速率设置恰当的激励参数、端接参数和分析求解参数,最后在接收端观察信号仿真眼图是否符合规范要求。

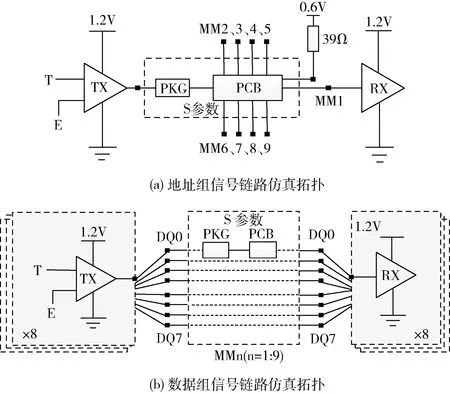

图2为DDR4总线链路仿真拓扑,图中TX表示地址组信号或数据组信号的发送端接口电路,RX表示地址组信号或数据组信号的接收端接口电路。T为发送端加载的激励波形,E为发送端接口电路使能控制电平,PKG和PCB分别代表封装段物理设计和印制板段物理设计,可以是物理结构参数也可以是表征传输特性的S参数。在地址组信号仿真中,PCB段的S参数体现了地址组信号的串推特性,信号通过封装管脚进入PCB后,可以在9个不同存储颗粒位置接收观测,同时采用片外端接方式上拉至0.6 V。数据信号链路仿真通常以存储颗粒的8个数据位为一组,每个数据位分别添加发送端电路接口模型和接收端电路接口模型。组内8个数据信号在发送端同时使能并加载一定速率的伪随机激励波型,在接收端观察组内串扰状态下的链路眼图质量。

图2 DDR4总线链路仿真拓扑

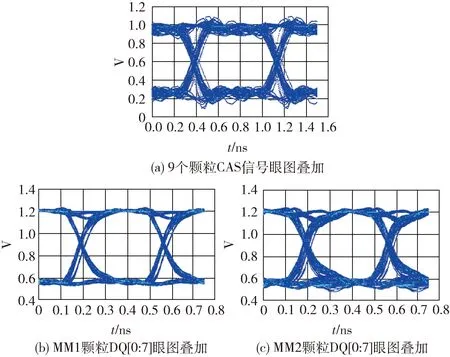

图3 串推结构设计总线仿真结果

2.2 码型分析仿真

传统的总线仿真结果显示设计裕量充足,但不足以化解该结构的设计风险。

结构中PCB板的厚度约为常规内存条的2.5倍,信号孔长度即是内存条信号孔的2.5倍。由于信号孔的寄生电感与信号孔长度强相关[16],如式(1)所示

(1)

式中:Lvia为孔寄生电感,单位nH。h为孔长,d为孔直径。孔长度增加,寄生电感随之增加。

相互靠近的有电流通过的电感器件,电流变化与电感之间互感的叠加作用,会有额外的电压产生,如式(2)所示

(2)

式中:L为信号孔之间的互感,i为通过信号孔的电流。

考虑到数据信号速率高,信号翻转时电流变化较大,地址组信号又是多负载多分支结构,而且地址组信号接收端没有片上端接,所以数据信号翻转对地址信号的影响是该结构面临的不确定因素,而传统总线仿真不能排除该不确定因素的影响。

为了充分化解设计风险,提出码型分析方法。选择离终端上拉电阻较远的MM1、MM2存储颗粒和地址组信号中空闲度相对小的CAS信号进行详细分析。

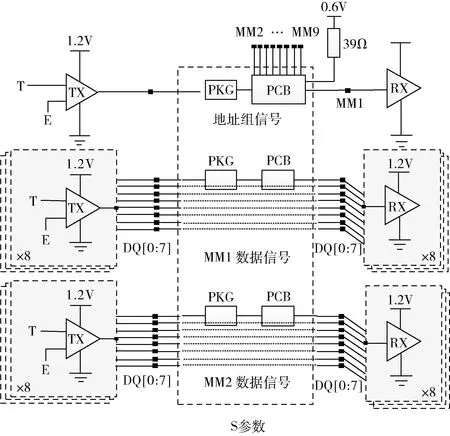

建立印制板两侧面对面贴装颗粒两组数据通道和地址信号物理关联链路,通过改变MM1颗粒和MM2颗粒数据信号链路的发送端激励波形表征不同速率和码型的数据信号翻转特性,采用如图4所示的码型分析链路拓扑,分析地址信号采样正确率是否受到影响。

图4 码型分析拓扑

2.3 静态码型仿真结果

静态码型是指数据信号无翻转电流,这时仿真链路中MM1和MM2的数据信号链路无激励波形加载,CAS仿真结果参考传统总线中的仿真结果。

根据DDR4存储颗粒数据手册要求,数据速率2666 Mbps~3200 Mbps对应的单端地址组信号的直流电平要求为:高电平大于VREF+65 mv,低电平小于VREF-65 mv;交流电平要求为:高电平大于VREF+90 mv,低电平小于VREF-90 mv。其中,VREF为参考电压,通常为0.6 V。在参考电压处的建立/保持时序根据速率不等,最小为145 ps~130 ps。

从图3(a)CAS信号9个颗粒位置的叠加眼图来看,在数据链路为静态码型情况下,信号内眼图的高、低电平距0.6 V有接近300 mv的电压差,即约210 mv的电平裕量,在参考电压0.6 V的时序宽度远大于290 ps。而实际工作时,每个颗粒的CAS信号采样电平和时序裕量是按照单颗粒的信号眼图来判别,而不是9个位置的叠加眼图,所以采样裕量大于等于眼图所示裕量。由分析可以推测:静态数据码型环境下的CAS信号采样裕量充足,无识别出错可能。

2.4 同向翻转码型仿真结果

同向翻转分为同向1010翻转和同向0101翻转。同向1010翻转是指MM1和MM2两个颗粒的两组数据信号同一时刻翻转方向一致,码型为“10101010”,数据速率为2666 Mbps。同向0101翻转对应数据翻转速率2666 Mbps不变,码型为“01010101”。

在CAS链路添加与静态码型链路相同的发送、接收端电路模型参数,两种同向翻转对应的9颗粒位置CAS信号叠加眼图如图5所示,图5(a)为同向1010翻转对应眼图,图5(b)为同向0101翻转对应眼图。

根据图5结果,在两组数据信号同向翻转时,CAS信号叠加眼图显示的电平窗口与静态码型相比,都有一定幅度的缩小。1010同向翻转对应的电平裕量略小,且交流输入低电平裕量接近于0。9个颗粒位置有实际采样电平裕量为零的可能,但不能确定与功能性信号识别出错强相关。

2.5 反向翻转码型仿真结果

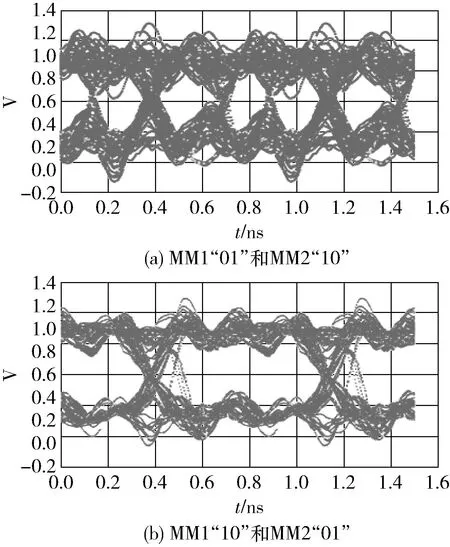

反向翻转是指MM1颗粒和MM2颗粒的数据信号在同一时刻翻转方向相反,也分两种情况进行分析。第一种情况:MM1颗粒数据信号码型“01010101”,MM2颗粒数据信号码型“10101010”,简称MM1“01”和MM2“10”,数据翻转速率2666 Mbps。第二种情况:数据翻转速率2666 Mbps不变,调换MM1和MM2两个颗粒的数据信号码型,MM1颗粒数据信号码型“10101010”,MM2颗粒数据组信号码型“01010101”,简称为MM1“10”和MM2“01”。

在CAS链路添加与静态码型链路相同的发送、接收端电路模型参数,两种反向翻转对应的9颗粒位置CAS信号叠加眼图如图6所示,图6(a)为MM1“01”和MM2“10”对应眼图,图6(b)为MM1“10”和MM2“01”对应眼图。

图6 反向翻转对应CAS信号叠加眼图

根据图6结果,MM1“01”和MM2“10”对应的CAS信号叠加眼图高低电平交叉,无论是电平还是时序都达不到手册要求,信号极有可能出现功能性识别错。MM1“10”和MM2“01”对应的CAS信号叠加眼图显示采样时序裕量充足,电平裕量略小。

进一步分析MM1“01”和MM2“10”对应的CAS信号可能出错的颗粒位置,图7为该反向翻转环境4个颗粒位置的CAS波形。

图7 MM1“01”和MM2“10”对应四颗粒CAS信号波形

从图7这4个颗粒位置CAS波形可以看出,MM1和MM3的CAS波形反射幅度大,高、低平稳电平处的反射方向都指向参考电平,且超出了接口电平要求,在这两个颗粒位置易出现信号识别错。MM4颗粒高电平在较宽的采样时序范围内也存在识别出错可能。

经分析,静态码型、两种同向翻转和两种反向翻转码型对CAS信号有不同程度影响。静态和同向翻转对CAS信号采样裕量影响较小,反向翻转会导致CAS波形产生明显畸变。反向翻转中的特定码型,即MM1“01010101”和MM2“10101010”,使得CAS信号在两个以上颗粒位置出现高电平和低电平识别出错。也就是说,当印制板上、下表面对贴的两个颗粒的数据信号反向翻转时,命令/地址信号会在多个颗粒位置出现电平识别出错。

从布局布线设计来看,CAS信号线与MM1和MM2数据信号线处于不同信号层,同层信号线间串扰可能性小。在纵向上,两类信号都经过了板厚较大的通孔,结合前文对孔间干扰的分析,减小孔间耦合成为优化设计的方向。

3 优化设计及仿真

3.1 双盲折叠串推结构

从优化通孔串扰的目的出发,设计如图8所示的折叠串推结构。该结构与图1的串推结构相比,地址组信号串推顺序有了明显变化。地址组信号从处理器出发,依次经过MM1至MM4、MM9校验颗粒、MM5至MM8,最后到达端接器件R。除此之外,PCB表面正、反贴颗粒的引盘孔在PCB厚度方向上无重叠。该结构增加了上下表面颗粒信号引盘孔的物理隔离距离,并且不改变原有的布局密度以及布线距离。

图8 折叠串推结构

常规PCB叠层工艺无法实现对贴颗粒的引盘孔阵列物理隔离,因此提出一种双面盲PCB叠层结构,两种叠层设计对比如图9所示。

图9 常规PCB工艺VS上面盲PCB工艺

印制板通常由基材、半固化片、表面铜箔组成。基材如图9中Core所示,是材料厂商提供的两面具有一定光滑度的铜箔和夹心介质材料组合体;半固化片如图中PP所示,是基材间填充的介质材料。常规印制板工艺中,表面铜箔位于PCB的两个表面。由布线和供电需求确定基材、半固化片的规格和数量后,一次层压成型再进行整板钻孔处理是常规印制板工艺特点。

在双面盲PCB叠层中,除了印制板表面铜箔外,在基材中间也有两层铜箔,这两层铜箔在虚线框的区域内分别起到了下表面铜箔和上表面铜箔的作用。双面盲PCB叠层工艺共有3次层压,第一次和第二次分别对两个虚线框内的Core、PP和表面铜箔进行层压,第三次对从上至下整个区域进行层压。盲孔的实现依靠前两次层压之后的钻孔工艺,对于虚线框内的结构,第一、二次层压之后的钻孔相当于常规工艺,第三次层压之后,之前的通孔结构成为盲孔。整板的通孔设计需求在第三次层压之后钻孔实现,不受前两次层压影响。

双面盲结构中的基材数量可以根据布线需求进行调整,由于不受激光盲孔钻孔深度的限制,可以实现多层盲孔互连。两个虚线框中间区域基材,可以用作电源供电层,电源层的基材数量和厚度不影响上盲和下盲区域的钻孔厚径比。

根据折叠串推结构和双面盲叠层进行设计优化,盲孔孔径可以由0.25 mm减小至0.15 mm,减小幅度40%,得益于钻孔厚度的大幅减小。

针对优化设计版本进行链路仿真分析,优化结构中的MM2和MM8颗粒分布位于印制板的上、下表面,Pin坐标重合,因此选择MM2和MM8颗粒的数据信号和地址信号CAS的进行码型干扰分析。

3.2 2666 Mbps仿真结果

MM2和MM8数据信号在2666 Mbps速率下同向翻转时,CAS信号叠加眼图如图10所示。图10(a)为同向1010翻转对应眼图,图10(b)为同向0101翻转对应眼图。

图10 2666 Mbps同向翻转对应CAS叠加眼图

MM2和MM8数据信号在2666 Mbps速率下反向翻转时,CAS信号叠加眼图如图11所示。图11(a)为MM2“01”和MM8“10”对应眼图,图11(b)为MM2“10”和MM8“01”对应眼图。

图11 2666 Mbps反向翻转对应CAS叠加眼图

优化设计后同向翻转和反向翻转叠加眼图与优化前相比,电平裕量有了显著提高,采样电平和时序裕量充足,信号功能性识别出错概率极小。

3.3 3000 Mbps仿真结果

把MM2和MM8的数据信号速率从2666 Mbps提升至3000 Mbps,观察CAS叠加眼图。两种同向翻转和反向翻转对应的CAS叠加眼图如图12所示。

图12 3000 Mbps同向和反向翻转对应CAS叠加眼图

根据图12的眼图结果,即使数据速率大幅提升,CAS眼图的电平裕量和时序裕量仍然充足,信号功能性识别出错概率小。双面盲折叠串推结构相比优化前的通孔串推结构,在高速率数据码型干扰环境下CAS信号质量大幅提升,识别出错问题得以解决。另外,优化结构中的数据信号由于孔径变小,孔分支长度减小,信号质量也会得到一定程度的改善。

4 应用测试

优化后的双面盲折叠串推结构应用于神威E级原型机运算板,在处理器的功能调试和运算板的工程测试中,DDR4信号传输性能和访存功能得到全面的测试验证。

DDR4测试中,包括读/写训练测试、课题访存功能测试和信号波形测试。读/写训练测试是指在与读/写速率适配的时序参数条件下,处理器与存储颗粒之前通过一系列训练步骤,建立可存可取的读操作与写操作运行环境。训练步骤包括初始化、读使能、数据选通与时钟边沿对齐、组内数据去偏斜等。课题访存功能测试与memtest原理一致,通过针对颗粒存储空间的大量读/写操作,统计内存中可能的出错位置及操作项,测试内存工作的稳定性。课题功能包括地址遍历、连读连写、不同码型数据的读写测试等。信号波形测试,即选择少量待测信号,焊接测试夹具,连接实时示波器进行实时波形捕获,确认信号速率和波形质量。由于时钟信号可以直观反映数据速率,同一颗粒的数据选通信号和数据信号波形叠加可以识别捕获波形对应操作是读还是写,所以DDR4波形测试中这3种信号较常见。

存储颗粒标称速率为2666 Mbps,在标称速率下,系统512个处理器所有DDR4存储互连通路中读/写训练全部通过,重复运行各类内存稳定性测试程序,包括长时间拷机课题,无报错。数据速率提升至3000 Mbps时,结果一致,读/写训练全部通过,课题运行仍然无报错。

3000 Mbps运行时读/写测试波形如图13所示。这里读/写操作的数据选通信号波形都采用两个时钟周期的导沿模式,导沿编码为1110,由于数据选通信号是差分信号,导沿之后的采样区间摆幅是数据信号的两倍。两幅图中,导沿之后摆幅较大的是数据选通信号波形,无导沿且摆幅较小的是数据信号波形。

图13 3000 Mbps读、写数据和时钟波形

图13(a)中,数据选通信号与数据信号在高低电平切换处无相位差,为读操作波形。图13(b)中,数据选通信号与数据信号在高地电平切换处存在半个数据位宽的相位差,为写操作波形。两图中,数据选通信号和数据信号叠加波形下方是周期性的时钟信号波形,时钟频率1.50 GHz,可知数据速率为3000 Mbps。从读、写操作数据波形来看,数据信号在超频条件下传输质量良好。

5 结束语

本文从多路DDR4存储颗粒嵌入式工程应用出发,设计了一种高密度DDR4串推结构,提出基于不同激励码型的仿真分析方法,分析该结构中数据组信号特定翻转码型影响地址组信号识别问题,进一步优化设计了基于双面盲叠层结构的折叠串推结构,有效解决了该问题。实测波形显示,该结构超频条件下的DDR4波形质量良好,并且具有较高的系统访存功稳定性。目前已推广应用于神威E级原型机等多台套大型计算装备,技术效益良好。