基于FPGA的千兆以太网MAC控制器的设计

杨 武,张 俊,苏国旺,丁旭然,李 秋

(中南大学自动化学院,湖南长沙 410083)

0 引言

以太网是目前局域网最常见的通信协议标准[1],具有网络灵活、兼容性高等优点。嵌入式系统逐渐走向网络化,对以太网接入的需求逐渐增大[2]。MAC(介质访问控制)层属于OSI参考模型的数据链路层,主要实现数据帧构建、差错检验、传输控制和接口转换等功能[3],是实现以太网技术的关键之一。

许多学者设计了功能、接口不一的MAC控制器以提供以太网传输功能。霍卫涛等[4]提出基于AMBA协议的双通道以太网MAC,并使用RGMII接口,以减少管脚数目。曾明[5]提出基于DMA的千兆以太网MAC,采用基于描述符的DMA结构实现数据的高速传输,兼容十兆、百兆传输速率。文丰等[6]提出仅支持千兆速率的以太网MAC软核,相较于兼容百兆、十兆的MAC控制器,具有更强的针对性和专一性。包海燕等[7]提出GMII接口单元,可完成MAC层帧数据的封装、解封及对媒体的访问管理。

本文设计了基于FPGA的MAC控制器,在满足千兆以太网MAC协议所要求功能及性能的同时,尽可能降低逻辑资源使用量,并提高系统可靠性。

1 MAC层协议

MAC控制器工作在半双工模式时,通过CSMA/CD(载波监听多路访问/碰撞检测)协议来控制对共享介质的访问,而在全双工模式,只需保证相邻两帧之间的帧间间隔不小于最小帧间间隔。IEEE 802.3规定的MAC帧格式如图1所示,包括前导码、帧起始定界符、目的地址、源地址、长度/类型字段、MAC客户数据、填充、帧校验(FCS)和扩展字段。

图1 IEEE 802.3规定MAC帧格式

2 千兆以太网MAC控制器的设计

本文提出的MAC控制器的总体架构如图2所示,MAC控制器通过GMII接口和物理层连接。主要模块包括主机接口模块、发送/接收缓存、发送发起模块、流量控制模块、发送控制器模块、接收控制器模块、接收保存模块、状态检测模块和MII管理模块。

图2 MAC控制器整体架构

主机接口模块实现地址译码,提供对MAC控制器内部寄存器、发送缓存和接收缓存的访问。状态检测模块采集发送和接收过程中的状态信息,并同步到主机接口模块。发送和接收缓存各包括一个改进型异步FIFO(位宽为32)和一个普通异步FIFO,分别用于存储帧数据和帧长度(字节数)。发送发起模块负责将帧从发送缓存读出,并将其转换成字节形式,提供给流量控制模块。流量控制模块实现控制帧的响应和发送,以支持全双工流量控制。发送控制器模块对帧进行封装并发送给PHY芯片。接收控制器模块完成帧的识别,并将解封装后的帧传递给上层模块。接收保存模块将帧转换为32位形式,写入接收缓存。MII管理模块实现对PHY芯片内部寄存器的访问。

2.1 改进型异步FIFO设计

发送和接收缓存都由存储帧数据的改进型异步FIFO和存储数据长度的帧长度FIFO模块组成。以发送缓存为例,存储帧数据的缓存需要完成帧数据从主机时钟域到发送时钟域的同步。仅考虑这一点时,可使用异步FIFO,但是发送帧时可能因冲突导致需要重发,也可能因为某些错误,导致放弃当前帧的发送,直接跳到下一帧,而异步FIFO不能满足这两点要求。为此,本文在异步FIFO的基础上进行改进,设计出读端口可清除及重读式异步FIFO。在异步FIFO的读端口增加帧重读和帧清除信号。帧重读信号有效时,读指针回到当前帧的起始位置。帧清除信号有效时,读指针跳到下一帧的起始位置。读端口可清除及重读式异步FIFO电路结构如图3所示。

图3 读端口可清除及重读式异步FIFO结构

除读写指针外,增加了指向当前帧起始地址的基地址指针,3个指针的最高位为翻转标志,其余位用于指示地址。进行读写操作时读写指针加一,帧重读信号有效时,读指针回到基地址,帧清除信号有效时,读指针和基地址指针变为基地址指针加帧长度。将读指针和写指针比较得到空信号,将写指针和基地址指针比较得到满信号。

由于写指针、读指针及基地址指针处于不同时钟域,所以比较前要进行跨时钟域的同步操作。写指针只会顺序变化,所以采用格雷码并打两拍的方法。当读指针格雷码和写指针格雷码打两拍后的结果相同时空信号有效。基地址指针会跳变,不适合使用格雷码,因此采用握手机制进行同步。实现方法为:当进行帧清除操作时,基地址指针变为基地址指针加帧长度,同时产生请求信号。在写时钟域对请求信号打两拍,取上升沿,得到同步后的请求信号。当同步后的请求信号有效时,在写时钟域锁存基地址指针(即得到同步后的基地址指针),并产生应答信号。在读时钟域对应答信号打两拍,取上升沿得到同步后的应答信号,读时钟域检测到同步后的应答信号有效时,清除请求信号。写时钟域检测到请求信号打两拍的结果无效时,清除应答信号。当写指针和同步后的基地址指针的最高位不同,剩余位相同时,满信号有效。

存储接收帧数据的缓存需要完成帧数据从接收时钟域到主机时钟域的跨时钟域同步操作,且在地址不匹配、CRC校验错误等情况下应当丢弃当前帧。因此采用类似的方法,在异步FIFO的写端口增加帧清除和帧完成信号,设计出写端口可清除式异步FIFO。定义读写指针和指向当前写的帧起始地址的基地址指针,帧清除信号有效时写指针回到基地址,清除写入的帧数据,帧完成信号有效时基地址指针更新为写指针的值,代表一帧数据正式写入。将写指针和读指针比较得到满信号,将读指针和基地址指针比较得到空信号。比较前对读指针和基地址指针进行跨时钟域的同步处理,读指针的同步使用格雷码并打两拍的方式实现,基地址的同步使用握手机制实现。当读指针格雷码打两拍后的结果和写指针的格雷码最高两位不同,剩余位相同时,满信号有效。当同步后的基地址指针和读指针相同时,空信号有效。

2.2 发送发起模块

发送帧时,发送发起模块按照发送帧长度FIFO提供的长度,从读端口可清除及重读式异步FIFO读取相应长度的帧数据,将其从32位形式转换为字节形式,并生成相应的控制信号,提供给流量控制模块。流量控制模块同意发送发起模块的发送请求后,再将数据和控制信号提供给发送控制模块。发送发起模块还需要根据发送控制器模块返回的发送结果对发送缓存中的帧进行管理。当帧发送完成或放弃帧时,发送发起模块向读端口可清除及重读式异步FIFO输出帧清除信号。当帧需要重发时,发送发起模块向读端口可清除及重读式异步FIFO输出帧重读信号。

2.3 接收保存模块

接收保存模块负责将接收控制器模块输出的解封装后的字节形式的帧数据拼接成32位形式,然后将帧数据和数据长度写入接收缓存。当接收帧没有错误时,接收保存模块将全部帧数据写入写端口可清除式异步FIFO之后,向写端口可清除式异步FIFO输出帧完成信号,并将数据长度写入接收帧长度FIFO。当出现地址不匹配、帧校验错误等情况时,接收保存模块停止写入帧数据,并向写端口可清除式异步FIFO输出帧清除信号,清除已写入数据。

2.4 流量控制模块

流量控制模块实现全双工模式下的流量控制,支持控制帧的发送、识别和响应,内部结构如图4所示。

图4 流量控制模块结构框图

流量控制模块对数据帧和控制帧的发送请求进行仲裁,然后选通相应数据通路,将数据帧或控制帧提供给发送控制器模块进行封装和发送,控制帧拥有更高的发送优先级。控制帧生成模块负责产生控制帧的帧数据和相应控制信号。控制帧识别模块对接收控制器模块提供的接收帧目的MAC地址、长度/类型字段、操作码等字段进行检查,判断其是否为控制帧。确定接收到控制帧时,按照控制帧中暂停时间参数的要求,在相应时间内阻断数据帧的发送。

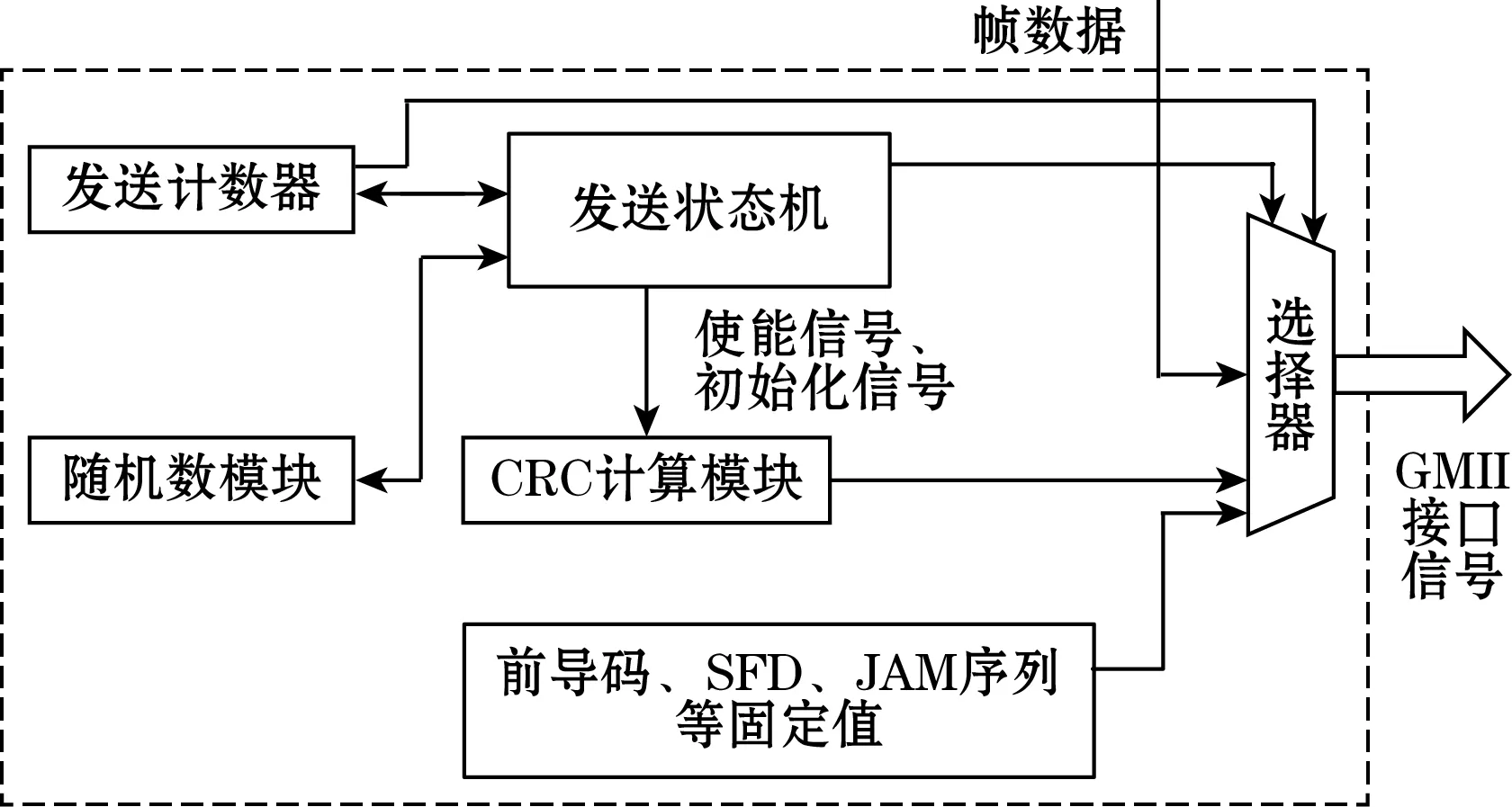

2.5 发送控制器模块

发送控制器模块从流量控制模块接收字节形式的帧数据,按照设置为其添加前导码、帧起始定界符、填充、FCS和扩展等字段,通过GMII接口发送给物理层,并实现CSMA/CD协议。发送帧时,可能成功发送,可能会因冲突导致需要重发,也可能因迟冲突、重发次数超过限制等错误导致需要放弃当前帧的发送。发生这几种情况时,发送控制器模块需要向发送发起模块提供相应信号,告知当前帧的发送结果。发送控制器模块的内部结构如图5所示。

图5 发送控制器模块结构框图

在半双工模式下,发送状态机模块根据CSMA/CD协议的要求执行载波检测、冲突强化、冲突退避、载波扩展、帧突发等操作,并根据MAC帧格式添加封装。在全双工模式下,发送状态机模块确保两帧之间的间隔满足96 bit的最小帧间间隔要求,并进行MAC层封装。发送状态机模块控制整个发送的流程,根据其状态可确定当前发送的字段。发送计数器模块提供各项计数,为发送状态机模块的状态转换等提供参考。随机数模块使用线性反馈移位寄存器提供冲突退避时所需要的退避随机数。为降低系统对时钟速率的要求,CRC计算模块使用8位并行CRC算法计算CRC-32码[8],将其按位取反后得到帧校验字段。

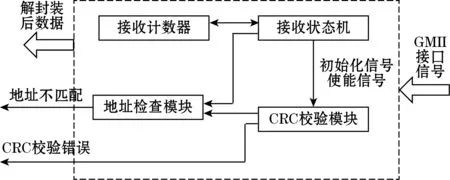

2.6 接收控制器模块

接收控制器模块通过GMII接口从物理层接收帧数据,进行帧的识别、解封装和有效性检查,将解封装后的帧数据向上层模块传递,其内部结构如图6所示。

图6 接收控制器模块结构框图

接收状态机模块根据CSMA/CD协议及MAC帧格式识别接收内容,进行最小帧间间隔等检查,判断是否接收到帧,并区分接收帧的各字段。接收计数器模块提供各种计数,为其他模块提供参考。地址检查模块进行地址过滤,对目的MAC地址进行单播、多播和广播地址检查,判断是否接收当前帧。同样,CRC校验模块使用8位并行CRC算法对接收帧进行CRC校验,以降低系统对时钟速率的要求。当接收帧出现地址不匹配、CRC校验错误、长度/类型字段描述与实际不符等情况时,接收控制器模块输出相应的状态信号。

2.7 MII管理模块

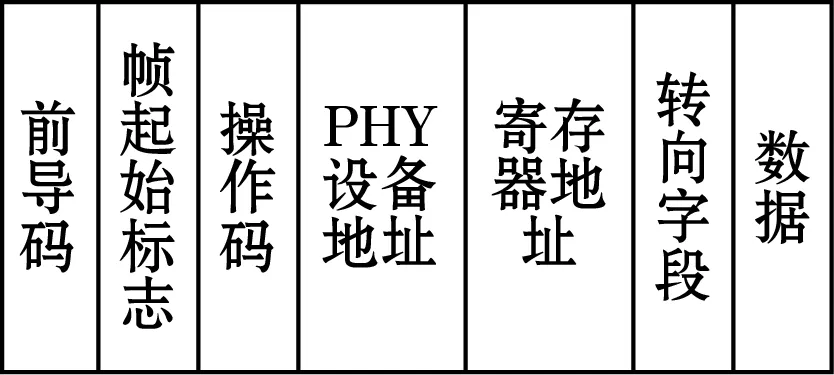

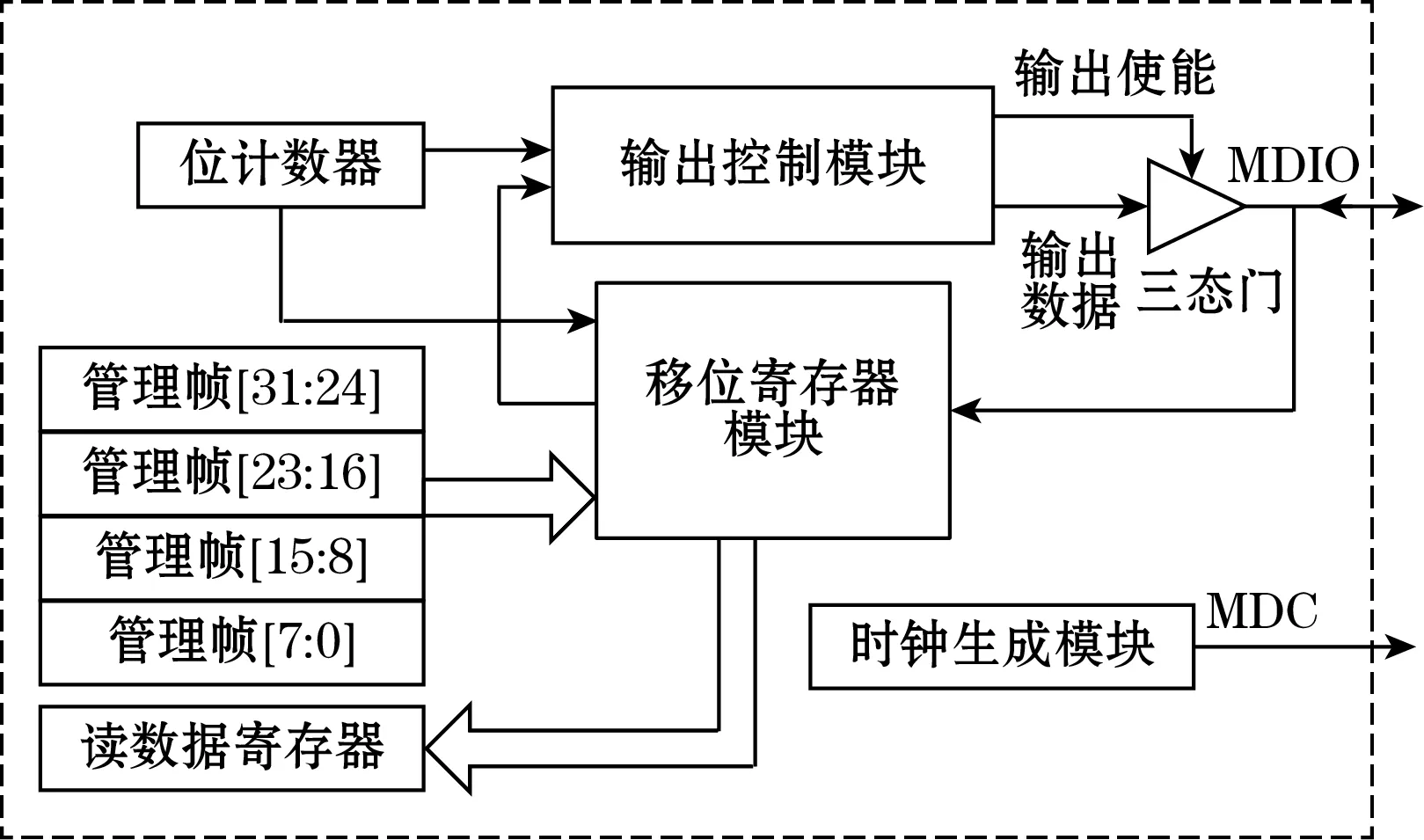

MII管理模块通过管理接口向PHY芯片发送管理帧,访问PHY芯片内部的寄存器,对PHY芯片进行配置或读取其状态信息。管理接口包括MDC时钟信号和MDIO串行双向数据信号,管理帧结构如图7所示。

图7 管理帧结构

MII管理模块内部结构如图8所示。时钟生成模块对主机时钟进行分频,得到MDC时钟。输出控制模块控制三态门的输出数据和输出使能信号,实现MDIO串行双向数据接口。前导码由输出控制模块提供,其余帧内容由移位寄存器模块提供。开始发送管理帧时启动位计数器,通过位计数器可确定当前发送的位。移位寄存器模块中包含一个8位的移位寄存器,从发送帧起始标志开始,每隔8个MDC时钟周期将管理帧的下一字节数据更新到移位寄存器模块中,中间将数据移位输出,提供给输出控制模块。移位寄存器模块还负责在读操作时将串行读数据并行化,存入读数据寄存器,供主机接口模块读取。

图8 MII管理模块结构框图

3 FPGA系统验证

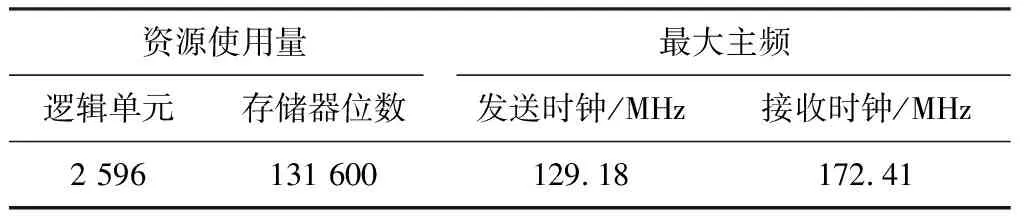

MAC控制器采用Verilog HDL硬件描述语言进行RTL代码设计,并利用ModelSIM软件完成功能仿真验证。在Qaurtus上建立工程,选择FPGA器件型号为EP4CE115F29C7,得到MAC控制器综合结果和最大主频如表1所示。MAC控制器的逻辑资源使用量较少,存储器资源使用量由缓存大小决定,可调整。发送及接收时钟均超过125 MHz,满足GMII接口要求。

表1 综合结果及最大主频

采用DE2-115开发板搭建硬件测试平台对设计的MAC控制器进行测试,测试平台如图9所示,开发板包含物理层芯片88E1111。

图9 硬件测试平台

由于开发板仅支持RGMII接口,所以需要在物理层芯片和MAC控制器之间增加一个接口转换模块。接收-发送模块负责对MAC控制器进行相应的配置,并在MAC控制器接收到有效帧时,将接收帧读出,更改帧的目的MAC、目的IP地址改为PC机地址,源MAC和源IP地址改为FPGA地址,然后写回MAC控制器,让MAC控制器将帧发回给PC机。

在PC机上运行网络调试助手,发送帧给FPGA,用wireshark抓包软件抓取发送和接收帧,结果如图10和图11所示。PC机发送和接收的帧除了源地址和目的地址相反之外,其他内容一致,说明MAC控制器工作正常。

图10 PC机发送抓包结果

图11 PC机接收抓包结果

4 结束语

本文设计的千兆以太网MAC控制器可工作在千兆传输速率下,配合物理层芯片能够完成以太网数据的收发。此外,MAC控制器支持控制帧的收发,实现了流量控制,且可通过管理接口对PHY芯片进行配置或读取其状态信息。设计中提出2种改进型异步FIFO,解决冲突帧的重传及错误帧的丢弃问题。