基于时间序列分析的高速PCB 板信号完整性检测方法

高 菲,吴 屏,胡秋琦

(哈尔滨工业大学(深圳)实验与创新实践教育中心,广东深圳 518000)

随着信息技术的飞速发展,高速PCB 板信号传输系统被越来越多地应用在通信、计算机等领域。在信号传输和处理速度日益提高的今天,保证PCB板信号传输完整性显得尤为重要。随着IC 制造技术的不断进步和创新,各种电子元器件之间在功能上更加兼容,但同时其超高的信号传输速度也导致高速器件在实际应用中容易出现信号缺失的问题[1-2]。

为了解决这一问题,该文基于时间序列分析提出了新的高速PCB 板信号完整性检测方法。在分析数据信号和高速信号传输时序要求的基础上,采用数据采集方法采集影响数据信号传输完整性参数,对采集的参数进行扫描,通过示波器仿真得到PCB板信号完整性的检测结果。

1 高速PCB板信号数据分析

由于信号在低频传输时的时差变化较大,因此可以忽略计算精度的影响,在PCB 板上模拟出传输导线,得到理想的延时计算结果。在分析时,将导线信号输出延时与驱动器输出端延时合并,使信号传输线上任意时间任意位置的信号波动曲线保持一致[3]。由于在高频电路板各传输线的传输过程中设计了一些电阻、电容和电导等器件,因此高频电路板的导通模型由理想导通模型改为分布网络模型[4-5]。

传输线的信号传输特征可以用定向阻抗Z0表示,传输延迟用Tpd表示。通过计算传输线的单位长度L和单位传输线上的电容C,可以得到传输线的定向阻抗Z0的表达式如式(1)所示:

由于在高频情况下,导线的信号输出延迟不能合并到驱动器的输出端进行统一建模处理,因此,在高频情况下,传输线路上任意位置的信号波动具有线性差异,这就是高频情况下的线效。相邻两回路之间通过相互作用的电场来产生电容,电容两回路之间的距离随导体距离的增加而减小。分析相容系数,通过相容系数表征两个电路中电容的变化情况[6-7]。

当电路A 中的电压发生变化时,会产生互容效应,向电路B 输入一个电流逆差IM,通过对电路间的电容值CM和电路A 上的电压变化率dV/dt进行计算,可得IM的表达式为:

从式(2)可以看出,电流逆差IM受两电路间互容值的影响,在电路电压变化率不变的情况下,互容值越大,互容作用越明显。在互容值不变的情况下,电路电压变化率越小,电流逆差越小,互容作用越弱。在两个电路中,任意一个电流回路都伴随着磁场的产生,并影响着另一个电流回路,作用力随着电流回路之间距离的增加而减弱,这种作用力就是互感作用力,一个回路的电流产生一个磁场,而该磁场会影响第二个回路[8-9]。

当电路A 中的电流发生变化时,由于互感作用,电路A 会向电路B 输入一个电压逆差VM,通过对电路间的互感值LM和电路A 上的电流变化率dI/dt进行计算,可以得出VM的表达式为:

根据式(3)可知,当LM保持不变时,电路A 中电流变化率越大,电路之间的电压逆差也越大,互感作用越明显;电流变化率不变时,电路互感值越大,互感作用越明显[10-11]。高频效应会影响信号传输的完整性,所以需要对其进行检测[12]。

2 信号完整性检测

将时间序列分析和信号完整性检测两者有机结合,通过对PCB 板输出的数据和信号进行采集,并对其进行时间序列设计得出不等式,以便进行PCB 板信号完整性检测[13-14]。

对于源同步电路,首先将电路A 和电路B 的数据通过Spt 系统输出并传输至串并转换器MCIOE445,通过驱动器发出锁存信号对数据进行封锁。源同步数据传输示意图如图1 所示。

图1 源同步数据传输示意图

锁定信号STB 的末端靠近数据,可以高效地接收数据,这样有利于接收端有效地接收数据。在STB信号传输过程中,由于传输线的内部阻抗会造成一定的时延,因此要把数据传输线的长度控制在一定范围内,以最大限度地保证信号传输的及时性[15]。源同步数据传输系统的时间序列关系如图2 所示。

图2 源同步数据传输系统的时间序列关系

根据图2可以建立时间序列表达式,如式(4)所示:

其中,TSSU为源数据输出的最短时间,TSH为输出数据的有效保留时间,TDSU为数据传输到终端时的有效时间,TDH为接收数据保留的有效时间。

为了保证数据能够完整地被接收端接收,应该满足数据传输到终端的有效时间TDSU和接收数据保留有效时间TDH大于源数据输出的最短时间TSSU以及输出数据有效保留时间TSH。保证时间余量充足,以确保系统正常稳定运行。

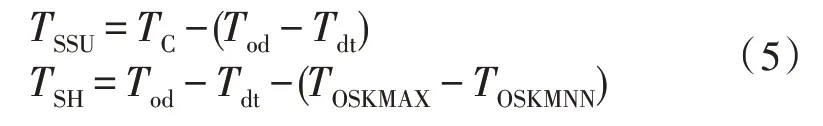

当对频率为600 MHz 的系统进行数据采集时,经过二分频后实际的工作频率仅有300 MHz,所以必须对源数据输出的最短时间TSSU和输出数据有效保留时间TSH进行计算。此时信号转换周期TC为3.3 ns,通过对采样周期起始时间到信号转换结束时间Tdt、采样周期起始时刻到数据传输终止的时间差Tod、数据传输延迟时间TOSKMAX进行计算,得出源TSSU和TSH的表达式如下:

代入参数后计算出TSSU=2.68 ns,TSH=0.14 ns,可以看出TSSU和TSH占比不够均衡,不符合源同步信号传输的基本要求,重新计算后得出TSSU=1.18 ns,TSH=1.63 ns。符合源同步传输的要求[16]。

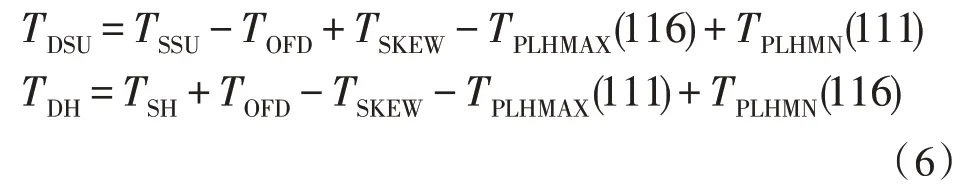

电路A 和电路B 的输出数据和转换结束信号经过差分驱动MCIOE116 输出,增加了数据延迟时间,所以在计算锁存信号STB 时必须考虑差分驱动的内部时间延迟。根据配套数据手册可知,芯片内部低频传输延时时间为TOFD,高频传输延时时间为TSKEW,且两频率下延时时间相同。将TSKEW作为常数。时间序列关系式可以表示为:

为了保证串并转换器MCIOE445 能够有效地锁存数据,需要满足数据输出最小时间为0.2 ns,信号输出有效保留时间为0.43 ns。根据时间序列要求可以得到TDSU与TDH的时间序列表达式如式(7)所示:

在高速信号传输中数据采集速率为600 Mbps,数据通过两个分路输出时,速率变为每路300 Mbps,对信号传输通道的网络结构做预先布局设计分析,以保证信号传输过程中不会因为网络结构问题而降低信号的完整性。采用线性模型对IBIS 模型进行模拟,以便在软件中进行信号完整性检测。将SPT7610的信号传输驱动前端作为线性结构,根据驱动时间和驱动效果模拟建立输出信号的特征模型。为了减少模型模拟结果与实际结果的误差,应尽量缩短信号传输各部件间的距离。差分驱动器MCIOE116 到串并转换器MCIOE445 锁存通道间的信号传输对整个信号传输完整性影响十分重要,所以要对这部分的完整性进行重点分析。其连接数据通道模型如图3所示。

图3 连接数据通道模型

对数据通道的单调性、噪声极限、低压过冲、高压过冲、常态延迟和转换延迟进行测量。由于信号的传输前端与接收前端不具有同时性,所以要对其进行分别测量。

对以上测量结果进行参数扫描,对参数变化下的信号完整性变化进行模拟,并对模拟结果进行分析对比,筛选出满足完整性和时间序列要求的参数极值。假设各元件内部阻抗与特征阻抗误差在±10%以内,则标准阻抗为40 Ω的元件在误差范围内的阻抗为36~44 Ω。采用TYIPCAL 类型数据来反映所需要的情况。分别对不同传输线长度的传输结果进行分析,得到波形图,各个参数变化的情况如表1 所示。

表1 波形图参数变化

通过观察波形图的信号完整性参数,如单调性、噪声极限、低压过冲、高压过冲、常态延迟和转换延迟,可以清楚地看到数据通道的信号是否满足完整性要求。

3 实验研究

为了验证该文提出的基于时间序列分析的高速PCB 板信号完整性检测方法的有效性,将其与传统检测方法进行实验对比。

对数据传输信号检测时间进行分析验证,在600 MHz 的高频工作状态下,采用高速数据包High Speed Test Packet 对信号的完整性进行验证。在待测平台发出待测试数据,可在测试点得到数据包对应的波形图,再对波形图进行数据提取,与原始数据包进行对比,得出数据包的传输时间长度,进而计算出信号的数据传输速率为490.569 Mbps。

根据高速PCB 板的信号传输规范,高速数据信号传输速率应该在467.76~520.24 Mbps 之间,所以该检测方法在检测时间上满足设计要求。

通常PCB 板在信号传输过程中会产生500 mA的负载。通过模拟5个500 mA的负载,并将其同时接入,以测试VBUS 电压的最大衰落。用示波器对数据传输线的波形进行捕获。示波器捕获波形如图4所示。

图4 完整性捕获波形图

从图4 中可以看出VBUS 电压从5.275 V 衰落到4.987 V,其差值为288 mV。根据规范,差值应该小于330 mV,表明该方法能够满足完整性检测要求。

4 结束语

该文主要讨论了高速PCB 板信号传输系统中的信号完整性检测方法,通过实验证明了该方法在检测时间和检测完整性上都具有优势,对信号完整性检测有一定的促进意义。