TFT-LCD中电容对公共电压的影响

邱鑫茂, 王巧妮, 刘娜妮, 刘 耀, 王宝强, 谢 鑫, 涂婷婷

(福州京东方光电科技有限公司,福建 福州350300)

1 引 言

薄膜晶体管有源矩阵液晶显示(TFT-AMLCD)技术具有庞大的产业规模。随着显示技术的发展以及市场差异化需求,大尺寸、高PPI、窄边框、高刷新率是目前高端显示屏的特征[1-3]。高端显示屏需求者对残像、残影的容忍度几乎为零。

目前多数残像评价是采用“黑白棋盘格点灯后在灰阶画面观察判定等级”进行的。残像的形成与棋盘格画面所需的驱动电压直接相关,棋盘格画面产生的残像一定是棋盘格形状。

显示屏进入市场前,开发阶段调试是重要环节。调研发现[4-6]:常见的极性反转驱动、像素预充电和面板内公共电压(Common Voltage,VCom)补偿调整无法完全消除残像。公共电压作为像素电压的基准电压,分布于整个面板,像素的亮暗取决于像素电压和公共电压的压差。公共电压通常采用直流驱动的方式,公共电压的稳定是确保显示画质的重要因素[7]。

棋盘格线残像产生原因主要为:黑白格边界处像素充电时间不足和公共电压负向波动,导致像素电压相对于公共电压正负帧不对称,使液晶产生极化,切换到灰阶画面表现为残像。

目前画面数据驱动IC输出的数据电压(Data Voltage,VData)对公共电压的影响本身未得到深入研究。数据电压和公共电压各自相连的金属导线与薄膜导电材料氧化铟锡(In2O3∶SnO2,ITO)形成电容(CDC)。本文分析了数据电压通过CDC耦合公共电压产生畸变(Distortion)的过程、产生线残像原因和提供畸变弱化方法,为线残像的改善提供了分析方法和理论依据。

2 数据电压与公共电压间电容

2.1 电容CDC分析模型

本文分析面板在开发阶段的评价过程中出现线残像问题,希望从CDC的角度进行分析研究。在产品实物制作前的CDC电容值是模拟得到的,且为固定值;采用平板电容简单模型计算(C=εrε0S/r),其电容的面积(数据电压与公共电压金属导线交叠面积)、电容间介质介电常数和距离为固定值。通过分析研究,面板工作状态的CDC有效电容其实受到TFT开关、栅极电压、公共电压及数据电压影响。

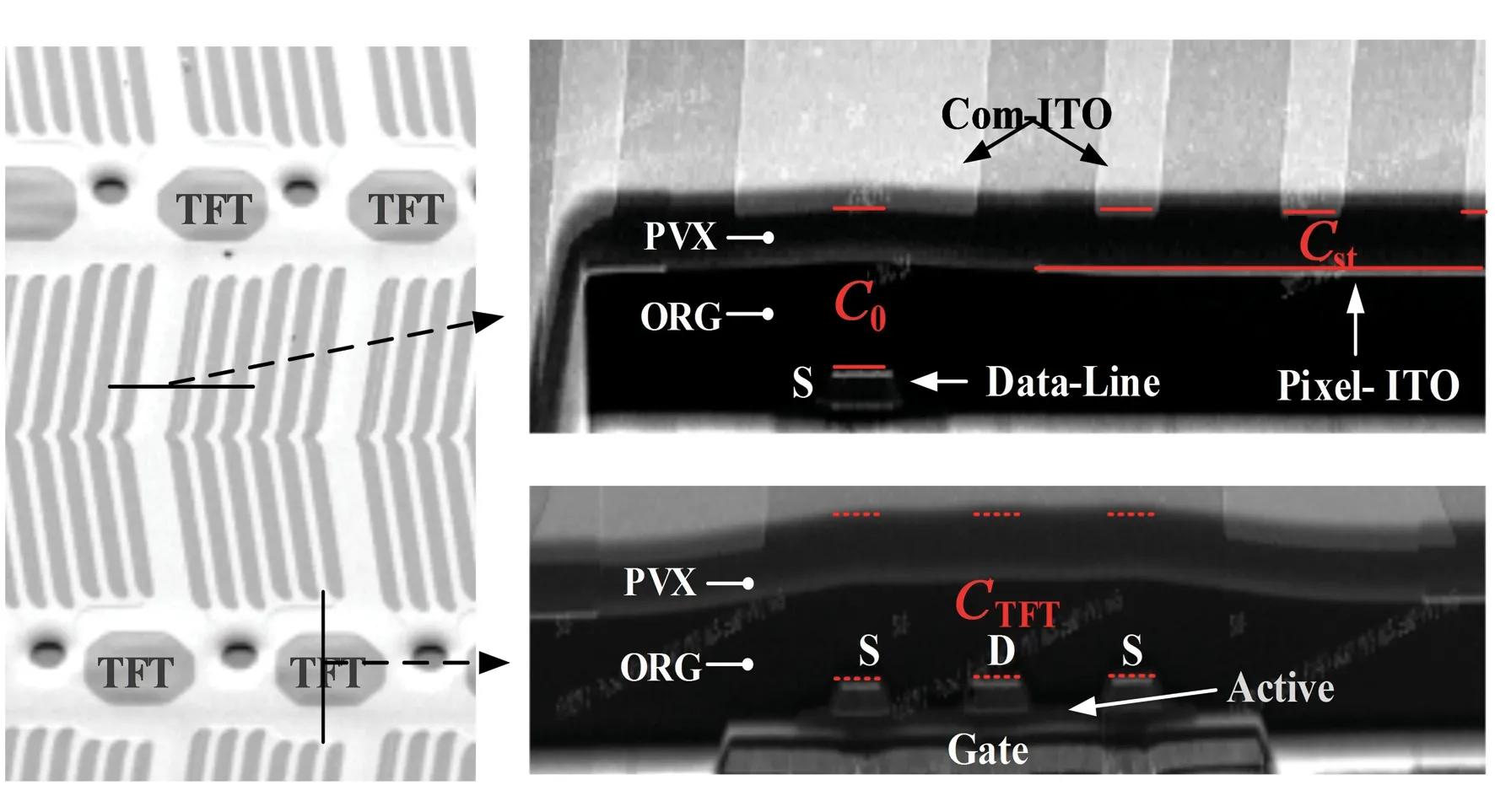

为更好地理解电容CDC组成,现对其阵列(Array)形貌描述如图1所示。该图为聚焦离子束(FIB)设备扫描得到表面和截面。从表面图可以看到公共电压电极ITO薄膜为条状分布。从截面图可以看到数据电压导线(Data-Line)和像素电极ITO薄膜(Pixel-ITO)位于公共电极ITO 薄膜(Com-ITO)下方。Data-Line与Com-ITO形成电容(C0),介质为SiNx绝缘层(PVX)和有机膜(ORG)。Pixel-ITO与条状Com-ITO形成驱动液晶偏转的存储电容(Cst),介质为PVX。TFT起Data-Line与Pixel-ITO之间连接开关的作用,对于此样品,TFT上方无COM-ITO。若TFT上方存在Com-ITO,Com-ITO与TFT的漏极(Drain)及有源层(Active)将形成电容(CTFT),介质为PVX+ORG。Com-ITO与底层栅极(Gate)对TFT形成“上下双栅极结构”,TFT工作状态同时受到双栅影响,同时CTFT也随双栅电压变化而变化。对于非有机膜设计方案,C0和CTFT的介质仅为SiNx绝缘层。

图1 阵列设计及电容CDC构成Fig.1 Diagram of array design and CDC composed

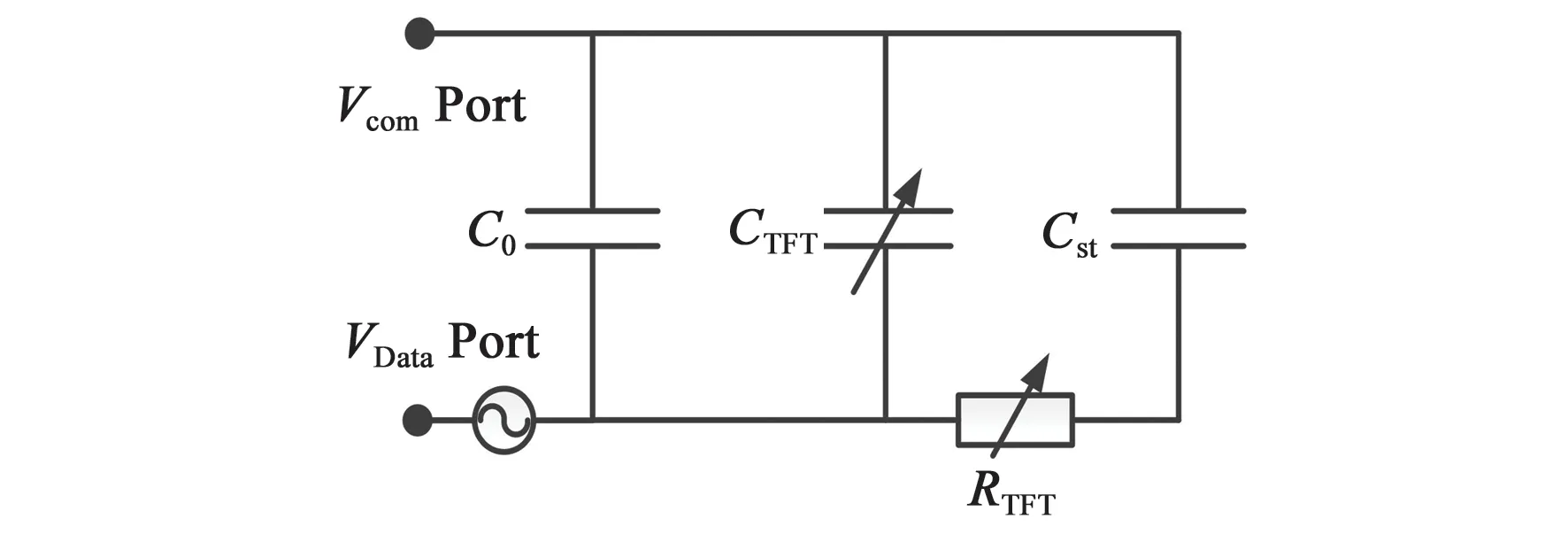

如图2所示,为便于分析电容CDC,将其简化为等效电路模型。C0和Cst为定值。TFT沟道有源层载流子随栅极电压变化,TFT层与Com-ITO形成电容 (CTFT)的有效面积变化,电容值随之改变。本样品因为TFT上方无Com-ITO,所以CTFT始终为0。等效电路中,C0和Cst通过RTFT并联。当TFT的栅极电压和数据电压变化时,TFT电流通过能力发生变化,等同于RTFT阻值变化。TFT完全关闭时,RTFT趋近于无穷大,CDC为最小值等于C0;当TFT完全打开时,RTFT趋近于0,CDC为最大值,等于C0+Cst。也就是说,电容将随着TFT电流通过能力而变化。

图2 CDC等效电路Fig.2 Equivalent circuit of CDC

2.2 电容CDC测量

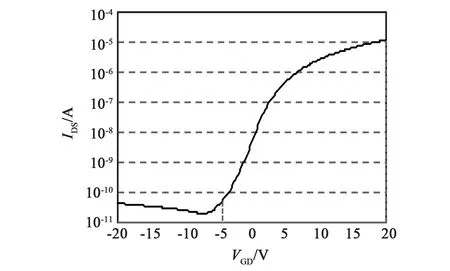

在CDC电容等效模型中将TFT当作等效电阻。在不同栅极电压下TFT电导通能力由图3IDS-VGD曲线表示。图中VGD(栅极和数据电压压差)为-5 V时,IDS为3.5×10-11A,TFT接近完全关闭,RTFT为高阻态。VGD从-5 V增加到20 V,TFT逐渐接近完全开启状态。通过观察实际显示效果VGD为15~20 V时,即可满足像素正常充放电,可认为RTFT接近低阻态。

图3 TFT IDS-VGD特性曲线Fig.3 Characteristic of TFT’s IDS-VGD curve

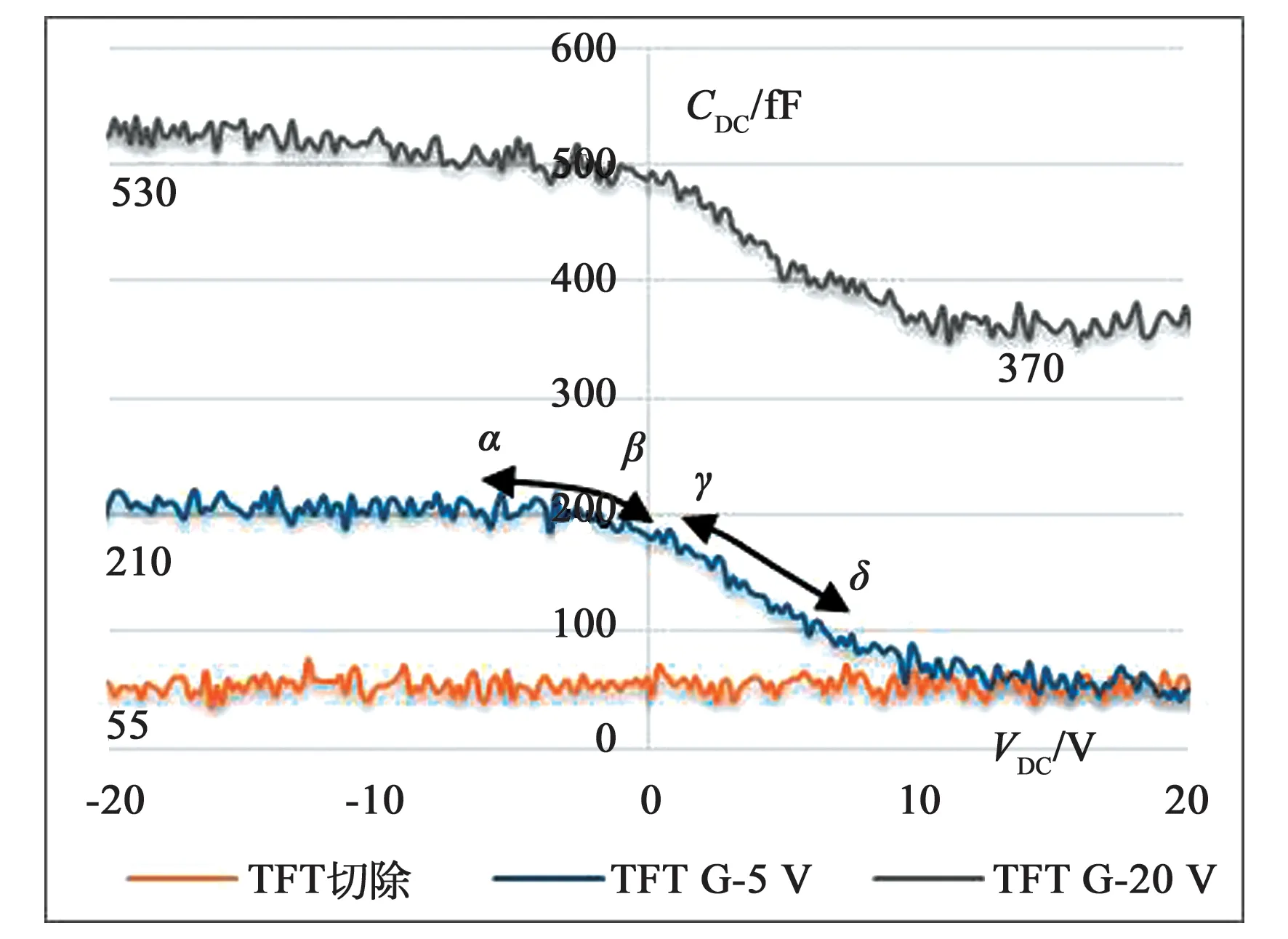

图4为CDC随VDC(数据电压与公共电压压差) 变化测试结果。图中TFT切除时测试得到的电容值为最小值(55 fF),即C0。当栅极电压为-5 V时,随着VDC增大,对应TFT工作状态在图3曲线中左移(即VGD减小,TFT倾向于关闭),CDC从210 fF减小至55 fF。同样地,当栅极电压为20 V,在VDC小于-10 V时,CDC可达到最大值(530 fF) ,即C0+Cst。随着VDC增大,对应TFT工作状态在图3曲线中左移,CDC减小至370 fF。

根据TFT-LCD像素扫描方式,在显示任一时刻绝大多数TFT处于关闭状态,因此后文CDC采用栅极电压为-5 V对应曲线进行描述。

图4 单像素CDC随数据电压/公共电压压差变化Fig.4 CDC changes with the voltage difference between data and common voltage

3 电容CDC对公共电压畸变的影响

3.1 畸变的测量方法

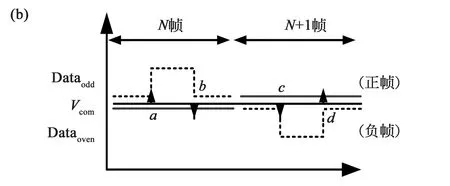

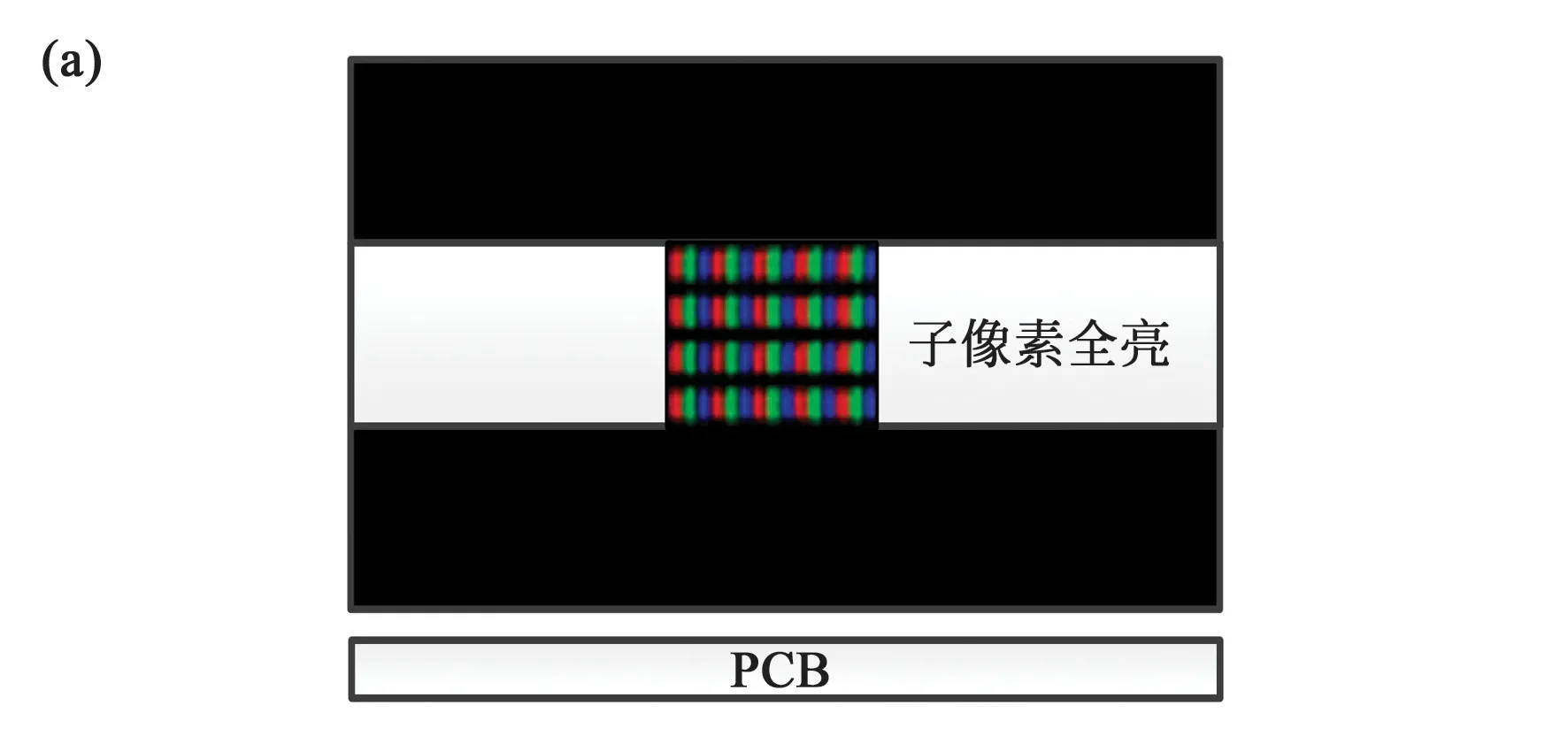

棋盘格(7×5)为液晶显示行业通用的残像评价画面。为分析解决显示棋盘格带来的残像不良,将在棋盘格画面测量公共电压的畸变。面板驱动电压采用“列正负帧反转”模式(其相邻两列数据电压极性相反),图5所示为棋盘格画面及数据电压示意图,在此画面下测量公共电压受数据电压转换的影响程度。通常在面板远端设置公共电压反馈金属线,并通过FFC排线连接至PCB,作为屏内公共电压的监测点。将监测反馈的信号与公共电压设定值进行比较后实时反向补偿,达到稳定公共电压的目的。

通常面板内公共电压补偿点和反馈点的分布数量有限,分布于面板周边区域;同时传输补偿电压的金属线线宽窄(特别是窄边宽产品)、电阻较大。因此面板内公共电压的各个区域的畸变,无法通过补偿达到完全均一。

图5 (a) 棋盘格画面及数据电压的金属线;(b) 数据电压转换及对应公共电压畸变。Fig.5 (a) Chessboard pattern and the metal line of data voltage;(b) Data voltage conversion and corresponding common voltage distortion.

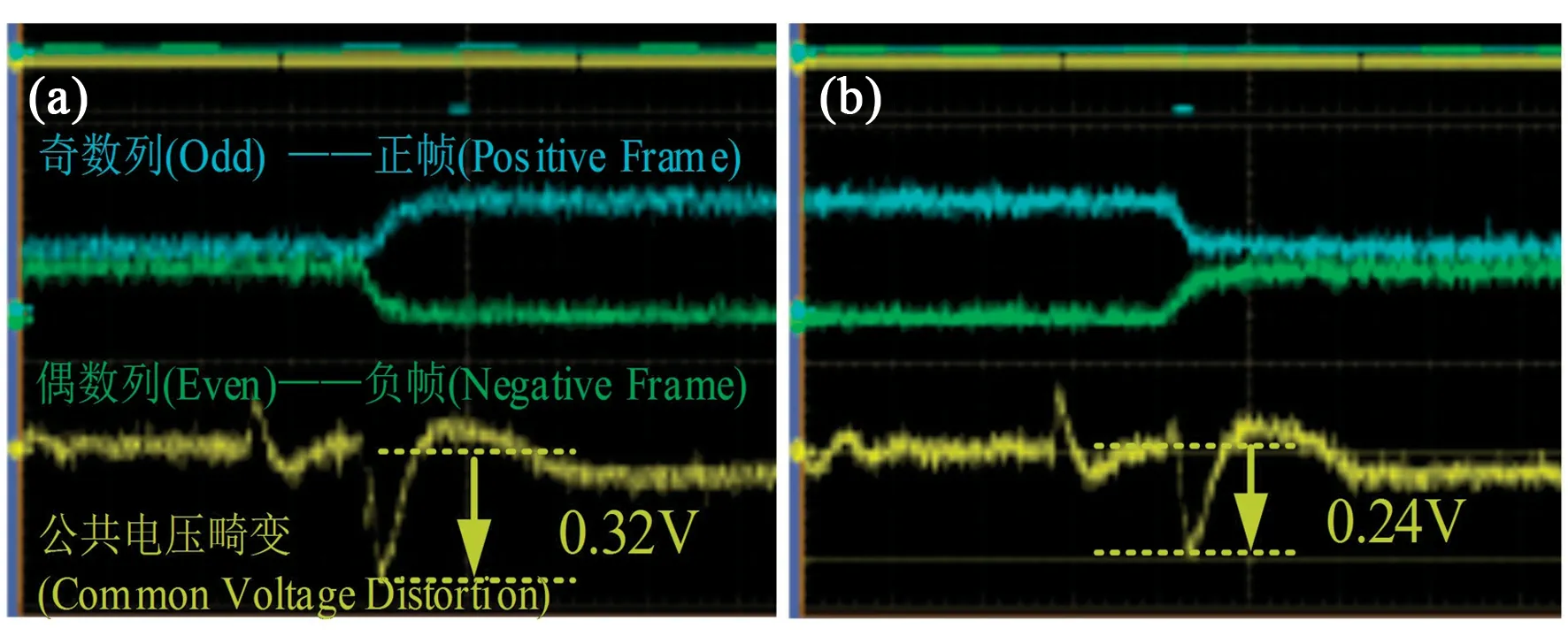

如图6所示,利用示波器抓取公共电压变化的波形。在7×5棋盘格下,沿着数据电压示意线(图5),“黑格→白格”时刻公共电压畸变量为-0.32 V,“白格→黑格”时刻公共电压畸变量为-0.24 V,恢复时间约为0.5 μs,部分产品的恢复时间达到10~30 μs。可以看出畸变量均为负值,奇偶列相反极性的数据电压转换对公共电压的影响无法抵消。

图6 棋盘格转换对应公共电压畸变。(a)黑格转白格;(b)白格转黑格。Fig.6 Distortion ofcommon voltage for the conversion of checkerboard pattern; (a) Black to white; (b) White to black.

3.2 公共电压畸变量与线残像

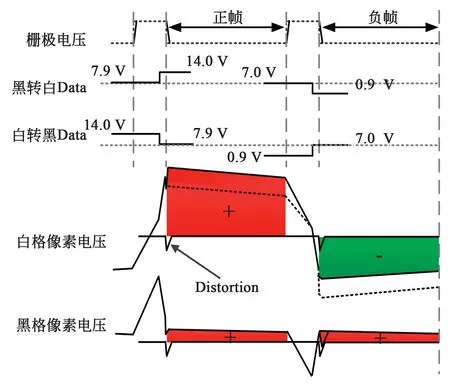

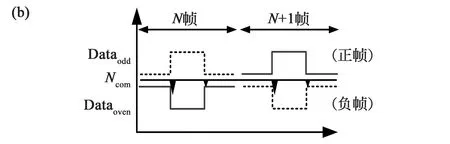

如图7所示,以黑格转白格为例进行描述,正帧时受到公共电压向下畸变的影响,TFT的栅极电压关闭前正帧的像素电压和公共电压压差增大,存储电容存储的正电荷(Q=CU)也增大[8];负帧时,像素与公共电压压差绝对值减小,存储的负电荷减小。同理,白格转黑格时受公共电压畸变量影响,黑格的正负帧的存储电荷倾向于正电荷。因此在正负帧周期内存在明显的正向偏压,并对液晶产生极化。线残像程度与公共电压畸变量及恢复时间呈正相关,数值越大、恢复时间越长,残像的线宽度越宽。对于UHD/60 Hz显示屏来说,1 H时间为7.6 μs,当恢复时间为30 μs时,残像线宽约为4行。因为线残像具有局部区域性,难以通过电路调制完全改善。

图7 正负帧像素储存电荷示意图Fig.7 Diagram of stored charge of positive and negative frame pixels

3.3 公共电压畸变为负值的原因

为了抵消持续正帧或者负帧造成的液晶极化,现有设计均采用正负帧交替驱动液晶。同时受到数据驱动IC限制,奇偶列数据电压同一时间正负极性相反。然而在前面的测试分析中,正常点屏在棋盘格画面测试得到公共电压畸变量始终为负值,正负帧及奇偶列无法抵消。接下来将分别测试奇列或者偶列的正帧和负帧分别驱动时数据电压转换对公共电压的耦合。

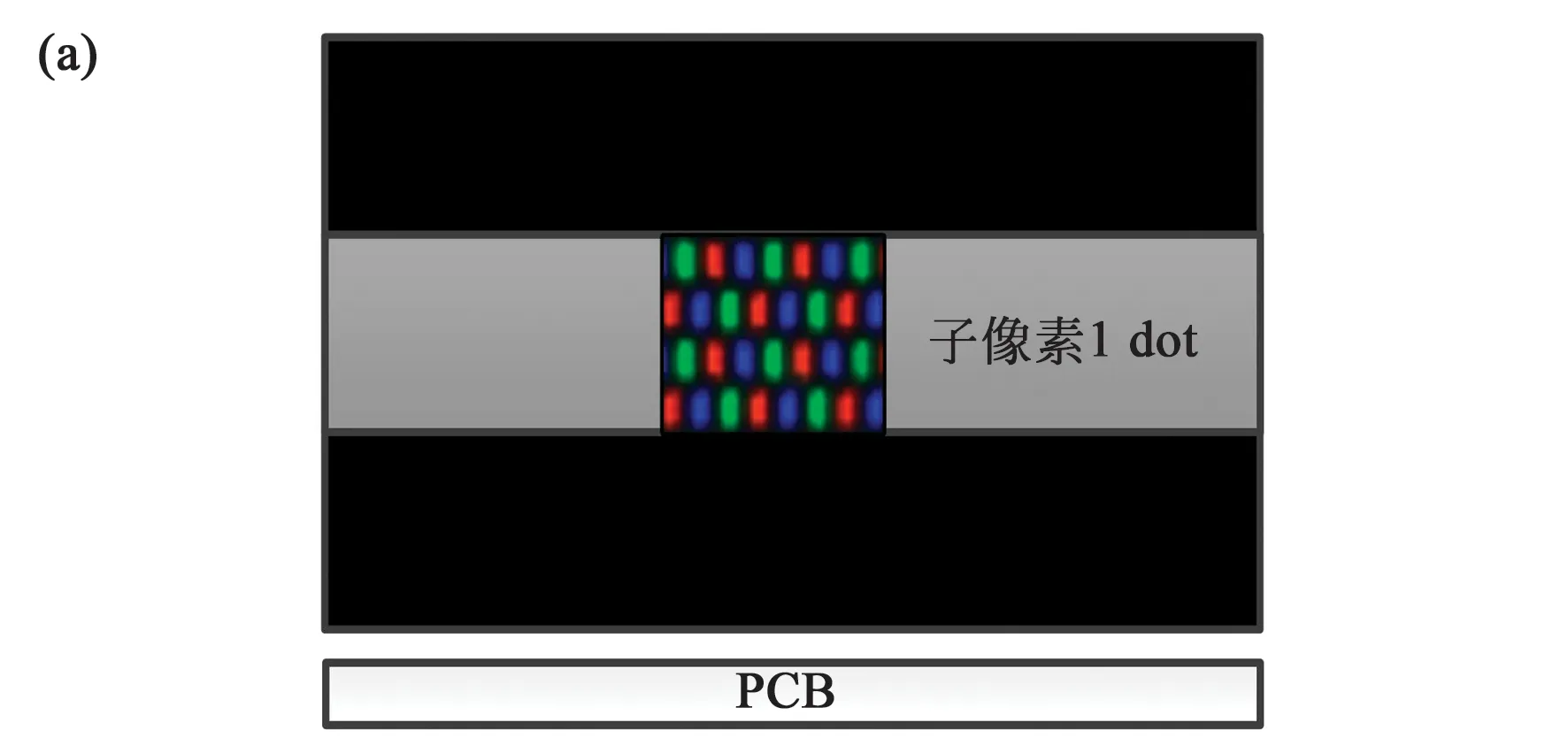

棋盘格画面中同一行不同列对应的数据同时有黑格和白格信号。在同一时间的数据电压转换时既有黑格转白格,也有白格转黑格。为了同一时间测试得到的公共电压畸变量为较大值以减小测试误差,如图8所示进行数据信号设置。一帧时间内偶数列为黑白黑数据信号,奇数列数据电压为黑点电压,同时使同一行的数据电压相同,形成的图案表现为黑灰黑条状(样品面板采用“Z-反转”像素分布结构,中间区域在该数据电压设置时微观表现为1 dot,宏观上为灰色)。同理,如图9所示,进行“黑白黑条”数据电压及其画面设置。

图8 (a)黑灰黑条画面;(b)黑灰黑条画面的数据电压。Fig.8 (a) Black-gray-black block pattern;(b) Data voltage for black-gray-black block pattern.

图9 (a)黑白黑条画面;(b)黑白黑条及其数据电压。Fig.9 (a) Black-white-black block pattern;(b) Data voltage for black-white-black block pattern.

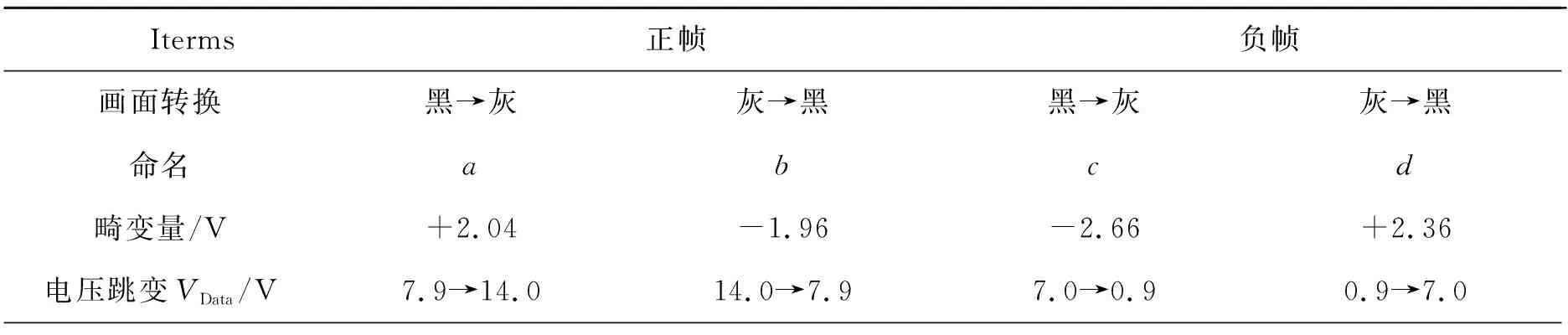

下面进行上述画面数据电压耦合公共电压产生畸变的测量及分析。表1给出黑灰黑条画面的公共电压畸变值、数据电压、公共电压及其压差(VDC),数据电压转换时间 (TData)越短,跳变越快。对照图4,表1给出不同VDC下的CDC变化趋势。畸变量描述如下:正帧时,将黑→灰变化时公共电压畸变量命名为a,幅值为+2.04 V;“灰→黑”畸变量命名为b,幅值为-1.96 V。类似地,负帧时“黑→灰”畸变量命名为c,幅值为-2.66 V;“灰→黑”畸变量命名d,幅值为+2.36 V。

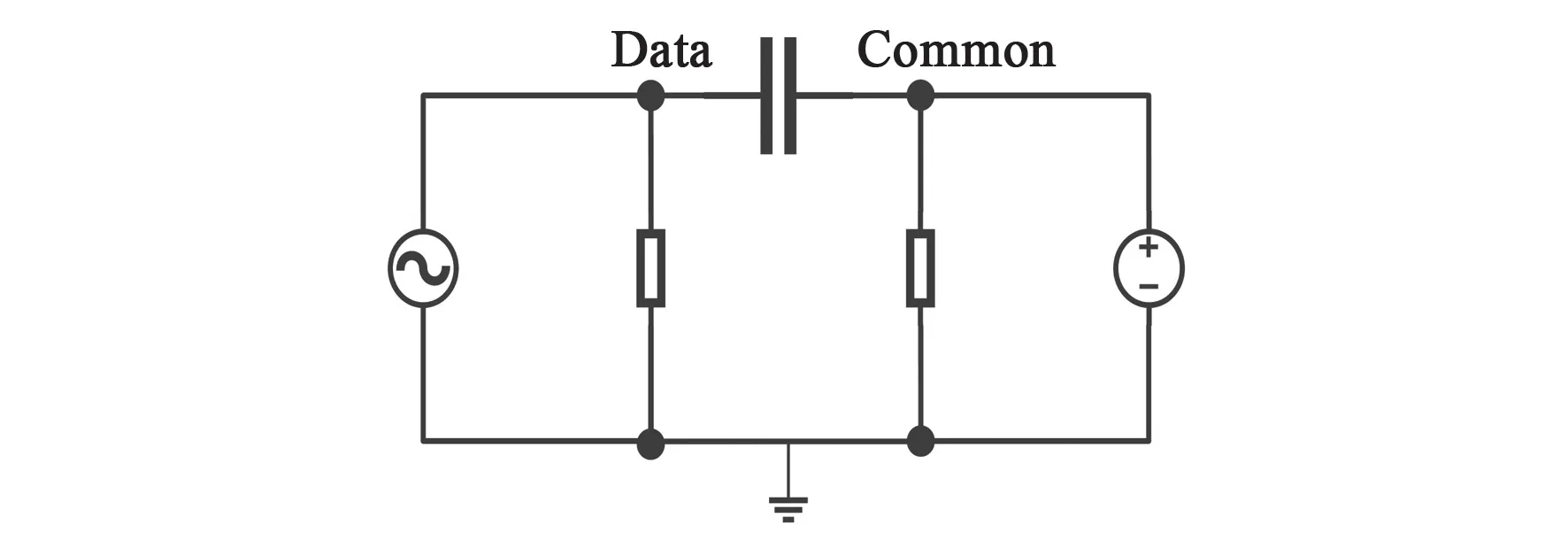

分别与数据电压和公共电压相接的导体形成的电容CDC符合一般电容的“阻直流通交流”的特性(图10),利用式(1)[9]进行畸变量数值差异的阐述。I越大,数据电压端电流“流过”电容到达公共电压端的数量越多,公共电压畸变量越大。因为在画面变化时,正帧电容CDC小于负帧,且正帧数据电压转换时间大于负帧,所以负帧的畸变量大于正帧。对于正帧,虽然转换时间“黑→灰”略大于“灰→黑” (116 ns >104 ns),但在“黑→灰”转换过程中,CDC趋势大于“灰→黑” (180 fF >110 fF),总体上畸变量a大于b。对于负帧,在“黑→灰”过程中,CDC与“灰→黑”过程相当,因为“灰→黑”电压跳变速度(50 ns)明显快于“黑→灰”(83 ns),使畸变量c明显大于d。

I=CDC×dVDC/dt.

(1)

图10 数据电压与公共电压电容耦合示意图Fig.10 Schematic diagram of capacitive coupling between data and common voltage

表1 黑灰黑条对应公共电压畸变量及阻抗计算参数Tab.1 Distortion of common voltage for black-grey-black block pattern and parameters of impedance calculation

续 表

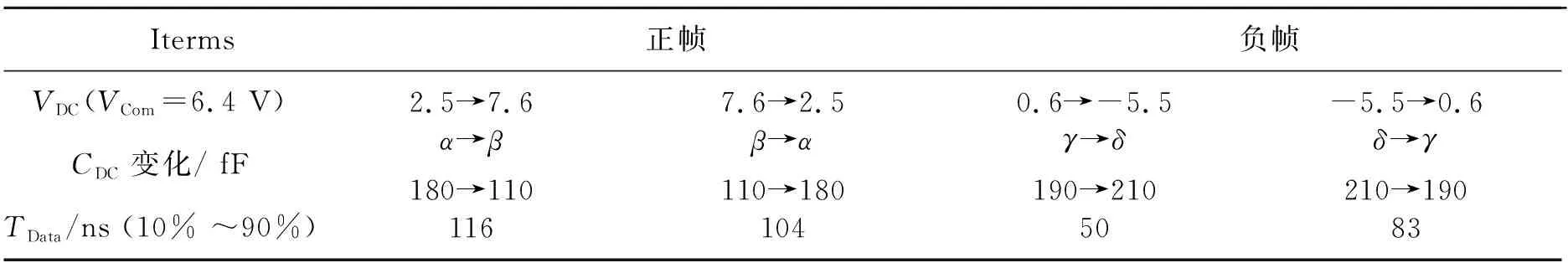

对于黑白黑条来说,公共电压的畸变由奇数列和偶数列相反极性跳变共同影响。在黑白黑条画面,黑→白、白→黑切换时公共电压畸变量测试值分别为-0.59 V、+0.36 V,与通过黑灰黑条计算值-0.62 V、+0.38 V相近。这也证实了黑白黑条画面公共电压畸变量可由黑灰条正负帧对应畸变量组合而成。对于棋盘格画面来说,公共电压向下的耦合程度大于向上的耦合程度,所以综合来看公共电压畸变量为负值。

表2 黑白黑条-公共电压畸变量

3.4 公共电压畸变减弱

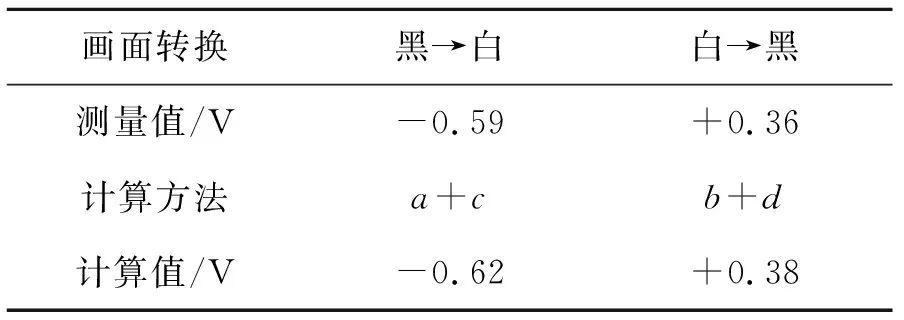

通过以上分析可以得出,减弱公共电压畸变量可以从减小CDC和减小数据电压转换速度两个方面进行。通过减小数据电压金属线与公共电压金属线交叠面积的方式可以减小C0[10]。通过设置数据电压驱动IC不同转换快慢的方式来减弱CDC带来的影响或者通过减小存储电容的方式来减弱公共电压畸变量未见报道。通过缩小正负帧数据电压转换快慢的差异,甚至将负帧数据电压转换速度略慢快于正帧,用于抵消CDC负帧大于正帧对公共电压畸变量的影响,该改善方案需结合数据电压驱动IC设计完成。现有IC只能调整电压转换的整体快慢,无法单独调试正帧或者负帧的电压转换速度。也就是说正帧、负帧的电压转换速度差异在现有IC设计条件下仍然存在差异。如表3所示,转换速度可调4档(00<01<10<11)在电容相当时,转换速度越慢(48 ns→55 ns),公共电压畸变量越小(2.67 V→2.61 V)。

表3 电压转换速度与公共电压畸变量Tab.3 Slew rate level and distortion

4 结 论

对于TFT-LCD残像画面,数据电压转换通过电容CDC对公共电压产生影响。奇偶列相反极性数据电压转换对公共电压影响程度不一致,无法相互抵消,产生负向畸变量,使得液晶极化,从而产生线残像。

本文通过实验和理论研究,提出TFT-LCD 数据电压和公共电压之间的实际工作电容CDC模型。数据电压金属导线通过TFT与像素ITO相连,将TFT状态作为电容变化关键影响因素。当TFT断开时呈现高阻态,电容交叠面积最小,对应容值为55 fF;当TFT完全打开时呈现低阻态,电容交叠面积最大,对应容值为530 fF;当TFT处于中间态时,测试得到的电容值为中间值。

本文结合电容阻抗式,解释“数据电压列正负帧反转”模式下棋盘格画面公共电压畸变量产生来源为不同图案数据电压转换快慢及电容差异。电容值越大,转换速度越快,畸变量越大。奇偶列相反极性数据电压转换产生的畸变量无法相互抵消,畸变量始终存在且为负值。

本文通过测量不同数据电压转换速度对应的公共电压畸变量,得出通过匹配合适的电路设计使正负帧畸变量绝对值趋于一致的可能性。总体上,本文对公共电压畸变量导致的线残像的分析改善和面板设计提供了新的帮助。