TFT阵列基板过孔电阻与耐流性能研究

陈运金, 欧忠星, 冯玉春, 林 忱, 刘 耀, 张 千, 陈 曦, 周 贺, 刘文瑞

(福州京东方光电科技有限公司,福建 福州 350300)

1 引 言

当前,薄膜晶体管液晶显示(Thin Film Transistor Liquid Crystal Display,TFT-LCD)成为市场主流显示技术,涵盖从手机到大尺寸电视的各种显示领域。薄膜晶体管阵列作为TFT-LCD的核心部件,在有源矩阵驱动显示器件中发挥了重要作用。晶体管阵列基板制备流程复杂,主要工序包含金属成膜、光刻胶涂覆曝光、湿法刻蚀、干法刻蚀、光刻胶去除等。在薄膜晶体管阵列制备过程中,需要各工序间紧密配合,任何一道工序出现缺陷都会影响最终的成品率[1]。在TFT薄膜晶体管制备中需要使用一种关键材料——氧化铟锡(Indium Tin Oxide,ITO),它是一种n型半导体陶瓷薄膜,凭借其高的可见光透射率、高的电导率、坚固、耐碱、耐高温及好的光刻性能等优良特性,被广泛应用于电子工业、屏蔽防护、光电子器件、液晶显示器件及太阳电池等行业[2]。TFT显示阵列基板的过孔是在完成栅极、源漏极以及绝缘层成膜之后的基板上,通过光刻胶涂覆曝光、干法刻蚀、光刻胶去除等方法制备得到的。通过在过孔的内部沉积一定厚度的ITO膜,利用ITO膜的导电性可以实现不同层间连通。过孔作为半导体显示阵列基板中一种重要单元,起着传输不同层间驱动信号作用,一旦存在过孔缺陷将会导致层间驱动信号传递失效,引起显示功能异常。随着显示技术的快速发展,各种高刷新率产品的开发对过孔性能提出了新要求,低电阻以及高耐流性的过孔是未来发展趋势[3]。然而,目前高耐流性能过孔的研究和应用面临重大瓶颈,主要是由于针对过孔耐流性影响因素以及作用机理尚不明确,如何制备出低电阻、高耐流性过孔的工艺技术方案不明确,也暂未有文献进行过相关报道。因此,针对TFT显示阵列基板的过孔耐流性的影响因素以及如何提升过孔耐流性的研究具有较高的研究价值和应用前景。

2 实 验

2.1 基板中部异常显示失效分析

在福州京东方8.5代TFT-LCD面板生产线的画面检测工序发现了产品A中高发绿色画面下明显可见的多条竖向暗线以及多条横向暗线异常,如图1所示。

图1 异常高发位置图Fig.1 Location map of high incidence adverse phenomena

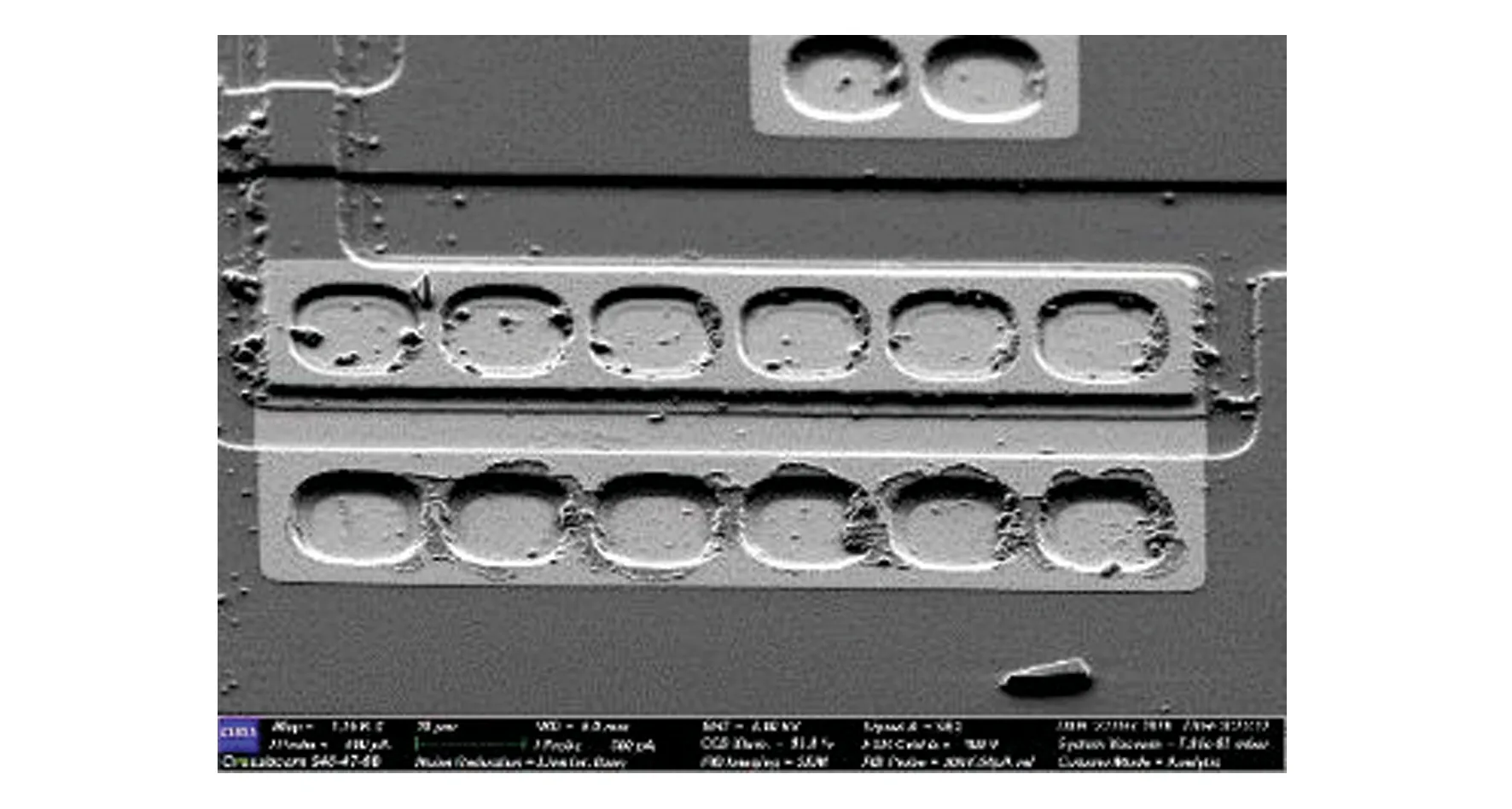

针对异常现象高发位置的分布发现,异常现象多发生于基板中部,严重时表现局部块状区域异常。因此针对基板中间区域的基板各组成单元借助聚焦离子束-扫描电子显微镜 (Focused Ion Beam-Scanning Electron Microscope,FIB-SEM)设备进行缺陷确认,发现基板中部多组过孔微观图像存在烧毁缺陷,如图2(a)所示。接下来为进一步确认显示异常与过孔烧毁缺陷有关,针对存在缺陷的过孔进行钨粉沉积实验发现,对烧毁过孔沉积钨粉后,异常显示现象消失。因此可以判断异常显示为过孔烧毁导致。

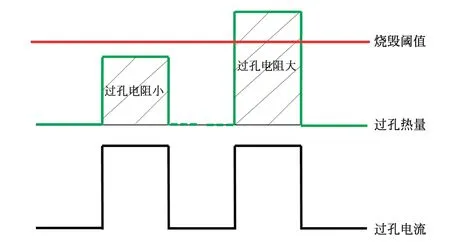

由于TFT阵列基板过孔起到传输不同层间信号的作用,当TFT阵列过孔工作时会施加一定频率的电流,电流通过过孔时会有热量产生。根据焦耳定律可知:过孔电阻越大,发热量越大,也就越容易超出烧毁阈值引起ITO膜层烧毁。过孔烧毁机理如图2(b)所示。

(a)过孔微观图 (a)Via hole micrograph

(b)过孔烧毁机理图(b) Diagram of via hole burning mechanism图2 过孔烧毁以及烧毁机理示意图Fig.2 Diagram of burning via hole and burning mechanism

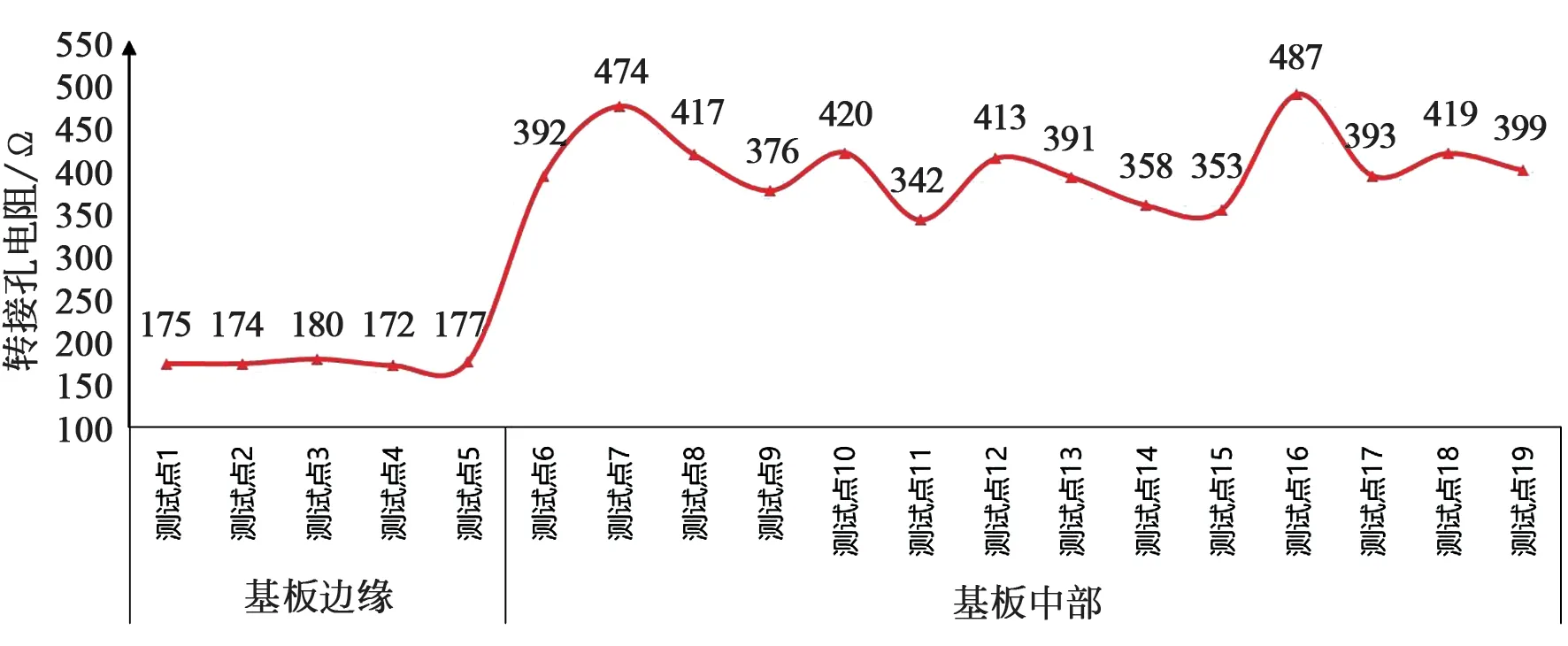

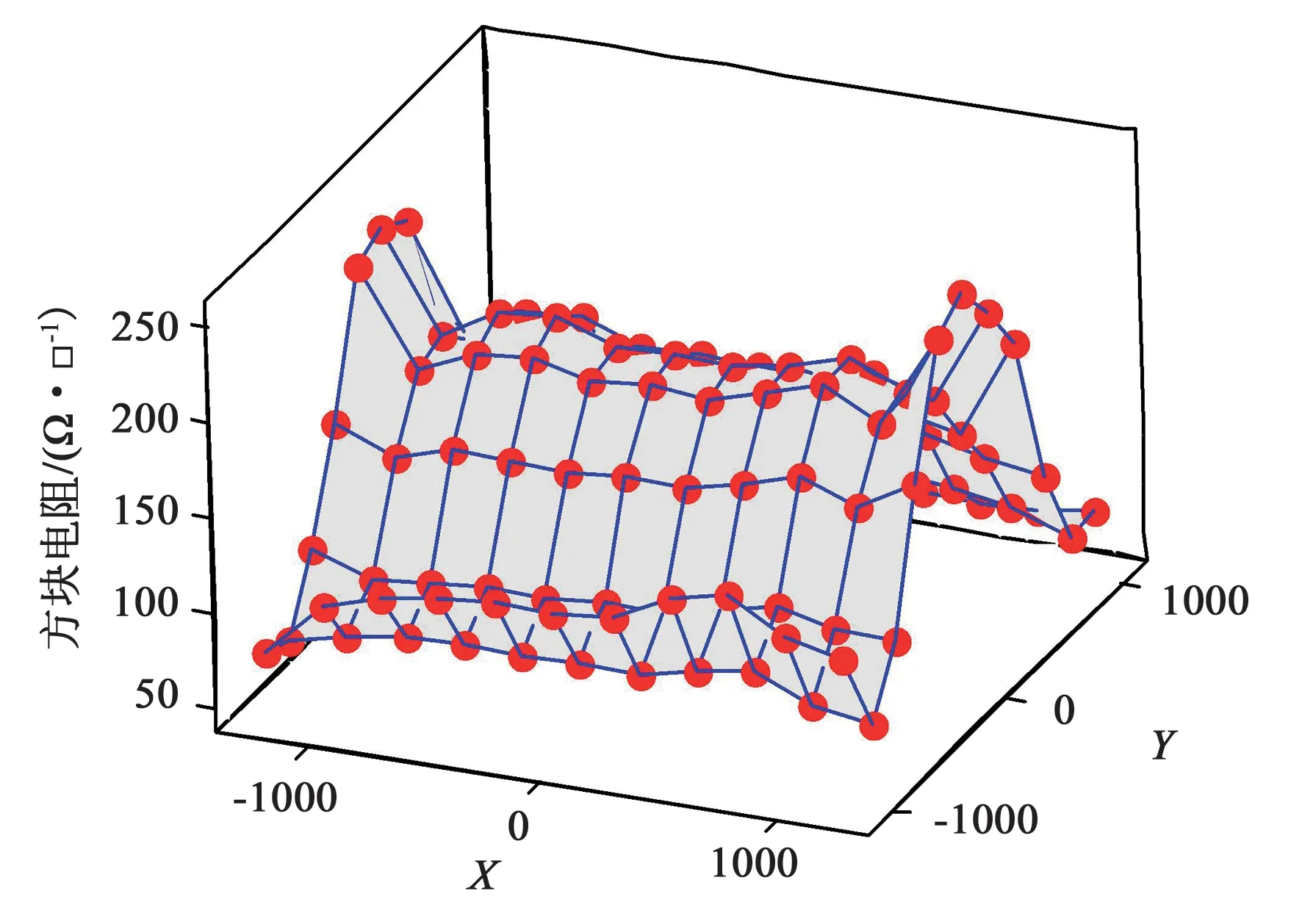

图3 基板不同区域过孔电阻测试结果Fig.3 Test results of via hole resistance in different areas of substrate

为了明确TFT阵列基板过孔电阻大小分布趋势,实验利用阳电子YAF-6565M TFT Probe Station设备针对基板不同区域的过孔电阻进行测试,结果表明:基板中部的过孔电阻均值为402 Ω,基板边缘的过孔电阻均值为176 Ω,中部的过孔电阻明显偏大,如图3所示。结合异常现象失效分析可以明确,基板中部出现的多条横竖向线显示异常的原因是基板中部的过孔电阻大、耐流性差,引起中部过孔烧毁导致。

为改善基板中部过孔电阻偏大、耐流性差的问题,本文针对ITO膜方块电阻、过孔坡度角及ITO膜与金属接触面积3个因素分别设计实验进行研究。

2.2 实验设计

2.2.1 实验一:ITO膜方块电阻的影响

TFT阵列基板的过孔是通过在孔的内部沉积一定厚度的ITO膜,利用ITO膜的导电性实现不同层间连通。因此ITO膜本身的电阻大小很大程度上会影响过孔电阻。为测试ITO膜厚,常使用ITO膜的方块电阻R□来进行表征。

R□=ρ/t,

(1)

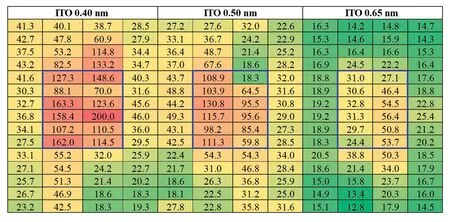

其中R□为膜的方块电阻,ρ为膜的电阻率,t为膜的厚度。产线中稳定生产的ITO膜,在其成膜参数固定情况下膜电阻率基本不变,方块电阻仅与膜厚有关,因此业内常用方块电阻R□来测试ITO膜厚度。通常ITO膜厚度越大,其方块电阻越小[4]。为了研究ITO膜方块电阻与过孔电阻的关系,实验采用ULVAC SMD-2400D型立式磁控溅射镀膜机在玻璃基板表面沉积ITO膜,镀膜尺寸为2 500 mm×2 200 mm,镀膜厚度分别为0.40,0.50,0.65 nm。针对不同ITO膜厚过孔采用四探针测试方法进行过孔电阻测试,结果如图4所示。

图4 不同ITO膜厚下过孔电阻测试结果Fig.4 Test results of via hole resistance under different ITO film thickness

从图4中的测试结果可以发现,0.40,0.50,0.65 nm ITO膜厚下基板过孔电阻均值分别为57.9,44.4,23.1 Ω。ITO膜越厚,基板过孔电阻越小,而且基板中部(蓝色框范围内)过孔电阻相较于边缘差异变小。实验一结果表明,通过增加ITO膜厚度可有效降低ITO膜方块电阻进而降低整体过孔电阻,缩小基板中部与边缘过孔间电阻差异。

2.2.2 实验二:过孔坡度角的影响

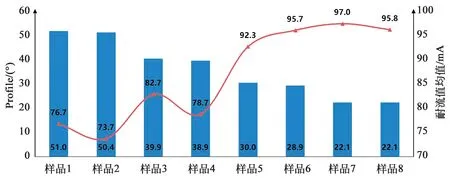

TFT阵列基板过孔是在过孔工艺段形成的,过孔的截面会形成有坡度角(Profile)的梯形状台阶,其坡度角的大小形成受膜质、光刻、刻蚀等参数的影响[5]。为研究坡度角对过孔耐流性影响,实验二通过调控绝缘层膜质与刻蚀参数制备出具有不同坡度角的过孔。针对不同坡度角的过孔施加从低到高的电流,当过孔施加的电流足够大时,将会引起过孔烧毁,此时施加的电流即为该过孔的耐流值,测试结果如图5所示。从测试结果中可以发现,当坡度角在38.9°~51.0°范围内,过孔耐流值不超过82.7 mA;当坡度角小于30°时,过孔耐流值普遍超过92.3 mA。过孔坡度角与耐流值成负向线性关系,即坡度角越大,过孔耐流值越小,越容易发生烧毁。通过减小过孔坡度角可有效提升过孔电阻耐流性。

图5 过孔坡度角与耐流值关系Fig.5 Relationship between slope angle of via hole and current resistance value

2.2.3 实验三:ITO膜与金属接触面积的影响

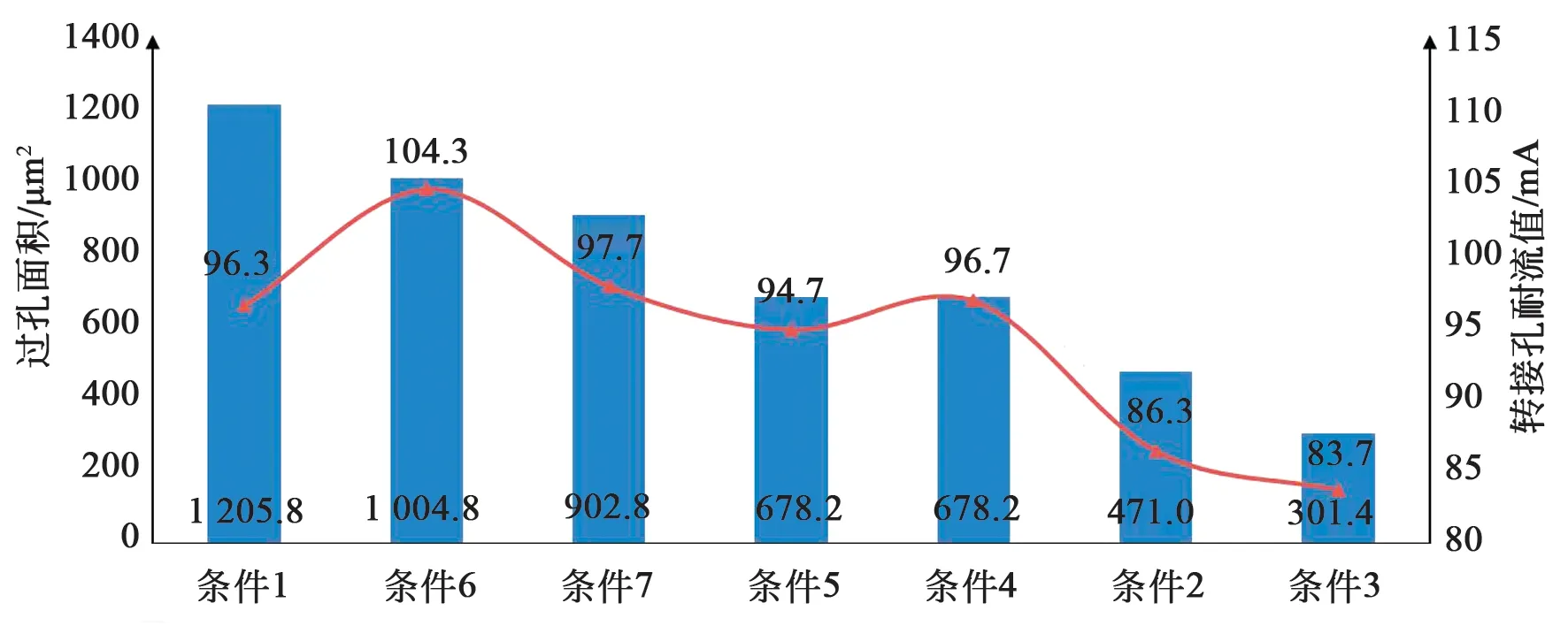

为研究过孔中ITO膜与金属接触面积对于过孔耐流性能的影响,在产品C中搭载不同设计的过孔TEG (Test Element Group) 进行耐流值测试,根据设计的孔径以及个数可以计算出过孔中ITO膜与金属接触面积,过孔设计基本参数如表1所示。

表1 过孔TEG设计参数Tab.1 Parameters of via hole TEG

续 表

实验中针对不同的过孔进行了过孔耐流值测试,如图6所示。测试结果表明:当过孔与金属接触面积大于678.2 μm2时,过孔耐流值超过96.7 mA;当过孔与金属接触面积减小至301.4 μm2时,过孔耐流值减小至83.7 mA。实验三测试结果表明,ITO膜与金属接触面积越大,过孔耐流值越大[6]。

图6 不同接触面积下过孔耐流值Fig.6 Current resistance of via hole under different contact areas

3 分析与讨论

3.1 过孔电阻与耐流性影响因素及机理

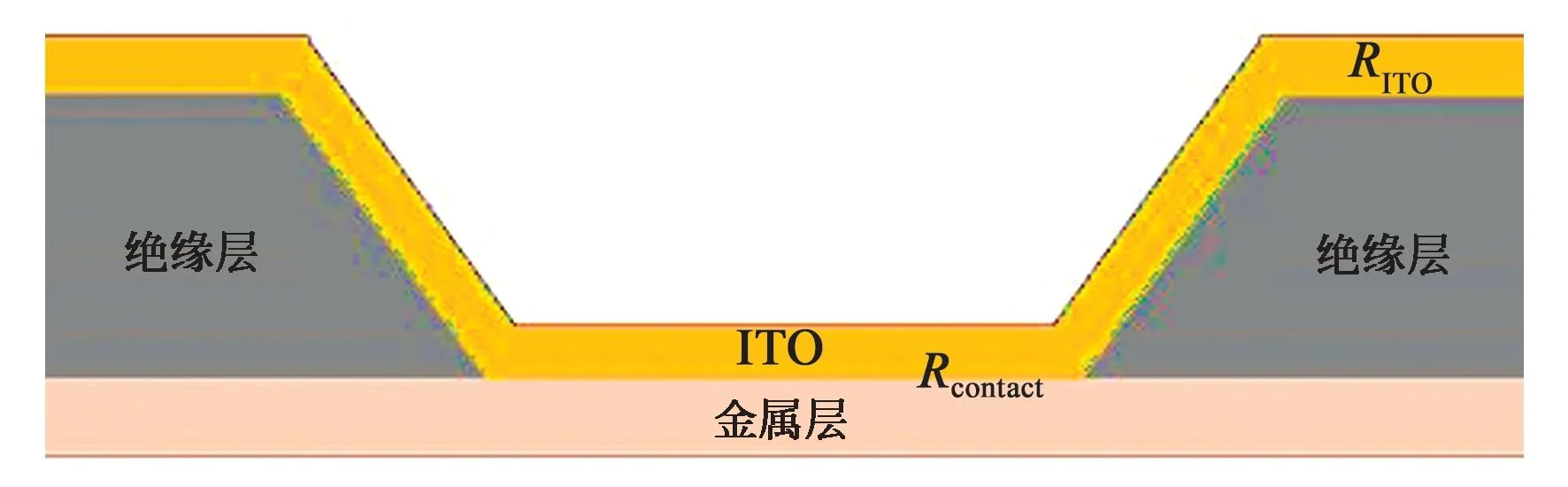

TFT基板过孔从微观截面看出过孔主要由金属层、绝缘层、ITO膜层3部分组成,如图7所示。从过孔结构分析出发,过孔电阻主要由ITO膜与金属层的接触电阻以及ITO膜层自身电阻两部分组成,即R孔=RITO+Rcontact。

图7 过孔截面示意图Fig.7 Schematic diagram of via hole section

3.1.1 ITO膜层自身电阻(RITO)的影响

业界针对单一ITO膜层电阻计算是采用膜层方块电阻乘以长宽比例得到:

RITO=(L/W)×R□,

(2)

其中RITO为膜层电阻,L为膜层长度,W为膜层宽度,R□为膜的方块电阻。从膜层电阻的计算定义可知,影响膜层电阻大小的主要因素是膜的方块电阻以及长宽比例,而ITO膜厚是影响膜的方块电阻R□的重要因素。一般情况下,在TFT阵列基板的过孔中ITO膜层长宽比例是固定的,这意味着ITO膜厚大小将直接影响ITO膜层自身电阻(RITO)大小。因此实验一中在过孔的接触电阻(Rcontact)不变的情况下ITO膜层加厚,其方块电阻减小可有效降低ITO膜层自身电阻(RITO),起到降低过孔电阻的作用。

2020年,刘丹[7-9]等人发现坡度角是影响后续膜层覆盖率的关键因素,坡度角与膜层覆盖率成负向线性关系。如图8所示,覆盖率为爬坡处膜厚a与顶层膜厚b的比值。当坡度角变小时,会引起ITO膜层覆盖率增高,即爬坡处ITO膜厚度a变大。在实验二中验证了增大过孔坡度角将会引起过孔耐流值下降,主要原因是当过孔坡度角变大时ITO膜覆盖率下降,爬坡处ITO厚度减小,其方块电阻变大,引起爬坡处ITO膜自身电阻(RITO)变大,进而导致过孔耐流值下降。

图8 过孔覆盖率示意图Fig.8 Schematic diagram of via hole coverage

3.1.2 接触电阻(Rcontact)的影响

过孔中的接触电阻(Rcontact)大小主要与ITO膜与金属基底间接触质量有关。使用微观手段对过孔底部研究发现,ITO膜层与金属接触面有许多凹凸不平的情况存在。由于在阵列基板制造过程中的一些杂质、微尘以及反应物极易嵌藏在表面的微观凹坑处,导致ITO膜层与金属层的实际有效接触面积缩小,接触电阻增大且电阻不稳定。在实验三中ITO膜与金属接触面积增大,本质上是使ITO与金属层的有效接触面积变大,降低了过孔接触电阻。在ITO膜层自身电阻(RITO)不变的情况下,降低ITO膜与金属层的接触电阻(Rcontact),可实现降低过孔电阻的作用。

综上分析,过孔电阻主要由ITO膜层自身电阻(RITO)及过孔接触电阻(Rcontact)两部分组成。ITO膜方块电阻减小以及过孔坡度角减小会导致ITO膜层自身电阻(RITO)减小,ITO膜与金属接触面积增大会导致过孔接触电阻(Rcontact)减小。改变ITO膜方块电阻、过孔坡度角、ITO膜与金属接触面积均能引起过孔电阻及耐流性的变化。

3.2 基板中部过孔电阻大及耐流性差机理

本文实验中提到的改变ITO膜方块电阻、过孔坡度、ITO膜与金属接触面积均会对过孔电阻产生影响。为明确产线中出现的基板中部的电阻偏大、耐流性差现象的机理,本文分别针对产品A基板的ITO膜方块电阻、过孔坡度角分布情况进行了确认。由于在产品A生产过程中对于过孔直径进行了严格管控,过孔直径基本不变,因此ITO膜与金属接触面积基本不变,其影响可忽略不计,故本文未对该因素影响进行分析。

3.2.1 ITO膜方块电阻分布的影响

ITO成膜设备中有一个重要部件单元——托盘遮罩(Tray Mask),其使用寿命的长短会影响ITO镀膜的质量。为研究托盘遮罩使用寿命对于ITO膜方块电阻大小及分布的影响,本文采用四探针法测试不同托盘遮罩寿命下沉积相同厚度的ITO膜(0.40 nm)方块电阻大小及分布情况,如图9所示。通过对比图9(a)和9(b)不同托盘遮罩寿命下ITO膜方块电阻测试结果可以发现:托盘遮罩寿命初期和末期基板中部方块电阻分布均表现出偏大趋势。初期整体方块电阻均值为104.1 Ω/□。末期整体方块电阻均值为131.9 Ω/□;随着托盘遮罩使用寿命的延长,基板整体方块电阻变大。

(a)托盘光罩初期电阻 (a)Resistance of initial tray mask

(b)托盘光罩末期电阻 (b)Resistance of last phase tray mask图9 方块电阻在基板的分布Fig.9 Distribution of block resistance on substrate

ITO膜方块电阻中部偏大主要有两方面因素引起:一方面产线ITO成膜设备中部存在冷阱区域,相较于边缘区域中部冷阱区域水分压更大(水含量更高),导致基板中部ITO成膜含水量较大引起方块电阻变大;另一方面在ITO退火过程中玻璃基板中间位置热风阻相较于边缘位置大[10],中部退火温度较低ITO结晶效果较差,导致ITO膜方块电阻中部偏大。

3.2.2 坡度角分布影响

图10 过孔坡度角在基板的分布Fig.10 Distribution of via hole slope angle on substrate

为研究坡度角在基板上的分布趋势,本文借助扫描电子显微镜(Scanning Electron Microscope,SEM)针对产品A基板不同位置过孔坡度角进行测量,测试结果如图10所示。从测试结果可以看出,基板中部(蓝色框范围内)坡度角均值为42.3°,相比于边缘坡度角(基板两侧边缘)均值34.1°偏大。根据试验二结果可知,当坡度角变大时,会导致ITO膜覆盖率下降,爬坡处ITO厚度减小,方块电阻变大,引起爬坡处ITO膜层电阻变大、过孔耐流值下降,易引起中部过孔烧毁。

在过孔刻蚀中主要使用的是干法刻蚀,主要原理是活性等离子体在高频电场作用下,存在于电场中的电子被电极电场加速运动与反应气体产生碰撞,反应气体发生激发或者电离产生活性基团或离子(活性等离子体),活性离子在电场的作用下高速撞击基板进行刻蚀。干法刻蚀的主要反应方程式如下:

SF6+e→F*+SFx+e,

(3)

Si+4F*→SiF4.

(4)

过孔坡度的形成主要受干法刻蚀中纵向刻蚀以及横向刻蚀的综合作用影响。其中纵向刻蚀主要以活性离子轰击为主,等离子体刻蚀为辅;横向刻蚀主要以等离子体刻蚀为主[11]。在过孔刻蚀中为了保障纵向刻蚀深度确保绝缘层无残留,一般在实际生产中会将实际刻蚀工艺时间设置为刻蚀终点时间(恰好完成一定深度刻蚀下所需要的工艺时间)的1.2~1.3倍。因此在基板中无论边缘还是中部的纵向刻蚀深度(V)都是一样的,确保纵向刻蚀彻底[12]。但是由于基板中部的活性等离子体相比于基板边缘的浓度偏小,导致基板中部横向刻蚀能力较弱,在相同刻蚀工艺时间内中部横向刻蚀距离(H中部)小于边缘横向刻蚀距离(H边缘)。正是由于这种横向刻蚀能力的差异才形成了基板中部相较于边缘坡度角(β)偏大的现象,如图11所示。

图11 不同位置过孔截面差异图Fig.11 Cross section difference of via hole at different positions

基于对基板中部的ITO膜方块电阻、过孔坡度角分布的测试和分析,可以明确基板中部过孔电阻大、耐流性差主要是中部ITO膜方块电阻偏大、中部过孔坡度角偏大两者共同作用的结果。一方面中部ITO膜方块电阻偏大主要与成膜设备在基板中部存在冷阱区域及退火设备基板中部温度较低有关;另一方面中部过孔坡度角偏大与基板中部干法横向刻蚀能力较弱有关。

4 过孔耐流性能改善

为解决福州京东方8.5代线产品A中部高发的过孔烧毁问题,需提升产品过孔耐流性能。基于产品A的曝光遮罩(Exposure Mask)已定型、无法针对过孔接触面积进行调整的情况,需要从其他方向进行改善。为此通过调控绝缘层膜质与干法刻蚀参数来减小坡度角以及增加ITO膜层厚度两种改善方案进行验证。

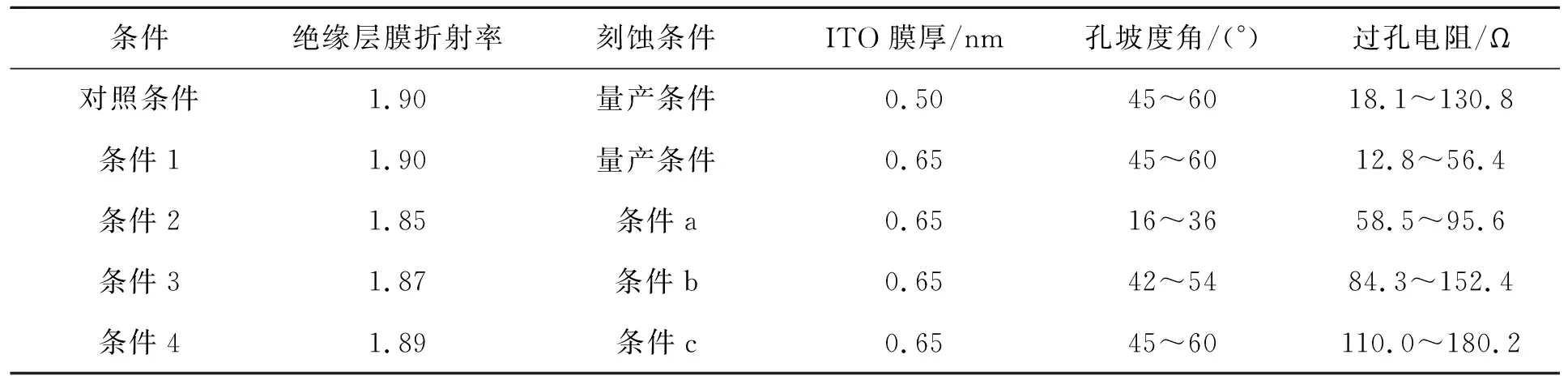

如表2所示,与对照条件相比,条件1中ITO膜厚增加0.15 nm,过孔电阻整体从18.1~130.8 Ω下降至12.8~56.4 Ω,通过ITO膜厚加厚有效降低过孔电阻。设计条件2、3、4的思路是调控绝缘层膜成膜参数制备出膜质不同的绝缘层膜(折射率越大,膜质越致密),通过搭配与膜质匹配的干法刻蚀参数工艺刻蚀后形成过孔,研究在不同膜质与干法刻蚀参数下过孔性能的差异。对比条件2、3、4结果发现,绝缘层膜折射率1.85搭配干法刻蚀条件a时,过孔坡度角在16°~36°范围内,过孔电阻在58.5~95.6 Ω之间,坡度角以及过孔电阻均较小。条件2中绝缘层膜质较软,在干法刻蚀时可以有效降低基板中部和边缘因横向刻蚀能力不同引起的坡度角差异,达到减小过孔坡度角、提升均一性的目的,因此在条件2、3、4中条件2的过孔坡度角及过孔电阻最小。

表2 过孔电阻改善条件及结果Tab.2 Improvement conditions of via hole resistance and result

ITO膜厚加厚和调控绝缘层膜质与干法刻蚀参数均可有效降低过孔电阻、提升过孔耐流性。但是条件2在导入产品A过程中发现存在光学伽马值(Gamma)偏低的问题,导致该措施无法顺利导入量产。而条件1的ITO增厚方案可满足产品光学品质要求,虽然ITO增厚成本会有上升,但是可以使过孔烧毁导致的异常报废率从0.66%下降至0.10%,整体收益性是正向的。因此在产品A中通过导入条件1的ITO增厚措施成功地解决了阵列基板中部高发过孔烧毁问题。

综上所述,在满足产品光学品质标准前提下,ITO膜厚增厚、调控绝缘层膜质以及干法刻蚀参数来减小坡度角、加大过孔接触面积的设计均可有效降低过孔电阻、提升过孔耐流性。

5 结 论

本文针对ITO膜方块电阻、过孔坡度角、ITO膜与金属接触面积3个影响过孔电阻与耐流性的因素设计相关实验,对实验结果以及机理进行讨论分析得出以下结论:

(1) ITO膜方块电阻减小、过孔坡度角减小、ITO膜与金属接触面积增大均可降低过孔电阻、提升过孔耐流性。

(2)过孔电阻主要由ITO膜层自身电阻(RITO)以及过孔接触电阻(Rcontact)两部分组成。ITO膜方块电阻减小、过孔坡度角减小会引起ITO膜层自身电阻(RITO)降低。ITO膜与金属接触面积增加本质是ITO与金属层的有效接触面积变大,引起过孔接触电阻(Rcontact)降低。

(3) 基板中部过孔电阻大、耐流性差主要与中部ITO膜方块电阻偏大、中部过孔坡度角偏大两者共同作用有关。中部ITO膜方块电阻偏大主要与成膜设备在基板中部存在冷阱区域及退火设备基板中部温度较低有关;中部过孔坡度角偏大与基板中部干法横向刻蚀能力较弱有关。

(4) 在满足产品光学品质标准前提下,ITO膜厚增厚、调控绝缘层膜质以及干法刻蚀参数来减小坡度角、加大过孔接触面积的设计均可有效降低过孔电阻、提升过孔耐流性。