LTPS AMOLED显示器像素电路阈值电压补偿效果的改善

皇甫鲁江, 朱健超, 赵旭亮, 卢江楠, 刘利宾

(京东方科技集团股份有限公司 技术中心, 北京 100176)

1 引 言

低温多晶硅薄膜晶体管(Low Temperature Poly Silicon TFT,LTPS-TFT)固有的阈值电压(Threshold Voltage,Vth)等特性的空间变动性(Spatial Variation)对采用该器件驱动的有源矩阵(Active Matrix,AM)有机发光二极管(OLED)显示器画面品质有着不可忽视的影响[1]。LTPS AMOLED显示器像素电路不仅要有显示信号刷新、帧周期驱动保持等基本功能,还需要对Vth变动性进行补偿。各种带有Vth补偿功能的像素电路被提出以应对这一问题[2-4],其中基于电压方式像素显示信号通过驱动TFT(Drive TFT,DTFT)栅源间电压信号的构成进行Vth变动性补偿[5-8]电压型(Voltage Program)像素电路的效果得到了肯定,量产LTPS AMOLED显示器主流像素电路多属于这种类型。

随着移动通信显示等方面应用中AMOLED显示器分辨率、帧频不断提高,信号刷新行周期变短、像素面积减小,这类电路的工作过程受到了负面影响。由于Vth变动性补偿效果不充分产生的画面品质问题,成为高分辨率、高帧频AMOLED显示器像素电路特性的制约因素。部分产品不得不采用外部辅助技术进行补偿[9],造成了技术复杂程度提高和成本增加。本文介绍的工作致力于通过像素电路本身的改进应对高分辨率、高帧频趋势下Vth补偿效果劣化问题。根据我们此前针对像素电路Vth补偿效果随显示分辨率、帧频提高而下降问题进行的研究[10],本文试图通过进一步的电路工作过程分析,确认影响Vth补偿的关键因素,针对性地提出像素电路改进对策。

2 像素电路工作过程

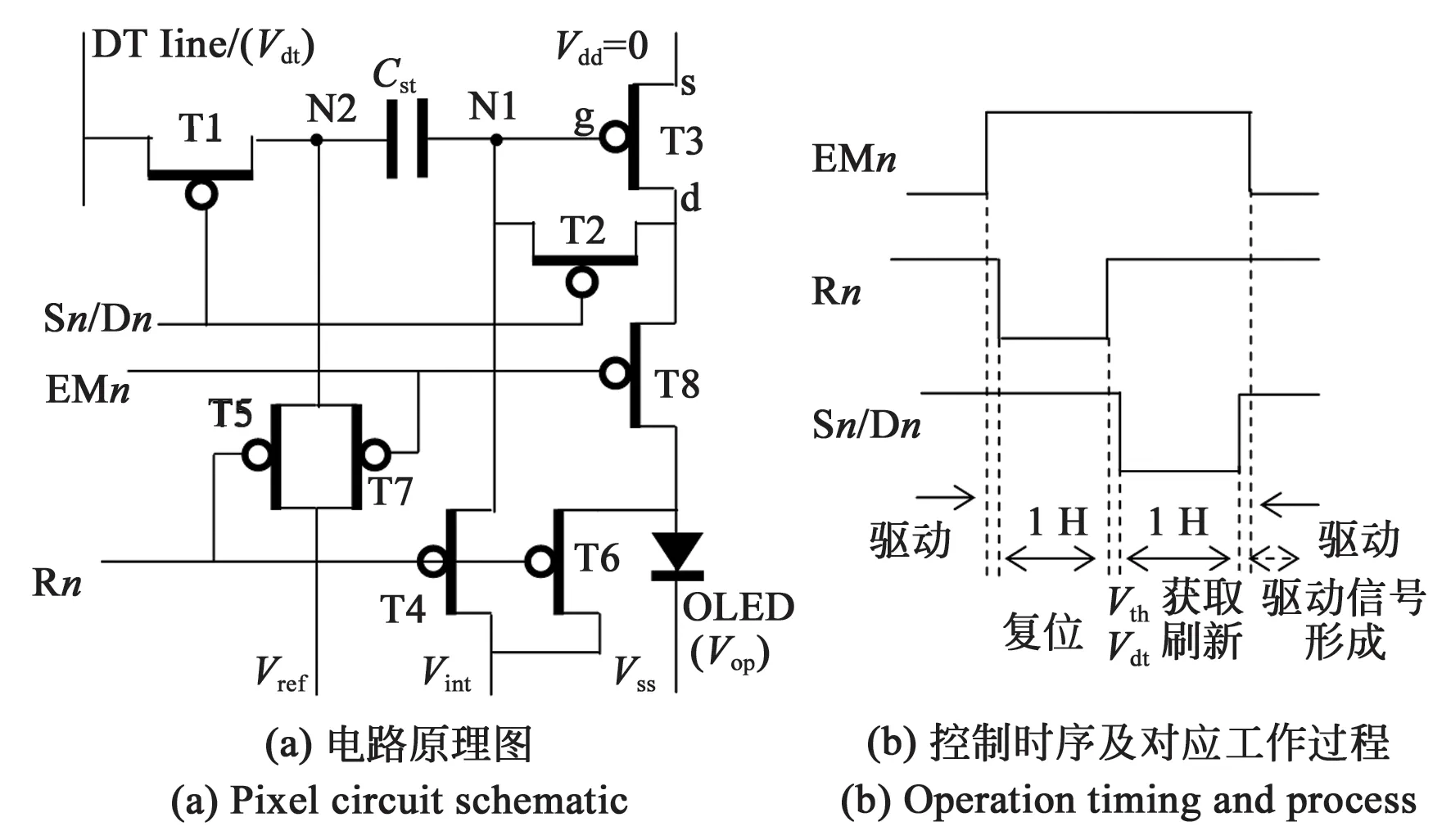

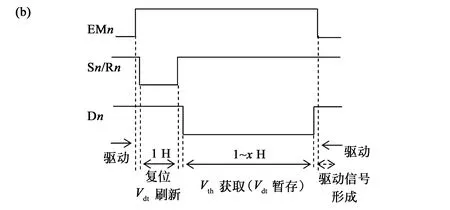

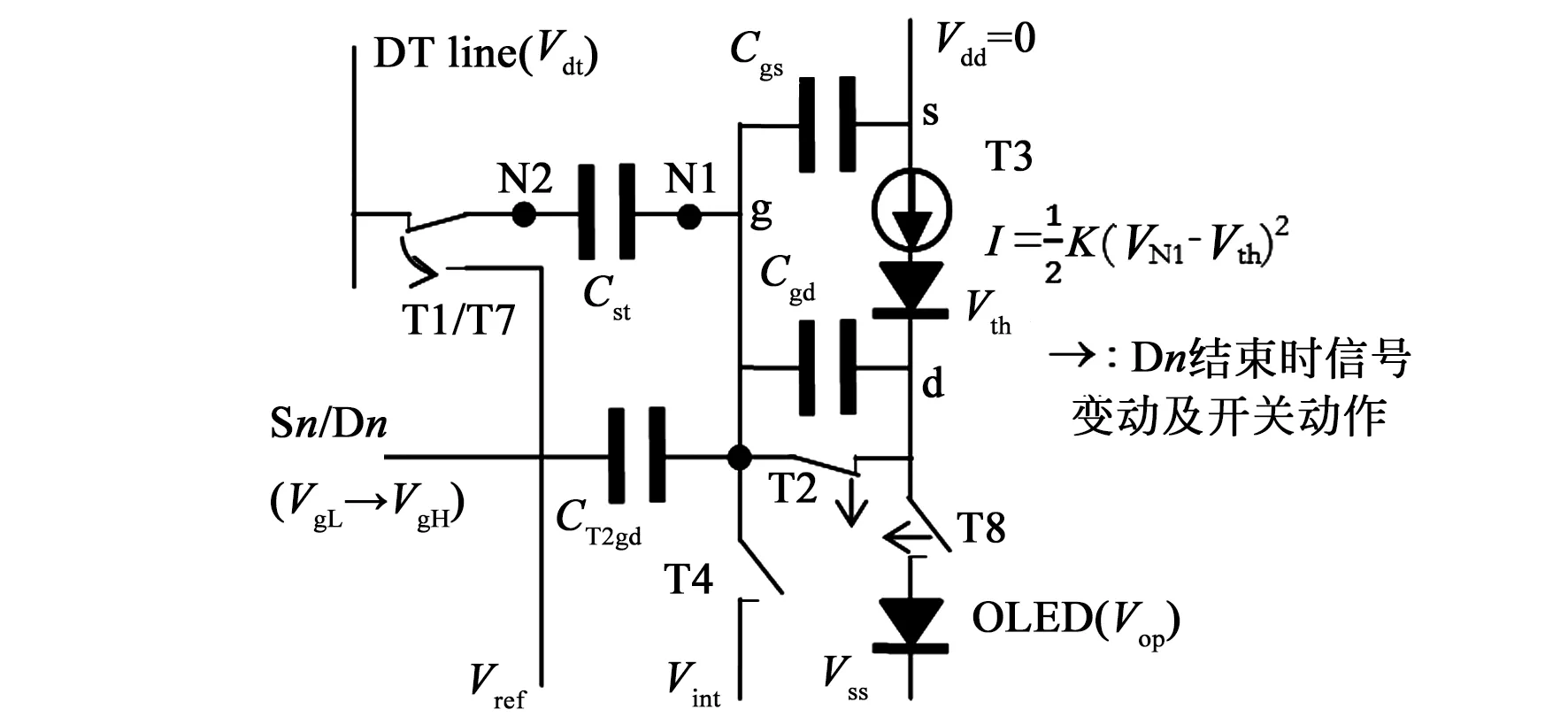

图1 一种电压型Vth补偿像素LTPS AMOLED像素电路Fig.1 Voltage-program LTPS AMOLED pixel circuit

图1是一种电压型Vth补偿像素电路,相关分析可以作为类似主流电压型LTPS AMOLED显示器像素电路工作过程的参考。在电路中,DT line为数据线(Data line),用于传输帧像素显示电压信号(Voltage Data,Vdt)。T3是输出像素OLED驱动电流的DTFT,其余TFT为开关TFT(Switch TFT,STFT),s、d、g分别表示TFT的源、漏和栅极。存储电容(Storage capacity,Cst)用于保持Vdt、Vth相关电位/电压信号,也是Vdt、Vth信号叠加及与基准电位耦合的电容,N1、N2为电容两端节点。像素OLED工作电压为Vop。Rn、Sn、Dn和EMn分别是第n行像素电路的复位(Reset)、Vdt刷新(Refresh)、Vth获取(Detection)和OLED驱动发光(Emission)时序控制信号。时序开始时控制信号由高电平跳变至低电平(VgH→VgL)的下降沿和结束时VgL→VgH的上升沿分别控制相关pMOS型STFT的导通和截止。Vint、Vref分别是初始化复位电位和信号基准电位,Vdd、Vss分别表示OLED驱动电源阳极和阴极电位。为叙述方便设定Vdd为整个电路的参考电位,即取Vdd=0 V。这样DTFT的栅、源间电压Vgs相关电位间形式上有等效关系:Vgs=VN1-Vdd=VN1。

这里以关键节点N1、N2电位变化为线索描述该电路帧周期的各个工作过程。时序Rn时,节点N1接Vint对Cst复位以消除前帧驱动信号的影响。时序Sn/Dn时,DT line通过节点N2对Cst充电,在节点N2获得像素显示信号Vdt电位,同时电源Vdd通过二极管短接DTFT(栅、源短接的DTFT可简化直流等效为压降Vth的二极管)和节点N1对Cst充电。如果充电时间充分,可在节点N1获取Vth电位。过程结束时,Cst电压为-Vdt+Vth(N1作为信号端,N2作为参考/基准端)。时序EMn时,节点N2接基准电位Vref,基于Vref和Cst上电压-Vdt+Vth在节点N1形成驱动电压信号Vref-Vdt+Vth,其中的Vth成分可以补偿DTFTVth变动性的影响。实际上,Vdt、Vth信号叠加并与基准电位Vref耦合形成驱动信号的过程是Sn/Dn结束时刻就启动的跨时序瞬态过程。考虑节点N1的各种寄生效应,这个瞬态过程不能在EMn时序开始瞬间完成,而是滞后一段时间才能稳定,形成的驱动信号也有所损失。驱动信号形成后,由Cst保持在节点N1,维持DTFT输出像素OLED驱动电流。

上述过程中,以分时占用数据线逐行扫描(Line Scan)方式进行的像素Vdt刷新并保持是有源矩阵显示电路构架的基本特征。驱动信号中精确的Vth成分是补偿效果的基础。Vth获取精度以及驱动信号形成过程中的Vth精度损失直接影响了其补偿效果。

3 Vth获取过程分析和精度改善

3.1 影响Vth获取精度的因素

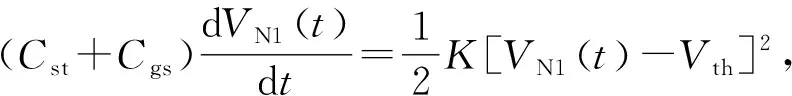

图2所示是图1像素电路Vth获取充电过程的等效电路,其中仅包含对Vth获取充电过程影响较大的因素,忽略了其他寄生效应的影响。Vth获取精度[10]分析需要考虑Vth获取相关电容充电过程中DTFT T3转移特性电流和节点N1电位(=Vgs)间的相互作用。相关电容不仅包括存储电容Cst,还包括与节点N1相连接的DTFT T3栅源电容Cgs。T3栅漏电容Cgd虽然也与节点N1相连,但充电过程中被T2短路不发生影响。二极管短接DTFT转移特性电流对相关电容充电时,节点N1电位VN1(t)满足微分方程:

图2 Vth获取充电过程等效电路Fig.2 Vth detection charging equivalent circuit

(1)

K是由结构参数决定的DTFT增益系数。需要说明的是TFT电容Cgs包含的沟道MOS电容成分随偏压变化问题[11]的处理。充电初期DTFT T3处于饱和工作区,Cgs沟道电容是强反型MOS电容;充电接近结束时,VN1接近Vth使DTFT沟道处于临界反型状态,Cgs沟道电容有微小降低,但变化数值小对充电过程影响不大。为突出核心过程,也假设Cgs为固定电容。

解微分方程(1),按图2中初始条件得到方程特解:

(2)

由式(2)可以直观理解得出结论:只要充电时间充分(t→∞),节点N1电位VN1(t)就会逼近Vth,即在节点N1获取精确的Vth。考虑到刷新扫描行周期限制,典型情况下相关电路Vth获取充电时间并不充分,尤其是在高分辨率、高帧频趋势下,行周期时间不断缩短造成了Vth获取精度劣化;另一方面,Vth获取充电与Vdt刷新充电共享Cst作为信号保持电容还会使Vth获取充电过程受不同Vdt电位影响,造成Vth获取精度不稳定。

3.2 关键因素检讨和改进对策

基于电路简洁性和像素电路布图(Layout)效率的考虑,多数实用电压型Vth补偿像素电路倾向以各种方式共享Cst作为Vth获取和Vdt刷新充电过程的信号保持电容。这种构架还可以直接在Cst上实现Vdt、Vth信号叠加。图1及文献[7]电路中Vdt、Vth分别以电容的两端作为信号获取端,跨Cst获取电压-Vdt+Vth;也有电路直接采用Vdt作为Vth获取充电电源[6,8],跨Cst获取电压Vdt+Vth。但这种构架也使两个信号获取过程关联同步,Vdt刷新扫描行周期成为Vth获取充电时间的硬性制约。

从电路各工作过程发生的前提和功能考虑,Vth获取充电过程不必依赖于Vdt信号。分离Vdt刷新充电和Vth获取充电过程,就有机会解决Vdt刷新扫描行周期对Vth获取充电持续时间的硬性制约。这种构架要求像素电路具有相互独立的Vdt、Vth信号保持单元,不仅可以使Vth获取充电过程持续充分长的时间,还能避免该过程受到不同Vdt信号电位的影响,确保Vth获取精度和稳定性。文献[12-13]像素电路核心部分具备上述特征,但其结构决定驱动保持期间DTFT栅极电位易受DT line信号波动的影响,实际应用存在串扰等显示品质制约。

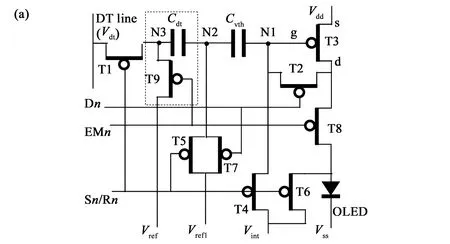

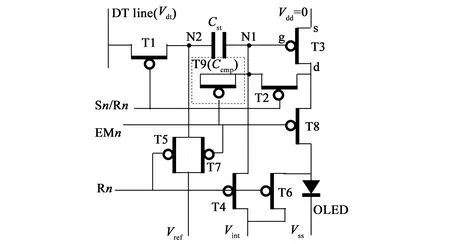

图3 Vdt刷新(a)和Vth获取(b)过程分离像素电路Fig.3 Pixel circuit of separated Vdt refreshing (a) and Vth detection (b)

图3是我们在图1像素电路的基础上提出的具有Cdt(虚线框内部分)、Cvth两个电容保持单元的像素电路,可以使Vdt刷新、Vth获取两个充电过程相互独立,Cdt、Cvth容量应大致相等。Vref1、Vref分别是复位和数据刷新、驱动信号形成和保持的参考电位和基准电位。该电路包含的工作过程与主流电压型像素电路大致相同,但利用互相独立的信号保持单元、相应STFT开关电路和时序控制信号,可以更合理地安排不同工作过程发生的顺序和持续时间。该电路节点N3接Vref,有利于屏蔽DT line信号波动对节点N1电位稳定性的影响。仍以关键节点N1、N2、N3电位变化为线索描述该电路帧周期包含的工作过程。时序Rn/Sn时,Cdt、Cvth共同端节点N2接参考电位,节点N1接Vint对Cvth复位,消除其中包含前帧驱动信号的影响,同时DT line通过节点N3对Cdt充电刷新Vdt信号,在节点N3获取Vdt电位。由于复位需要的时间较短,通常不会因行周期制约而影响复位品质。Dn时序时,二极管短接DTFT通过节点N1对Cvth充电。该过程中节点N3的Vdt电位由Cdt电容单元电路保持、不占用数据线,因此可以不受行周期限制而持续充分长的时间,从而在节点N1获取精确的Vth电位。Dn时序结束时,节点N2直流浮空,Cdt与Cth形成串联电容,两个电容上信号叠加形成串联电容电压-Vdt+Vth。这个串联电容在驱动信号形成和保持过程中的作用等效于图1电路中的保持电容Cst,所以也用Cst表述。时序EMn时,节点N3接基准电位Vref,基于Vref和串联电容Cst上电压-Vdt+Vth在节点N1形成驱动信号Vth+Vref-Vdt。之后驱动信号由串联Cst保持在节点N1,维持DTFT帧周期内输出像素OLED驱动电流。

更有利的电路工作过程顺序是设置专用的复位时序Rn启动复位过程,然后是时序Dn对应的Vth获取充电过程,在Dn结束时用时序Sn启动Vdt刷新过程。这种安排不仅可以避免复位过程受行周期制约,更可以避免Vth获取充电过程中节点N3保持的Vdt电位因负面寄生效应而发生精度损失。代价是增设一条专用的Rn时序控制信号线。

3.3 Vth获取充电过程持续时间延长的效果

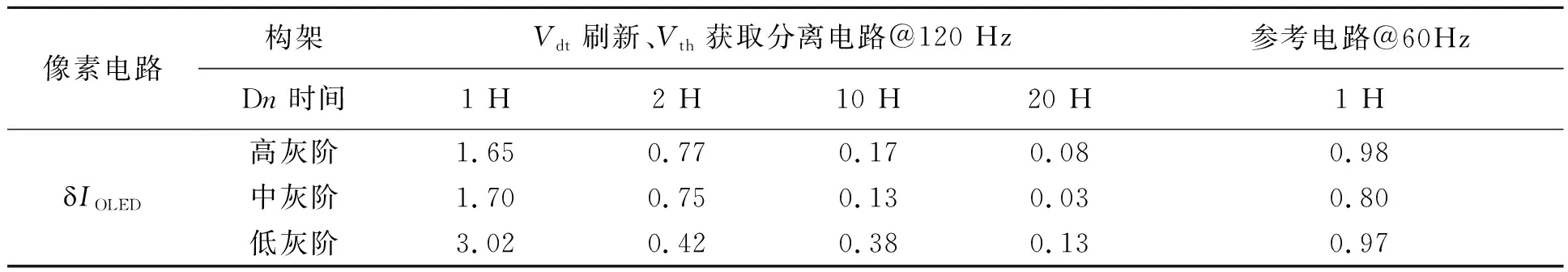

我们基于图3中Vdt刷新、Vth获取过程分离像素电路构架,按一种典型应用情况进行量化设计,同时采用图1中电路构架进行相应设计作为参考。假设LTPS-TFTVth变动为δVth=0.5 V,模拟不同构架和设置像素电路像素OLED驱动电流的相对变动幅度δIOLED,评价其Vth变动性补偿效果,参见表1。

表1 δVth=0.5 V时OLED驱动电流变动性δIOLED模拟Tab.1 Simulation result of δ Ioled variation on δVth=0.5 V (%)

表1中Dn表示时序持续时间,单位H是扫描行周期,参见图1(b)、图3(b)。随着Dn时序持续时间的加长,过程分离电路构架像素电路Vth变动对OLED驱动电流的影响逐步减弱,大约在20 H左右,就可以认为Vth变动性的影响基本被补偿抑制;参考电路构架的像素电路只能以1 H(60 Hz帧频1 H时间相当于120 Hz帧频2 H)持续时间充电获取Vth,其补偿能力与过程分离电路Dn时序持续2 H结果相似,远达不到理想水平。

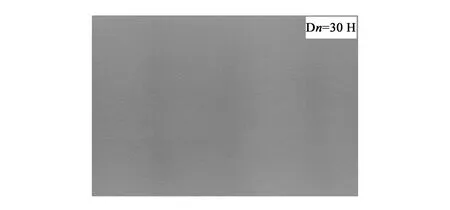

(a)Vth获取充电时间充分(Dn=30 H) Mura效果(a) Mura state with sufficient Vth detection time (Dn=30 H)

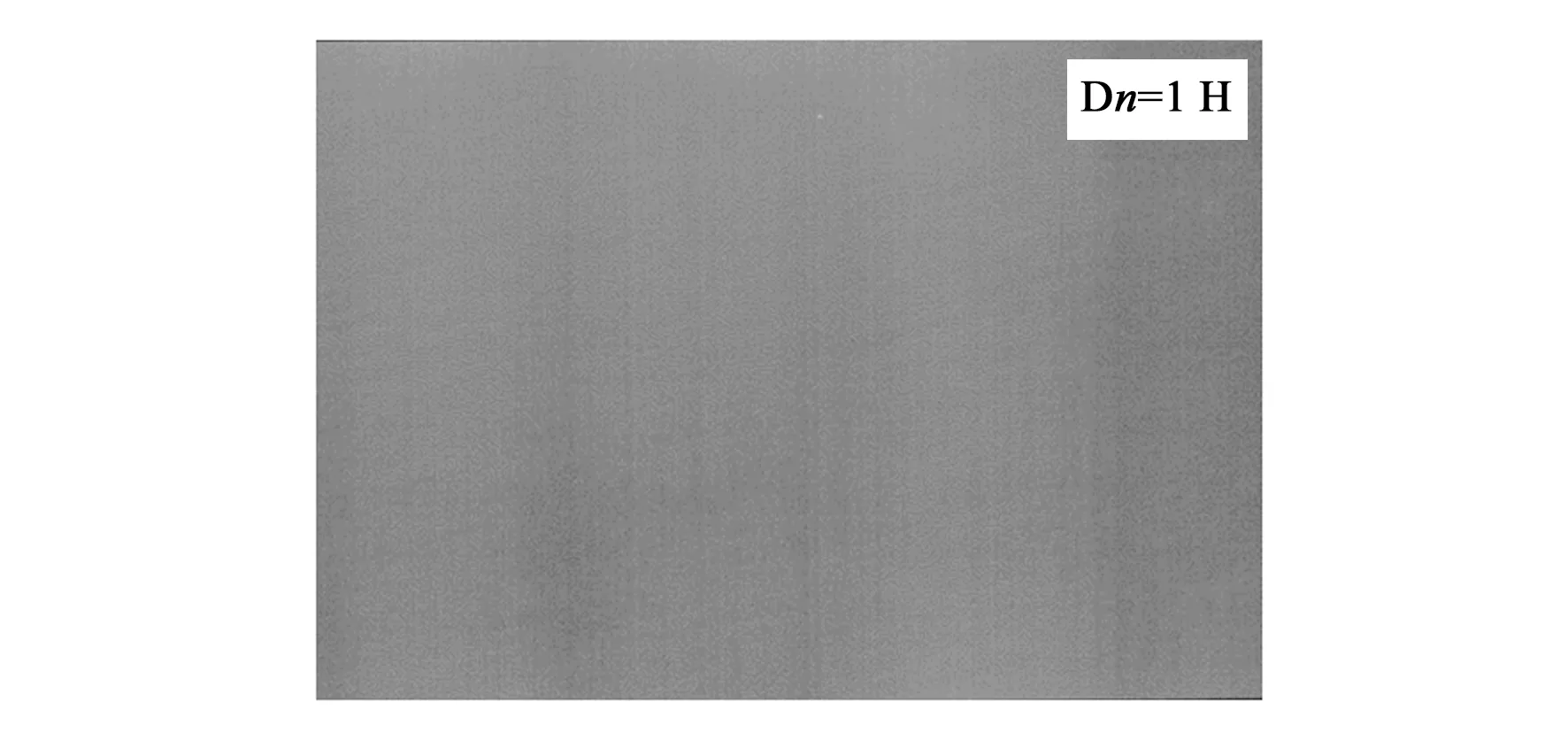

(b) Vth获取充电时间同行周期(Dn=1 H) Mura效果(b) Mura state with line scan period Vth detection (Dn=1 H) 图4 像素电路不同Dn设置低灰阶均匀场补偿效果对比Fig.4 Vth compensation effect on low grey uniform field of various Dn time

我们按过程分离像素电路构架量化设计制作了显示器样品以验证改善效果。图4是样品以120 Hz帧频显示低灰阶白平衡均匀场时的Mura缺陷效果照片。术语Mura表示与显示内容无关没有明显边界的画面不均匀形貌特征。选择低灰阶场景是因为Mura通常在低灰阶下更容易显现。为便于辨识,影像的亮度做了统一的调整。实际上,弱Mura缺陷通过照片进行评价是困难的,图4中Mura对比仅有相对和参考意义。本文样品评价的结论主要是通过直接的视觉评价得出的。

图4照片(a)样品Dn时序持续时间设置为30 H,即Vth获取充电时间充分;照片(b)是同一样品Dn时序持续时间设置为1 H,即Vth获取充电时间与行周期相同。可以看到当Vth补偿充电时间充分时,Mura缺陷被明显抑制。照片4(b)中细竖条纹Mura是LTPS准分子激光退火工艺产生的典型缺陷形貌特征,这种缺陷也是Vth变动性的主要原因。随着Dn时序持续时间的加长,Vth获取充电时间充分的样品相关Mura显著减弱,说明Vth变动对OLED驱动电流的影响被电路补偿抑制了。

4 驱动信号形成瞬态过程中Vth精度损失和对策

4.1 时序转换中电路状态分析

这里假设Vth获取充电过程结束前在节点N1获取的Vth是精确的,以便重点关注之后的精度损失。仍以相对简单的图1中像素电路进行相关问题分析。Dn/Sn时序结束时,Vth获取充电通路上的STFT T2截止。接下来EMn时序控制节点N2由Dn/Sn时序结束时的电位Vdt转接到基准电位Vref,Vdt、Vth信号及基准电位Vref耦合在节点N1形成驱动信号。这个涉及两个时序转换的瞬态过程可以用图5所示等效电路描述。等效电路仅包含对DTFT驱动信号形成瞬态过程影响较大的因素,忽略了其他寄生效应的影响。与节点N1相关DTFT T3栅源、栅漏电容Cgs、Cgd和STFT T2栅漏电容CT2gd包含了半导体MOS电容性质的沟道电容,其容量随偏压而变化[11]。为表述方便,这里把因相关节点电位跳变随偏压变化后的TFT栅源、栅漏电容用上标“+”标识。

图5 Vth获取过程结束时刻等效电路图Fig.5 Equivalent circuit of transition status at the end of Vth detection

时序转换瞬态过程前后,节点N1、N2及其他相关节点的电位变动不仅造成电荷在节点N1相关电容间重新分配,也使相关TFT沟道电容发生变化影响电荷再分配的结果。根据电荷量守恒原理,相关节点电位跳变前后,与节点N1连接的Cst和其他电容间电荷分配满足守恒方程:

δQN1=δQst+δQgs+δQgd+δQT2gd=0,

(3)

解方程(3)得在节点N1Vdt、Vth叠加后形成的驱动信号电位:

(4)

式(4)中等号右侧第1项为驱动信号中目标Vth成分,用以补偿Vth变动性的影响。第3项为目标Vdt信号成分,用以控制像素OLED驱动电流。第2、4项分别表示由于相关TFT电容增量对驱动信号中Vth、Vdt成分造成的摊薄等效应。第5项是相关电容增量和其他节点电位跳变耦合造成的节点N1电位平移。其中,第4、5两项表示的Vdt相关精度损失和平移可以通过Vdt信号修正补偿,我们仅关注Vth相关的第2项,即Vth的精度损失Vthls,单独表示为:

(5)

4.2 造成转换过程Vth精度损失的因素和对策

式(5)右侧项分子涉及的因素,反映了造成Vth精度损失的直接原因,形式上是节点N1相连接电容整体增量。其中CT2gd+-CT2gd是STFT T2栅漏沟道电容从导通态变为截止态的增量。这个过程中STFT T2导电沟道消失,沟道电容为负增量。模拟研究表明,这一负增量幅度较大,对Vth精度损失有突出的影响。MOS开关器件这种状态转换过程中沟道电容变动造成的信号精度损失,IC技术称为开关误差(Switching Induced Error)[14]。

式(5)中Cgs+-Cgs表示DTFT T3栅源沟道电容从Vth获取过程结束时临界截止状态转换到驱动信号偏置输出像素OLED驱动电流状态的增量。另外,Vth获取过程中栅漏电容Cgd被短路而无存储电荷,获取过程结束时整个Cgd+被释放成为增量电容(包括沟道电容成分和固定寄生电容成分等)[15]。模拟研究表明T3沟道电容在时序转换中偏压及变化幅度不大,Cgd固定寄生电容也较小,DTFT T3相关电容增量及其影响较小。

时序转换过程中与节点N1连接的STFT T2、DTFT T3相关电容总增量是负值。为补偿其影响,需要在节点N1曾设一个正增量的MOS补偿电容Ccmp,以便使下列关系成立:

(6)

如果利用相同的像素电路基板制作工艺流程制作pMOS沟道电容Ccmp进行补偿,则有Dn时序信号反向电平偏置,或pMOS沟道电容反向连接、Dn时序信号同向电平偏置2种对策方案,实质上是利用补偿TFT的反向开关误差补偿STFT T2开关误差[16]及其他误差。

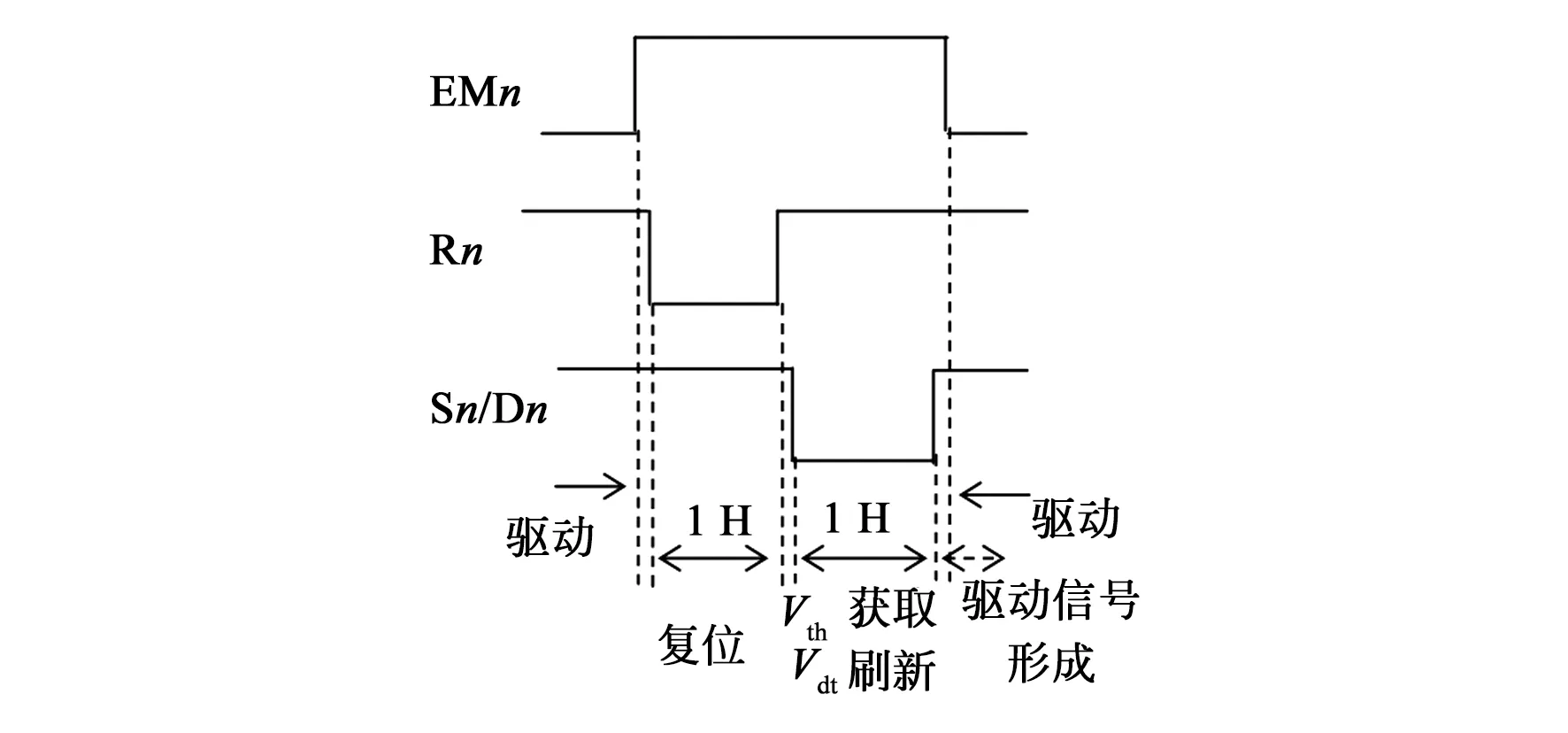

(a) 电路原理图(a) Pixel circuit schematic

(b) 控制时序及对应工作过程(b) Operation timing and process图6 Vth获取过程结束时STFT T2开关误差补偿Fig.6 Compensation for STFT T2 switching error at the end of Vth detection

图6是Dn时序信号反向电平偏置pMOS补偿电容对时序转换中Vth精度损失进行补偿的电路对策方案。虚线框中补偿TFT T9电容CT9gs+CT9gd等效为补偿电容Ccmp,利用EMn时序信号电平作为Dn时序信号反向电平偏置。T9沟道电容在EM时序开始与T2沟道电容在Sn时序结束偏置变动幅度相同、方向相反,通过T9适当的结构参数设计,可以使其沟道电容变化Ccmp+-Ccmp抵消T2、T3相关电容大部分增量,即式(6)近似成立,补偿STFT T2截止过程的开关误差及部分DTFT T3电容增量造成的误差。

4.3 补偿STFT开关误差的电路对策效果

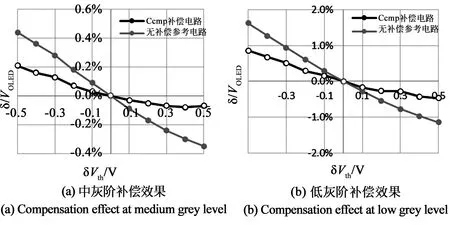

图7是通过补偿电容Ccmp对增量电容造成的Vth精度损失进行补偿效果的模拟曲线,包括视觉相对敏感的中、低灰阶两种状态,帧频设定为60 Hz。在相同的Vth变动幅度δVth下,有Ccmp补偿电路Vth精度损失造成的驱动电流变动幅度δIOLED明显被抑制。

图7 TFT电容增量补偿效果模拟评价Fig.7 Simulation of TFT capacity increment compensation effect

模拟结果表明,只要补偿TFT(Ccmp)设计适当,δIOLED-δVth曲线就会充分接近水平坐标轴,即δIOLED充分小。但由于δIOLED-δVth关系本身是非线性的,补偿不能完全抑制Vth变动性对IOLED的影响。非线性的δIOLED-δVth关系的原因是:时序转换过程中,DTFT T3沟道电容的偏压Vgs、Vds变动幅度与Vdt相关,中、低灰阶下小幅度Vdt信号产生的Cgs、Cgd增量随Vdt变化而变化,而时序信号偏置大幅度变动|VgH-VgL|造成的CT2gd、Ccmp增量则几乎是固定的[11],因此式(6)无法在不同灰阶显示信号Vdt下都严格成立。这意味着,通过反向开关误差虽然可以较好地补偿影响较大的STFT T2截止时的开关误差,但无法完全补偿DTFT T3沟道电容增量等造成的Vth精度损失。

(a) 有电容增量补偿电路低灰阶Mura效果(a) Low grey level Mura with capacity increment compensation

(b) 无电容增量补偿参考电路低灰阶Mura效果(b) Low grey level Mura without capacity increment compensation 图8 电容增量补偿效果样品对比Fig.8 Effect of TFT capacity increment compen-sation through sample comparison

图8照片(a)是有电容增量补偿像素电路样品显示低灰阶白平衡均匀场的Mura缺陷效果,照片(b)是无电容增量补偿参考像素电路样品的效果,照片(a)中有补偿像素电路样品的Mura相对较轻。由于工艺、设计和工作状态的差异,图8中Mura形貌的方向性等特征与图4不同。

5 结 论

Vth空间变动性补偿效果是LTPS AMOLED显示器像素电路的关键特性。在AMOLED显示高分辨率、高帧频趋势下Vth补偿效果劣化。本文根据相关像素电路工作过程分析结果,提出了延长Vth获取充电时间、补偿相关TFT电容增量误差的电路改进对策,改进的电路对Vth补偿有良好的改善效果。针对像素OLED驱动电流受Vth变动影响突出的低灰阶状态,模拟结果表明Vth获取和Vdt刷新过程分离像素电路的OLED驱动电流变动降低为参考电路的1/7以下;反向增量电容补偿像素电路OLED驱动电流变动大约为与无补偿参考电路的1/2。样品视觉评价结果与模拟结果趋势相符。考虑到不同灰阶和更多样品的整体状态,改善像素电路样品的相关显示品质可以达到实际应用可接受以上水平。

本文所述的Vth补偿效果改善对策仍然存在一些问题。其中Vth补偿充电、Vdt刷新充电过程分离像素电路中,由Cdt、Cvth串联形成的Cst电容值折损大,像素电路需要更大的布图面积,造成高分辨率像素电路布图困难;反向STFT开关误差补偿也不能完全补偿像素电路驱动信号形成过程中Vth精度损失。但这些问题并没有掩盖核心技术概念的改善效果,只要持续改进、逐步优化,就有机会使技术概念的优越性在应用中显现。