基于电流模逻辑的宽频带二分频器设计

张 博,王好博,杨 朋,吴昊谦

(西安邮电大学 电子工程学院,陕西 西安 710121)

随着无线通信系统在相关领域的迅速发展,越来越多的无线通信标准协议得到广泛的应用[1-2]。频率综合器是收发机电路的重要组成部分,分频器广泛应用于锁相环频率综合器的反馈回路,其作用是对压控振荡器(Voltage-Controlled Oscillator,VCO)输出的高频信号进行降频、拓宽频率输出范围且输出正交信号[2-3]。近年来,随着不同应用环境的出现及新的无线标准的提出,对锁相环频率综合器的工作频率范围提出了更高的要求,相应的对能够实现宽频率覆盖范围的频率综合器芯片的需求也越来越迫切。分频器电路直接决定了频率源的输出频段,如何提高分频器的频率覆盖范围成了目前研究的一个重点。

二分频器是所有分频器的基本组成模块,目前常见的二分频器电路结构有注入锁定结构、单向时钟结构、电流模逻辑结构(Current Mode Logic,CML)等。齐骋等[3]利用CML 的衍生结构,设计了一个正交二分频器,电路的工作频率为200 MHz~2.8 GHz,在3 V 电源电压下功耗为1.15 mW;Lai 等[4]采用注入锁定结构设计了一个正交二分频器,电路的工作频率为3.4~9 GHz,功耗为20.4 mW,尺寸为1100 μm×1000 μm。虽然工作频率有所拓宽,但是由于加入了电感元件,功耗和面积明显增大。

本文采用改进的CML 电路结构,针对分频器工作频率范围窄、CML 电路自身很难工作在低频段的问题,设计了一种能够实现200 MHz~11 GHz 频率覆盖范围的分频器。电路在传统的CML 结构上加以改进,采用无尾电流源的CML 结构,并使用电阻作负载,同时加入了耦合电容和偏置电阻,提高了分频器的响应速度。在两级CML 电路中加入开关电容阵列,使得分频器在不同的工作频率下切换对应的电容负载,解决了CML 电路不能工作在低频的问题,进而拓宽了分频器的工作频率范围,减少了开关管的使用,降低了芯片的面积和功耗。

1 二分频器电路设计

1.1 CML 电路设计

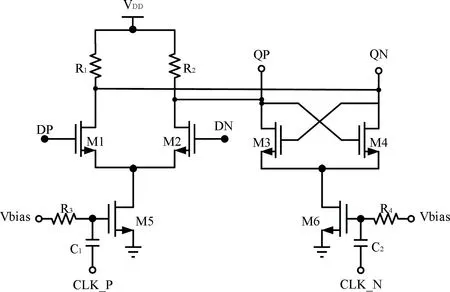

本文设计的CML 电路原理图如图1 所示。其中,MOS 管M1、M2 为采样对管,所在支路构成CML 的采样支路;MOS 管M3、M4 为交叉耦合对管,所在支路构成CML 的锁存支路;R1、R2为负载电阻,也叫上拉电阻,R3、R4为偏置电阻,C1、C2为耦合电容[5]。其工作原理为:当差分输入信号CLK_P 为高电平且CLK_N 为低电平时,M5 导通,电流被全部导向采样级,输入端的数据直接反映到输出,即CML 电路工作在“采样模式”;当差分输入信号CLK_P 为低电平且CLK_N 为高电平时,M6 导通,电流全部导向锁存级,CML 电路工作在“保持模式”。交叉耦合管不仅为环形电路提供负阻,确保电路能保持振荡,而且形成了正反馈结构,保持住前一阶段采样的数据,使得输入信号对输出没有影响,从而在一个周期内完成信号的采样和保持,实现CML 电路结构的锁存功能。所以CML 电路也被称为锁存器电路[6-7]。

图1 CML 电路原理图Fig.1 CML circuit schematic

电路在基础的CML 结构上加入了偏置电路,若M5 和M6 直接与时钟信号CLK 相连,则偏置电流和电路输出的摆幅将在很大程度上取决于PVT 条件。输入时钟振幅会产生不同程度的衰减,电阻R3和R4与电容C1和C2产生的时间常数比时钟周期长得多,因此可以最小化时钟振幅的衰减,耦合电容的取值一般为门电容M5 和M6 的5~10 倍[8]。在此电路结构中,MOS 管M5、M6 的峰值电流远远超过其偏置电流,此特性能有效提高二分频器的响应速度。

不同的CML 电路主要体现在负载和尾电流源上。常用的负载有电阻和PMOS 管。采用二极管连接的PMOS 管作为负载或者采用工作在线性区的PMOS 管作为负载会使输出信号幅度降低,且充放电速度变慢,不适合应用在高频的快速分频电路中。选择电阻作为负载可以提高分频器的响应速度,使输出接近满摆幅。有尾电流源的结构在一个时钟周期内消耗的电流恒定,且时钟输入管的直流偏置容易调节,但电路的切换受尾电流源的影响,工作速度大幅降低。与有尾电流源结构相比,无尾电流源结构可以达到更高的工作速度,具有更好的相位噪声性能。通过在时钟管的栅极串联偏置电阻,使得上级的时钟输入信号通过电容交流耦合到栅极,从而解决直流电平难配置的问题。为了满足更高的频率要求,本设计采用无尾电流源偏置的电阻负载结构。

对于CML 结构组成的二分频器而言,其工作频率与自谐振频率有关,自谐振频率是指由于电路相当于环形振荡器的闭环负反馈系统,自身会发生振荡,即不施加输入时钟信号CLK,仍然会有信号输出。其自谐振频率fosc为:

式中:gm为采样管M1、M2 的跨导;CL为CML 电路所有输出节点的寄生电容。根据自谐振频率公式可以反映出,增大采样管的跨导或者减小输出节点的寄生电容都可以提高电路的自谐振频率。虽然自谐振频率与R(R1和R2的总电阻)无关,但R的大小决定了电路能否起振[9-11]。主要取决于交叉耦合管,交叉耦合管为电路提供负阻,从而和正电阻抵消,保证电路环路增益始终大于1,所以起振条件应保证:gm,34× R >1,其中,gm,34为MOS 管M3 和M4 的跨导。

1.2 开关电容阵列电路设计

本文设计的开关电容阵列电路原理图如图2 所示,其中包括MOS 管M10 和M11 组成的反相器,提供电平的转换并作为隔离数字电路和模拟电路的缓冲级;R5和R6为分压电阻;MOS 管M7 作为开关,用来控制C3和C4是否接入电路;MOS 管M8 和M9 的作用相当于电阻,由于M8、M9 的源极接地,导通时将M7 的漏极与源极电位拉至低电平,使得M7 工作在深线性区。电路工作原理:当S0为低电平时,M7 管导通,电容C3和C4接入CML 电路的输出端口;当S0为高电平时,M7 管关断,电容C3和C4不接入CML电路。

图2 电容阵列电路原理图Fig.2 Capacitor array schematic

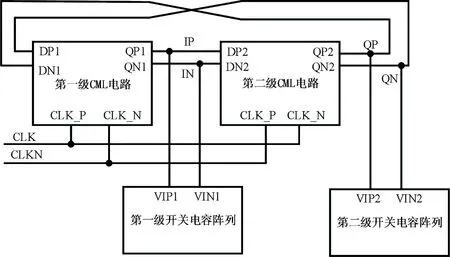

1.3 宽频带二分频器电路设计

根据D 触发器构成二分频器原理可知,将两个CML 电路级联,并把后一级的输出端Q 连接到前一级的输入端D,即构成了差分输入和差分输出的二分频器。二分频器电路的整体框图如图3 所示。其中包括两级相同的CML 电路和两级相同的开关电容阵列。在每级CML 结构的输出端加入开关电容阵列,通过开关切换不同的电容负载来确保二分频器在不同频带内均能稳定工作。其中,第一级电路信号输出端分别与第二级电路的输入端相连接;第二级电路的信号输出端QP2 和QN2 分别与第一级CML 电路的信号输入端DN1 和DP1 相连接。第一级电路的信号输出端IP 和IN 分别与第一级开关电容阵列的差分输入端相连接;第二级电路的信号输出端QP2 和QN2 分别与第二级开关电容阵列差分输入端相连接;两级CML 电路的信号输入端CLK_P 和CLK_N 相互连接。第一级开关电容阵列接S0,第二级开关电容阵列接S1。S0和S1为比特数字信号[1 ∶0]控制端。当[S0∶S1]=[0 ∶0]时,电容阵列接入电路,此时电路可稳定工作在较低频段;当[S0∶S1]=[1 ∶1]时,电容阵列不接入电路,电路负载电容为开关管的寄生电容可忽略不计,此时电路稳定工作在较高频段范围。

图3 宽频带二分频器电路结构框图Fig.3 Wideband divide-by-2 frequency divider circuit structure

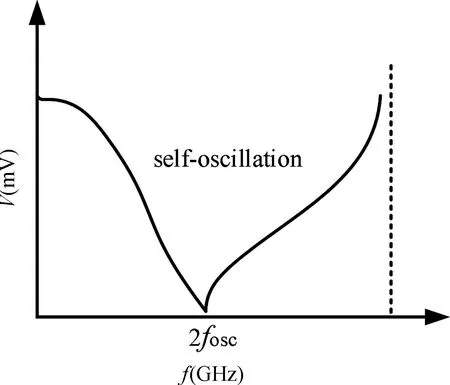

高速二分频器的典型特征是把所需的最小时钟电压摆幅(灵敏度)映射成时钟频率的函数[12]。分频器电路通常使用输入灵敏度曲线来分析其动态特性。如图4 所示为分频器电路的输入灵敏度曲线,其中横坐标为输入频率,纵坐标为分频器正常工作所需的最小幅度。在时钟频率fclk=2fosc处,电路正常工作所需的输入摆幅最小,此时分频器电路相当于自由振荡在fosc处的环形振荡器,当时钟频率偏离2fosc时,需要提高输入信号幅度使电路正常工作。

由图4 可知,输入时钟信号的摆幅越小,则电路正常工作的频率范围越小,因此要达到大的工作频率,输入时钟信号幅度必须较大。一般VCO 输出摆幅都比较大,对于跟在VCO 后面的分频器,其输入时钟的摆幅往往不成问题[13-16]。

图4 电路的输入灵敏度曲线Fig.4 Input sensitivity curve of circuit

2 版图设计及电路仿真

宽频带二分频电路核心版图如图5 所示。电路设计及版图采用TSMC 0.18 μm RF CMOS 工艺。由于CML 电路为全差分结构,电路版图设计中首要考虑电路的对称与匹配,高频线采用上层金属线以减少寄生电容对电路的影响。该分频器版图尺寸仅为256 μm×126 μm。

图5 电路版图Fig.5 Circuit layout

经后仿真验证,此分频器的最高工作频率可达11 GHz,最低工作频率低至200 MHz,实现了从低频段到高频段的超宽频率范围。此分频器的工作电压为1.8 V,消耗电流为3.58 mA。

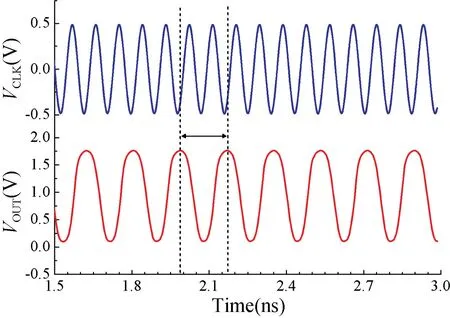

当[S0∶S1]=[1 ∶1]时,输入时钟信号幅值500 mV,频率为11 GHz 下,此宽频带二分频器的波形图如图6 所示;当[S0∶S1]=[0 ∶0]时,输入时钟信号幅值500 mV,频率为200 MHz 下,此宽频带二分频器的波形图如图7 所示。

图6 输入时钟频率11 GHz 下的二分频仿真图Fig.6 Simulation result of divide-by-2 frequency divider at 11 GHz clock input

图7 输入时钟频率200 MHz 下的二分频仿真图Fig.7 Simulation result of divider by-2 at 200 MHz clock input

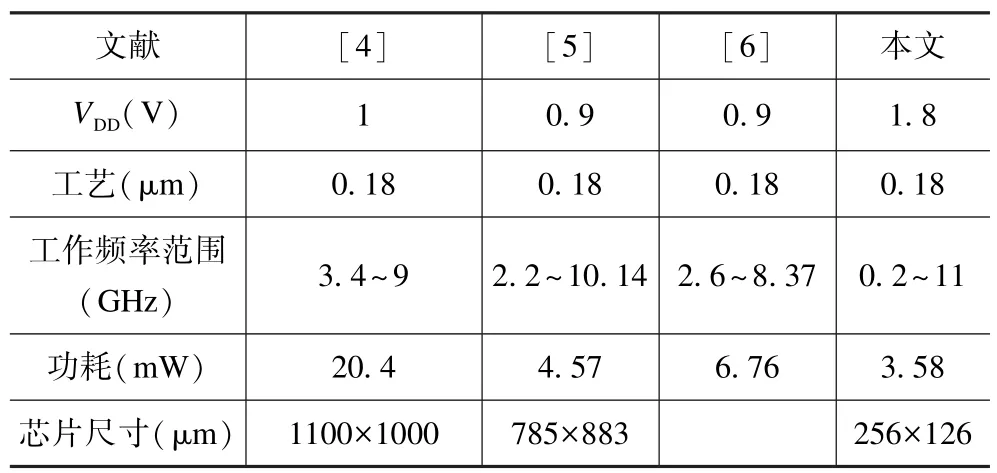

表1 为该二分频器与其他文献二分频器的性能对比。从表1 可以看出,在相同的工艺下,本文设计的二分频器工作频率范围更宽,功耗更低,面积更小,性能更优。

表1 二分频器性能对比Tab.1 Performance comparison of divide-by-2

3 结论

本文设计了一种基于CML 结构的宽频带二分频器电路,电路在传统的CML 结构中加入了偏置电路,提高了CML 的工作速度。在每级CML 结构的输出端加入开关电容阵列,通过控制位开关切换不同的电容负载,使得分频器电路可以稳定工作在低频,从而拓宽了二分频器的工作频率范围。仿真结果表明,该二分频器在输入时钟频率200 MHz~11 GHz 下均能实现正常的二分频功能,极大地拓宽了电路的分频范围,降低了功耗,减少了面积,性能优于传统的二分频器。