基于FPGA的超宽带数字波束形成技术

顾明超,李春晓,边 疆,张汉卿

(1.中国电子科技集团公司第五十四研究所,河北 石家庄050081;2.河北省电磁频谱认知与管控重点实验室,河北 石家庄050081)

0 引言

相控阵技术是近年发展迅速的前沿热点技术之一,早先应用于雷达探测技术,多为窄带阵列处理体制[1],典型带宽值为几兆赫兹至几十兆赫兹。随着技术推广,目前已经逐步应用到电子对抗系统中,瞬时带宽也要求到几百兆赫兹甚至更高。2020年12月中国工程院发布的信息与电子工程领域技术前沿,相控阵技术在该领域10项前沿工程技术中占据两席,足以说明相控阵体制的技术先进性,对其关键技术工程化研究应用具有一定紧迫性,本文主要介绍其关键技术之一的超宽带数字波束形成技术的原理与其在FPGA中实现过程。

相控阵技术从有源放大和波控单元的位置区分,可分为无源和有源相控阵;从波束形成方式区分,可分为模拟波束合成、数字波束合成以及模数混合波束合成;从技术发展角度看,相控阵从无源发展到有源,从模拟发展到数字架构。数字波束形成是相控阵领域中的一个关键技术,其本质是一种数字化空域滤波,增强特定方位入射到阵列的信号,提高信噪比,抑制其他方向的干扰与噪声,为之后信号处理提供必要条件。在电子对抗领域,若能形成多个指向可变的宽带数字波束密集覆盖敏感区域,通过多波束并行侦察方式,势必能提高电子侦察系统的信号截获概率。

电子对抗中对宽带没有明确定义,一般认为信号带宽与中心频率之比小于1%时,为窄带信号;大于1%小于25%时,为宽带信号;若带宽与中心频率的比值大于25%,为超宽带(UWB)信号[2]。在电子对抗领域,由于为非合作接收方式,不明确信号调制类型和带宽以及持续时间,需通过高速ADC采集瞬时覆盖目标频段,再通过宽带侦察和信道化检测等措施对信号参数进行测量。目前瞬时带宽典型应用范围为300 MHz及以下,瞬时覆盖500 MHz到GHz带宽的需求也将日益增多[3]。

Xilinx公司Virtex-7系列的大容量FPGA是一类性价比高且应用较广的芯片。这个系列FPGA有数量众多的逻辑/存储资源以及较为丰富的乘法器和数量众多的高速串行总线接口,非常适合于超宽带数字多波束的技术验证。

1 数字波束形成实现原理

1.1 数字波束合成原理

本文主要讨论信号接收波束形成,不涉及发射波束。早期的波束合成往往采用模拟移相的方式对多路模拟信号进行移相后合路,由于模拟移相器在宽频带中具有“非色散”特性,对覆盖频带中各频点移相值一样,应用于窄带信号的合成效果较为理想。但是对于电子侦察而言,瞬时覆盖带宽高达几百MHz甚至GHz,由于天线孔径效应的存在,导致宽带波束方向与理想方向产生偏差,瞬时带宽越大,天线的孔径效应越明显[4]。模拟信号移相合成方式已经不能满足宽带合成需求,必须采用宽带数字校准合成技术实现对多阵元宽带数据流的处理。

在阵列信号接收过程中,辐射源发出的目标信号在空间传输后到达接收阵列天线的各阵元,由于天线阵元的位置差异导致其接收信号的波程差异,因此各阵元的输出信号存在一定的相对时间延迟。对各阵元接收信号的时延做出补偿,让经过补偿后的各个输出信号在所期望的空间方向上幅度为同向相加,则此时可以最大化指定方向的波束输出信号幅度,并且使其他方向上的波束幅值相应变小,由此对非期望方向上的无用信号起到了抑制作用,用时域滤波处理方式达到了空域滤波的效果,这也是数字波束合成的一般性原理。

下面以均匀线阵、单音信号输入为例进行说明,相邻两个阵元间隔为d,如图1所示。

图1 信号入射均匀线阵示意图Fig.1 Schematic diagram of signal incident uniform linear array

假设阵元1为相位参考,来波方向与法线方向夹角为θ,c为光速,各阵元的时延表达式为[5]:

(1)

则各阵元相位差如式(2)所示:

(2)

若采样率为fs,则整数时延就近取整后,整数延迟值计算如式(3)所示:

Lint=round(τi·fs)。

(3)

分数时延计算如式(4)所示:

Lfraction=τi·fs-round(τi·fs)。

(4)

式(1)~(4)的推导隐含了一个重要前提,即各阵元接收到数字化过程的通道一致性是理想的,但实际情况并非如此,需要校准源产生扫频或梳状谱信号作为阵列接收模块的输入激励,对通道一致性进行校准,再按上述分析过程进行合成处理。

通道间不一致包括在法线方向时,各阵元接收信号时延不一致和通道间非线性相位差异,时延不一致可分解为整数采样点和分数点延迟,整数采样点可通过采样点校准在FPGA中对数据缓存或移位寄存器实现,分数点延迟和非线性相位差异可以与波束合成功能的分数点延迟功能进行合并,通过频域实现,这种组合实现方式有利于降低硬件实现的复杂度和资源消耗。

1.2 宽带数字波束合成实现过程

一般阵列处理系统包含阵列天线、模拟信道、数字处理和软件控制席位四部分。波束控制由软件席位控制模拟信道和数字部分电路完成。简化框图如图2所示。

在图2中,若ADC采样率足够高,采用射频直接采样体制接收覆盖目标频段,各阵元接收的多通道射频信号经过滤波放大后进入高速ADC完成模数转换,通过实采样校准和数字延迟滤波完成波束合成功能,或者实采样信号通过宽带变频滤波后形成多相结构的零中频数据流,再经过宽带复校准和数字复合成滤波计算后,完成宽带数字波束合成功能。

宽带侦察系统中,除了要求形成宽带波束,往往还采用宽带侦察引导窄带测向的方式,需要形成多个窄带波束进行控守,只需按照阵列模型和频点计算合成系数,再与按中心频点计算的通道间相位校准系数相乘,通过窄带滤波后的乘加运算完成信号合成功能。

2 宽带数字波束合成实现过程

波束合成的实现可分为时域法和频域法,无论哪种方法,预处理包含的采样同步、采样点校准都是必须的,都是DSP通过回读FPGA内同步存储的多路数据,经过校准和合成算法,将计算后系数写入FPGA中[6]进行后续运算。时域法和频域法均可实现宽带数字波束,处理方法的选择主要取决于波束数量、硬件资源消耗与系统成本。

2.1 时域合成法

宽带波束形成时域实现常见的有FIR滤波器实现、基于Farrow的分数点延时法和微波光子技术的时延方法。Farrow结构[7]可实现任意分数点延迟,延迟改变只需更改输入参数即可,延迟精度取决于相数和阶数,对宽带多相数据而言,乘加器使用数量较大,工程化优势不明显。微波光子技术[8]通过光延迟实现真延时功能,延迟精度受环境因素影响较大,目前技术成熟度暂不满足工程化要求。

宽带时域波束合成最常见做法是通过FIR滤波器组实现的,利用FIR滤波器实现各阵元不同延时后的加权。其设计思路是:若需在期望方向形成指向波束,选择带宽内一定数量频点来进行波束设计,得出在这些特定频点上的加权值,也就是得到每个阵元的幅度权与相位权。设计一组滤波器,使每个滤波器的幅相响应分别在这些频点上,与各阵元的幅度加权和相位加权近似相同。换言之,就是设计一组FIR滤波器,用其幅频响应和相频响应分别拟合各阵元的幅度权与相位权。时域合成框图如图3所示。

图3 时域合成框图Fig.3 Block diagram of time domain DBF

模拟信号数字化后,通过FIR滤波器加权后相加,形成波束输出。在不考虑通道一致的情况下,为降低FIR滤波器阶数,只需要滤波器实现分数点延迟,整数点延迟由FPGA内部缓存或移位寄存器完成。

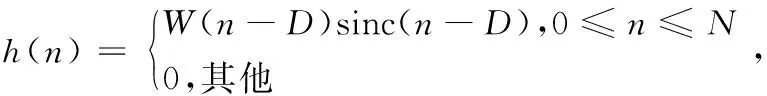

理想的分数时延滤波器的冲激响应可表示为:

hid(n)=sinc(n-D)。

(5)

当延迟不是正整数时,式(5)表示的滤波器是非因果的,若直接使用截断后的sinc函数来设计分数时延滤波器,其性能往往是不可接受的。为降低吉布斯效应的影响,时域加窗是常用的方法。

加窗后的冲激响应如式(6)所示:

(6)

其中,理想冲激响应hid(n)被窗函数截断,窗长L=N+1。窗函数可选择海明窗、汉宁窗以及切比雪夫窗等。窗函数法计算量小、实时性高,但硬件资源受限导致滤波器长度较短时,该方法难以控制幅度响应误差。若波束指向变化时,需不断加载更新滤波器系数,造成波束数据间断,影响对目标信号接收效果。

设计举例:24阵元线阵,阵元间距0.1 m,采样率1 600 Msample/s,瞬时覆盖500 MHz带宽,要求形成3个波束,波束覆盖范围±30°。

校准滤波器系数64阶,时延滤波器系数32阶,满足设计要求。单片FPGA接收2路采样数据,8相200 Msample/s结构,若采用实信号校准合成方法,校准滤波消耗乘法器为64×8×2=1 024,合成滤波消耗乘法器为32×8×2×3=1 536,合计2 560个乘法器,采用XC7VX690T可实现预期功能,但只能形成1个波束。由此可见,宽带时域处理方法资源消耗多,尤其是数据为多相结构时,资源按相数线性增长。

2.2 频域合成法

时域合成处理占用FPGA内部资源较多,因此必须转换思路,选择一种处理实时资源消耗少的校准合成方法支撑宽带阵列处理数字多波束应用需求。

对此,采访中,多地纪检干部也向本刊记者表示,对于群众身边的形式主义、官僚主义等直观的或“变种”的“四风”问题,纪委监委会严查不松劲。“对顶风违纪问题加大监督检查力度,严查快办,并实行责任倒查,严肃追究党组织主体责任和纪检组织的监督责任,同时对典型问题通报曝光,形成有力震慑。”近来,各地通过不断丰富监督检查手段,通过常规检查、大数据筛查、群众监督等方式,密切关注“四风”隐形变异、改头换面等新动向,其目的都是很明确的,那就是严防“四风”反弹回潮。

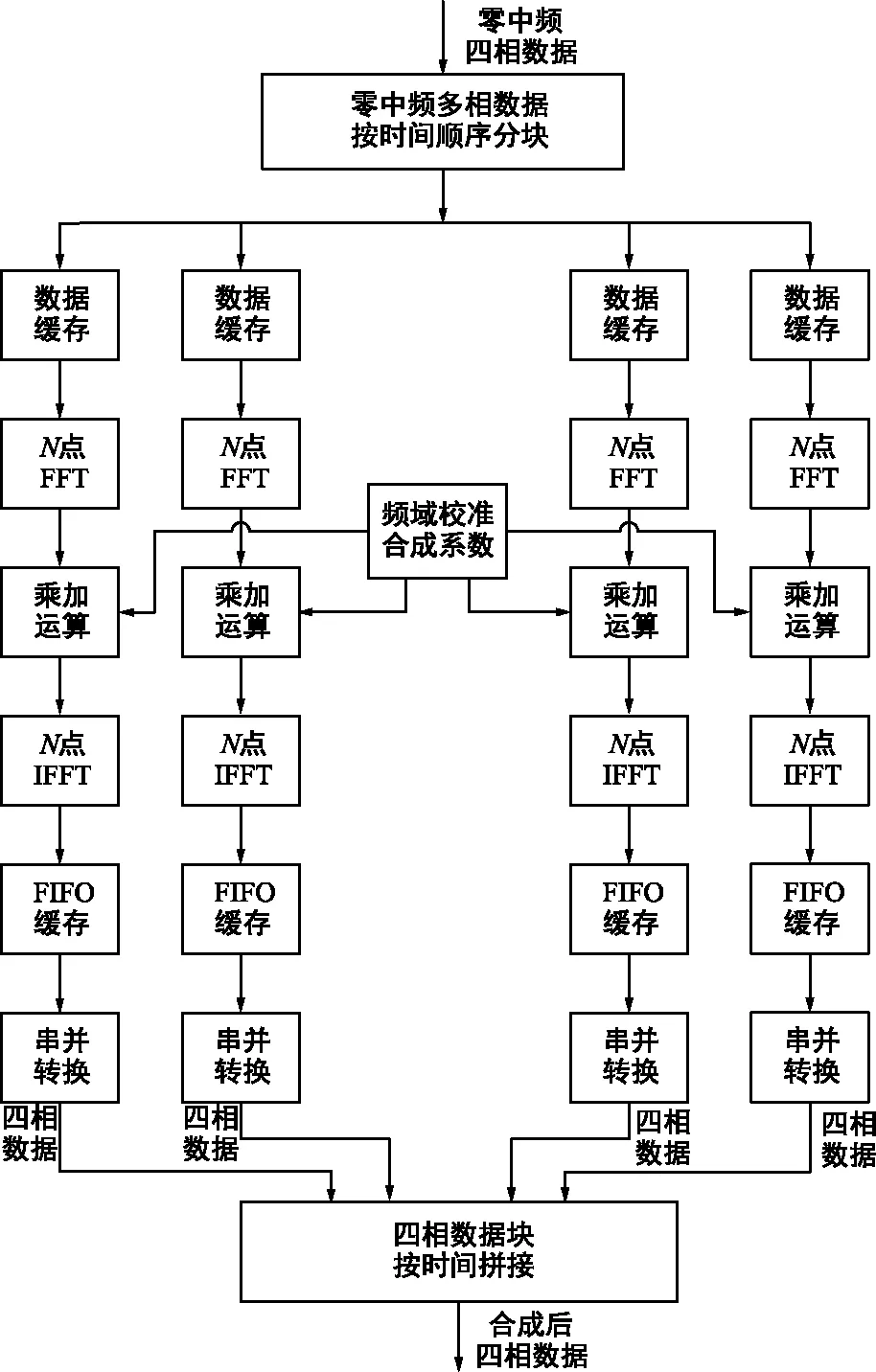

时域校准合成实质为数据流与时域系数卷积运算,需通过并行乘加实现。若将运算变换至频域处理,校准合成系数先进行卷积运算,补零后通过FFT运算变换至频域,频域系数与频域数据串行相乘,各路相加后再IFFT变换至时域,形成DBF数据流。FFT和IFFT消耗乘法器和存储资源较少,乘法器的使用数量较时域大为减少。频域合成FPGA实现如图4所示。

图4 频域合成FPGA实现框图Fig.4 FPGA implementation of frequency domain DBF

图4中,通过JESD204B总线接收的采样数据经过多相滤波形成四相零中频数据流,对多相数据流按N点等间隔进行划分,数据块顺序与FPGA中4路处理资源对应,经过数据缓存并串转换后进行FFT运算,并与DSP下发的频域系数相乘后与其他数据通道的对应支路求和,IFFT变换至时域,串并转换后,按照时间对应关系重新排列数据,形成连续的波束合成时域数据流。

3 FPGA实现验证

在超宽带波束合成FPGA实现过程中,遇到了多个技术实现问题。例如频率分辨率与自校源步进不匹配,FPGA处理时钟高造成时序收敛困难,数据传输量过大导致形成波束数量减少,频域合成后的时域数据断数,校准合成一体设计降低资源量,提升波束扫描连续性等FPGA实现问题。

3.1 采样率变换提升处理与传输

在工程应用中,校准时理想状态是让校准频点精确落在整数谱线上。自校源产生的频率步进最小为500 kHz,若按采样率进行计算,采样率800 Msample/s,FFT点数256,此时频率步进为3.125 MHz,不能与自校源进行适配。

在XC7VX690T中,当FPGA资源占用较多时,时钟速率运行至200 MHz会造成时序收敛的困难。

采样率为800 Msample/s,一个波束的数据量为25.6 Gbit/s,再加之64/66 bit编码效率以及95%的传输效率,数据量为27.79 Gbit/s,需通过一组4XAurora总线才能将一个波束传出,造成FPGA高速串行接口使用过多,减少了波束数据的传输,从而限制了波束形成数量。

为了解决以上三点问题,设计了基于多相结构的采样率变换模块,采样率由800 Msample/s变换至640 Msample/s,校准的频率步进由3.125 MHz变为640/256=2.5 MHz,适配了自校源频率步进特性。

通过采样率变换后,FPGA内部逻辑处理时钟为640/4=160 MHz,有效降低了FPGA电路时序收敛的难度,降低了FPGA技术开发难度。

3.2 IFFT变换后波束数据不连续

在频域处理时,通过仿真发现IFFT后的波束数据存在不连续现象,即当进行IFFT变换时,存在瞬态信息丢失问题。因此频域处理必须消除两次IFFT交界处相位不连续对合成造成的影响[9]。

结合FPGA实现特点,采用1/2交叠运算的办法对相邻两次IFFT后时域数据交叠处进行去重处理。以单音信号为输入,通过仿真对比,频域FFT处理不作1/2交叠与作1/2交叠,输出时域数据的对比。光滑曲线是经过1/2交叠后的曲线,三角符号曲线代表未经过1/2交叠的曲线,如图5所示。

图5 FFT计算1/2交叠对比图Fig.5 1/2 overlap comparison chart of FFT calculation

由图5不难看出,未经过1/2交叠处理的数据波形存在明显数据点周期性跳变现象,跳变周期与FFT点数一致。与不交叠处理相比,交叠处理会使FPGA波束形成模块的资源消耗翻倍,但与时域校准合成相比,频域处理资源消耗小,仍具明显优势。

3.3 频域校准合成一体设计

传统的宽带时域数字波束形成多采用多相分解滤波器的结构,对通道校准滤波器和时延滤波器独立设计,通过滤波器级联的方式硬件实现,导致乘加滤波资源消耗过大,宽带波束形成个数较少,工程化使用受限。

如果将时域信号变换至频域处理,可在DSP处理器中,对校准系数与合成系数首先进行时域卷积运算,达到校准系数与合成系数一体设计的效果,再转化成频域系数进行乘加运算后转换为时域数据,通过这样的转化运算能有效降低FPGA内乘法器资源消耗,提升波束形成个数,工程化优势明显。

3.4 提升波束扫描连续性

传统的数字波束合成采用延时滤波器实现,在FPGA中通过对FIR滤波器在线配置实现。当波束指向发生变化时,需要实时对时延滤波器系数进行加载更新和复位,在更新系数时,输出的DBF存在时间上间断现象,影响对目标信号侦察控守。

频域处理时,合成系数是按块运算的,只要提前将指向系数写入FPGA缓存内,在FPGA的时序控制下,将系数写入波束合成模块,在不复位电路的情况下,对波束指向进行“捷变”,切换速率为FPGA内部一个时钟周期。

3.5 频率指向一致性验证

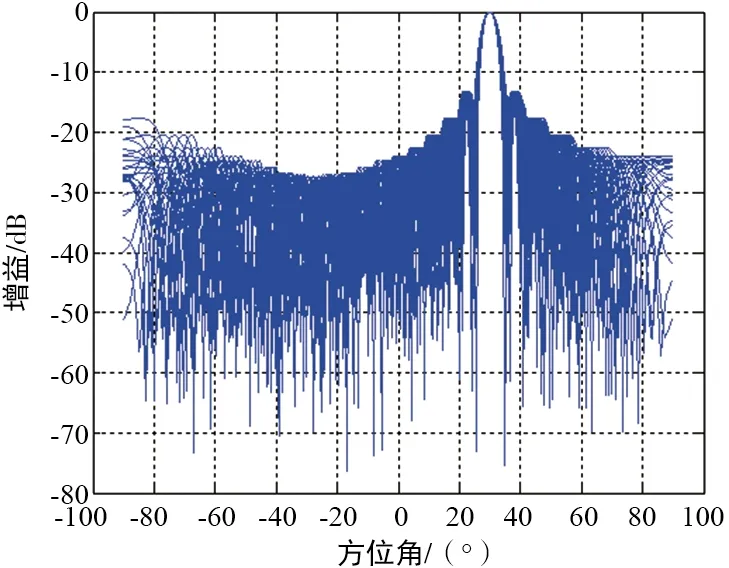

为了验证瞬时带宽内DBF后各频率指向一致性, 500 MHz内产生26个等间隔20 MHz的单音信号进行仿真,在30°指向时,得到各频率的波束图。

由图6可以看出,所有频率分量的单音信号都指向了30°,没有其他方向的波束峰值出现,从而验证了宽带下各频率指向一致性。

图6 多音信号波束指向仿真Fig.6 Beam pointing simulation of multitone signal

3.6 合成增益验证

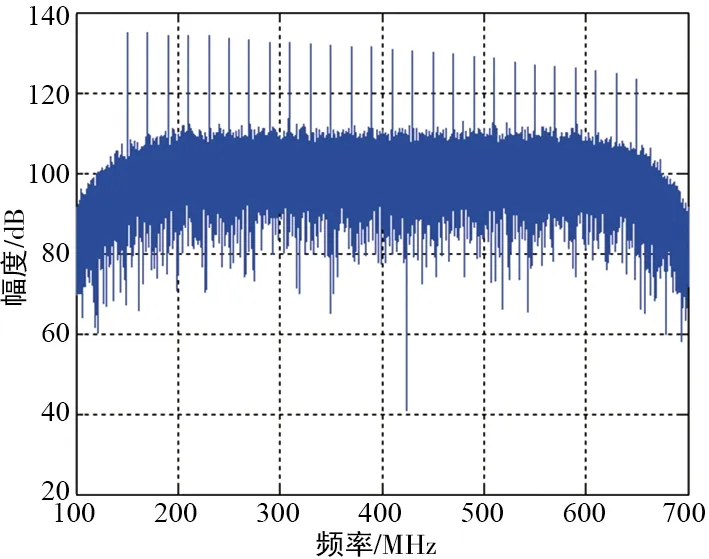

为了验证波束合成效果,采用专用信号发生器输出多个单音信号,通过功分配器输出至波束合成接收机各中频输入。通过FPGA校准合成处理,将单路采样数据与频域合成后数据存储后导入至Matlab中计算幅度谱,覆盖频率范围从150~650 MHz,分别如图7与图8所示。

图7 宽带波束合成前频谱Fig.7 Spectrum analysis before wideband DBF

图8 宽带波束合成后频谱Fig.8 Spectrum analysis after wideband DBF

由图7与图8不难看出,经过宽带数字波束形成处理后,信号幅度不变,但宽带内噪底显著降低,信噪比得到明显提升。通过数据统计,合成增益约13 dB,与理论值13.8 dB接近,从而验证了该处理方法的可行性与有效性,为数字化宽带阵列校准合成处理的工程实现进行了技术储备。

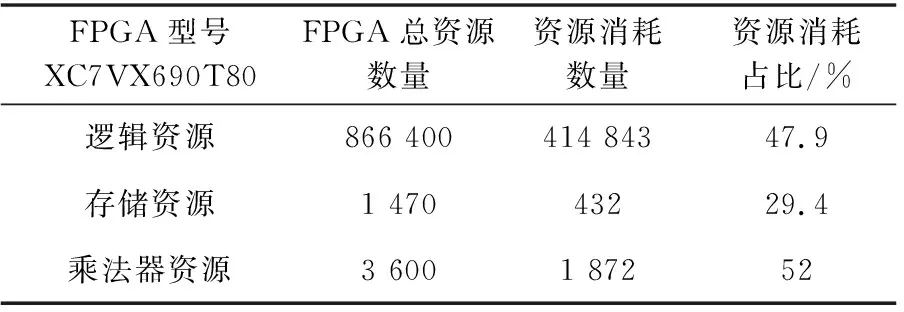

3.7 FPGA处理资源统计

在Vivado17.4环境下,对XC7VX690T芯片综合布线后资源使用情况进行了统计,单片FPGA实现两通道1 600 Msample/s实采样数据接收,形成3个独立500 MHz宽带波束输出,资源占用如表1所示。

表1 FPGA中资源消耗

FPGA中主要资源有3种:逻辑资源、存储资源和乘法器资源。由表1可知,3个宽带500 MHz的波束形成功能在FPGA中片内资源消耗占比分别为47.9%、29.4%和52%。FPGA程序运行在160 MHz处理时钟下,波束合成功能运行稳定可靠。

4 结束语

本文介绍了数字波束形成原理与超宽带数字波束形成技术的实现过程,重点描述了采用频域合成技术实现超宽带多通道校准与波束形成的处理过程,并结合FPGA特性进行了硬件实现,验证了频域合成技术对超宽带数字波束形成的有效性。

当前对相控阵系统探测距离要求的提升,促使相控阵天线阵面尺寸日益增大,阵元数量也对应增长,越发凸显功耗与成本给阵列技术工程化造成的瓶颈。随着半导体工艺的飞速发展,采用SIP微封装,低功耗集成化ASIC芯片设计的数字T/R组件[10]技术受到阵列信号处理领域广泛重视,其中资源消耗较大,功能可固化的处理模块采用ASIC流片,以达到低功耗与低成本预期。FPGA设计作为ASIC流片设计前期的原型验证手段,起到了缩短芯片设计周期以及优化芯片实现结构的作用,是专用集成芯片开发过程中不可或缺的技术验证环节。