基于玻璃钝化结构的梁式引线肖特基T 型对管芯片的研制

汤寅,熊威,王霄,杨勇

(南京电子器件研究所,江苏 南京 210016)

肖特基势垒二极管与PN 结二极管相比,起始电压低、贮存电荷效应小、开关速度快[1-2],所以能在很高的频率下工作,在通信、微波测量和微波仪器中得到广泛使用。梁式引线结构由于摒弃了管壳封装,直接用电镀金梁代替常规器件的引线,用它直接连接到微带电路上,引线电感小的同时消除了管壳电容,极大提高了器件的频率性能[3-6]。

N 型Si 基梁式引线低势垒肖特基二极管T 型串联对管芯片结合了肖特基二极管和梁式引线结构的特点,并将2 只芯片集成在一起,可以有效提升芯片的一致性,使整流检波电路的对称性更好,电路稳定性和可靠性得到有效提高。该种形式器件应用领域非常广泛,可用于平衡式混频器和宽带检波器等微波电路,在倍压整流检波电路、自动增益控制(AGC)、微波信号源的自动电平控制(ALC)环路和接收机中的常用调幅解调等方面也有重要应用。早期国内外有少量关于硅梁式引线集成器件的报道[7-8],但采用的是类似聚酰亚胺支撑的技术途径,由于可靠性差等原因导致其不具备工程应用价值。而基于玻璃钝化结构的梁式引线集成器件虽然机械强度高、可靠性优异,但工艺实现难度较大,且对集成管芯的参数性能一致性要求极高,多年来国内外在这方面的研究报道鲜见。

本文设计了一种易于实现的基于玻璃钝化结构的梁式引线集成器件工艺途径,主要通过玻璃槽成型及钝化技术结合低势垒蒸发工艺实现了器件制备。研制的芯片正向压降VF≤350 mV,结电容Cjo≤0.1 pF,击穿电压VBR≥4 V,动态电阻RD≤20 Ω,电压灵敏度Sv≥17 mV/μW,对管芯片的关键电参数偏差小于5%。基于该技术途径可进一步拓展为对管(反向并联)、四管堆(含环形、交叉环形、共面环形、桥型、共面桥型)等结构形式,非常适用于微波混合集成电路,可有效促进整个电路组件的小型化发展。

1 结构设计

本文设计的梁式引线T 型串联对管芯片结构如图1 所示。器件由两个对称的肖特基单结组成,以确保电参数的一致性。硅岛周围采用“V” 字型玻璃钝化支撑保护,以提升器件机械强度和可靠性水平。金-半接触周围采用低压化学气相沉积(LPCVD) 生长的SiO2钝化,以降低器件漏电流水平。势垒孔选用优化后的势垒金属以降低势垒高度,进而获得优良的正向导通电压。电极互连以及引出端金梁均采用电镀实现,具备高的附着力和优良的键合特性。

图1 梁式引线T 型串联对管芯片的结构示意图Fig.1 Schematic diagram of T-type beam lead Schottky diode series pairs

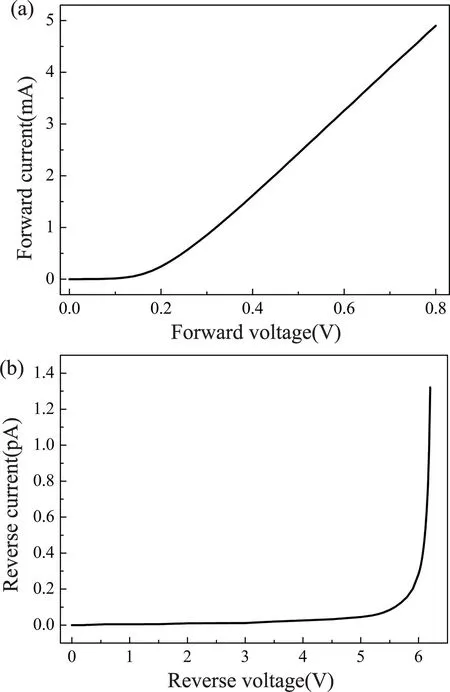

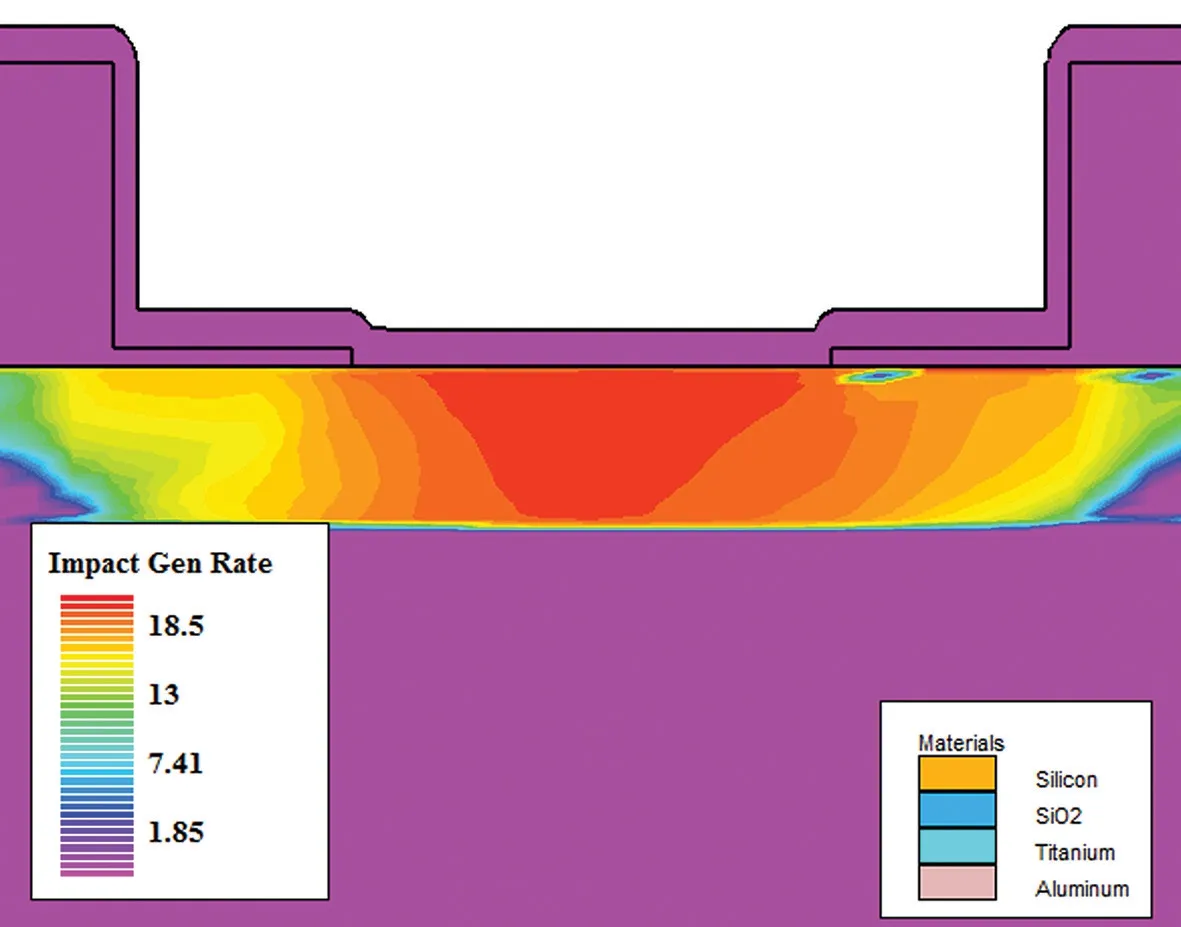

肖特基单结芯片的I-V特性和电场分布仿真结果分别如图2 和图3 所示。设计的单结芯片的正向电压低于350 mV,反向击穿电压高于5 V,且呈现体内击穿。

图2 肖特基单结芯片的I-V 特性。(a)正向I-V 曲线;(b)反向I-V 曲线Fig.2 The I-V characteristic of single Schottky diode.(a) Forward I-V curve;(b) Reverse I-V curve

图3 肖特基单结芯片的电场分布Fig.3 The electric field distribution of single Schottky diode

2 工艺制备

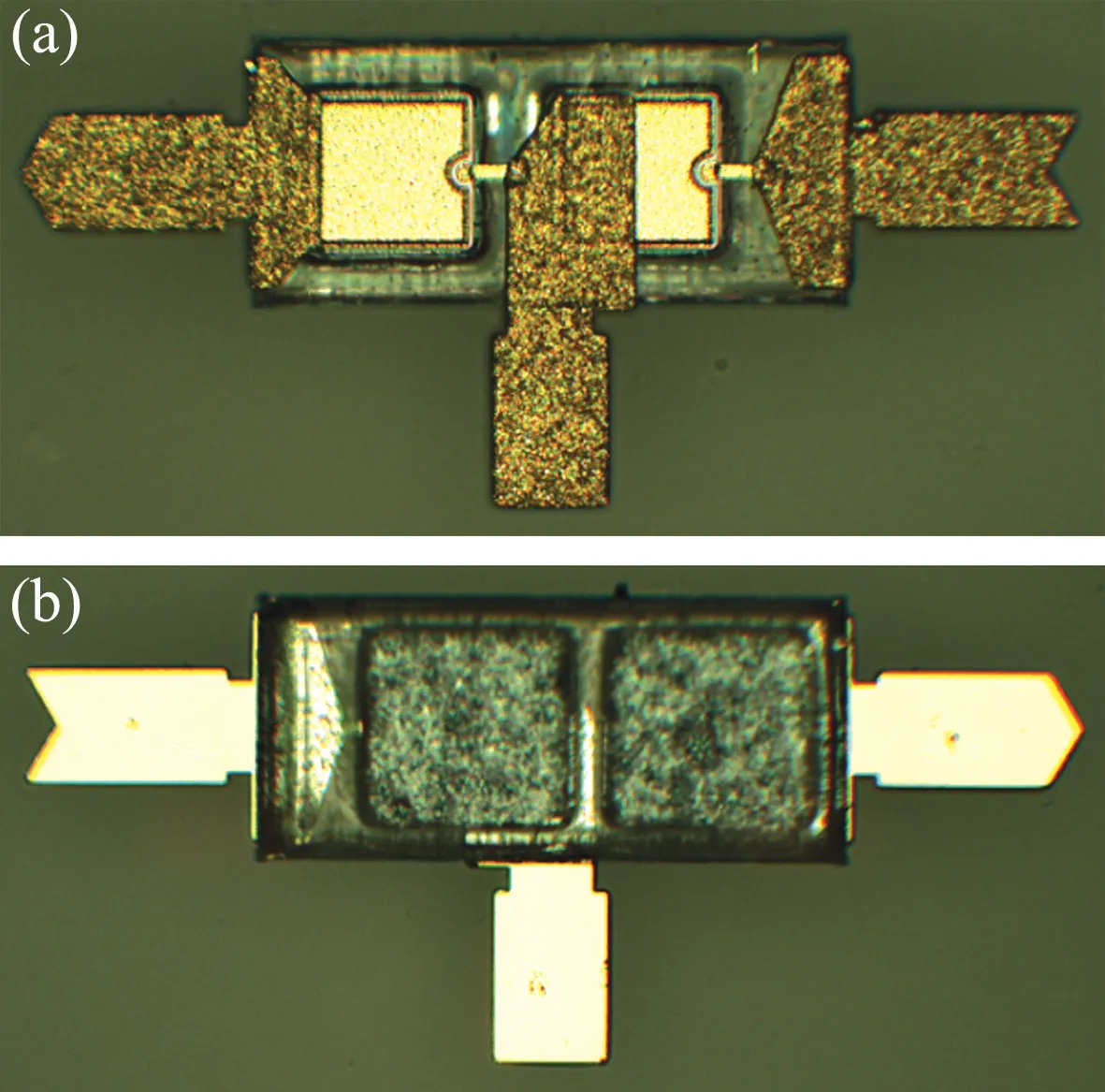

本文制备的对管芯片实物外观如图4 所示。器件采用的是n 型外延硅片,由于本器件为低势垒肖特基二极管对,对于外延材料要求较高,要求外延厚度极薄的同时过渡区极短。在工艺方面的难度主要集中于玻璃槽成型、玻璃钝化填充以及低势垒蒸发工艺。

图4 梁式引线T 型串联对管芯片外观图。(a)正面;(b)背面Fig.4 Figuration of T-type beam lead Schottky diode series pairs.(a) Front side;(b) Back side

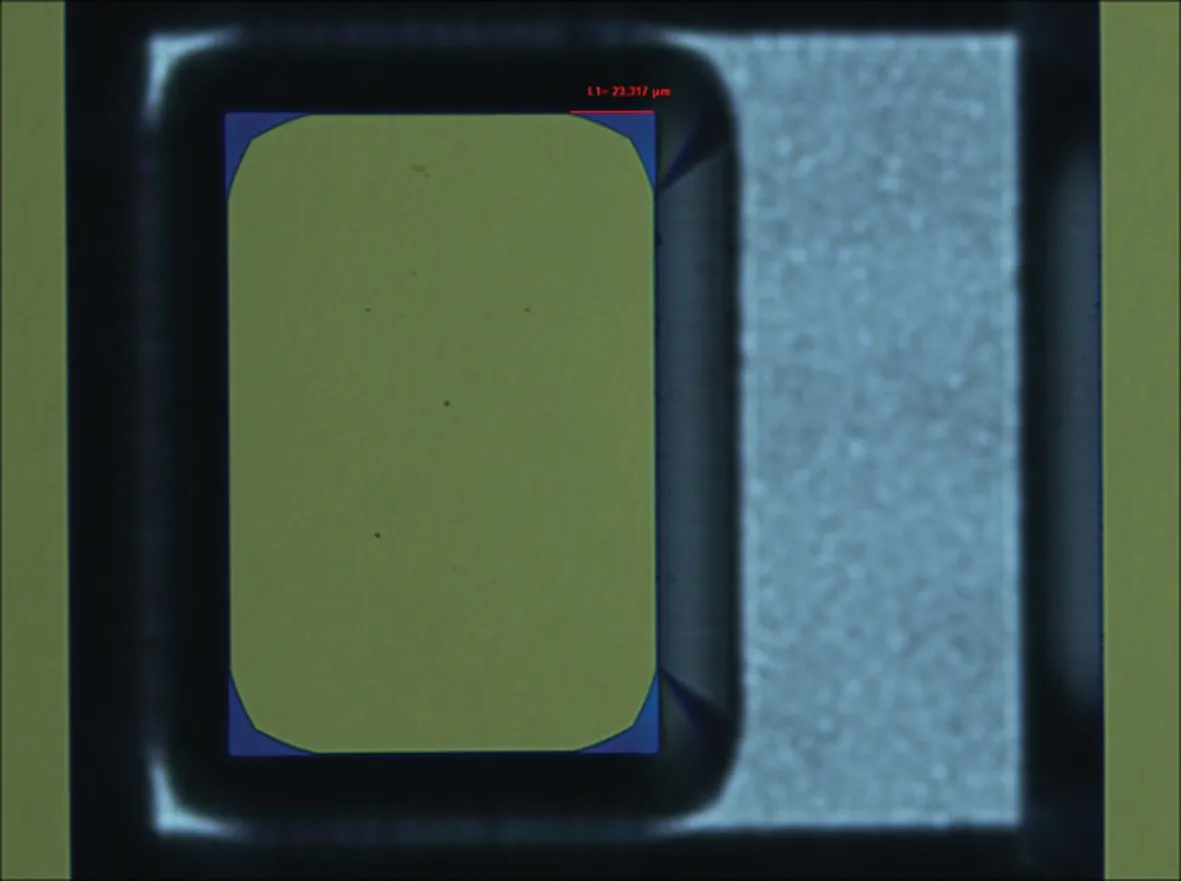

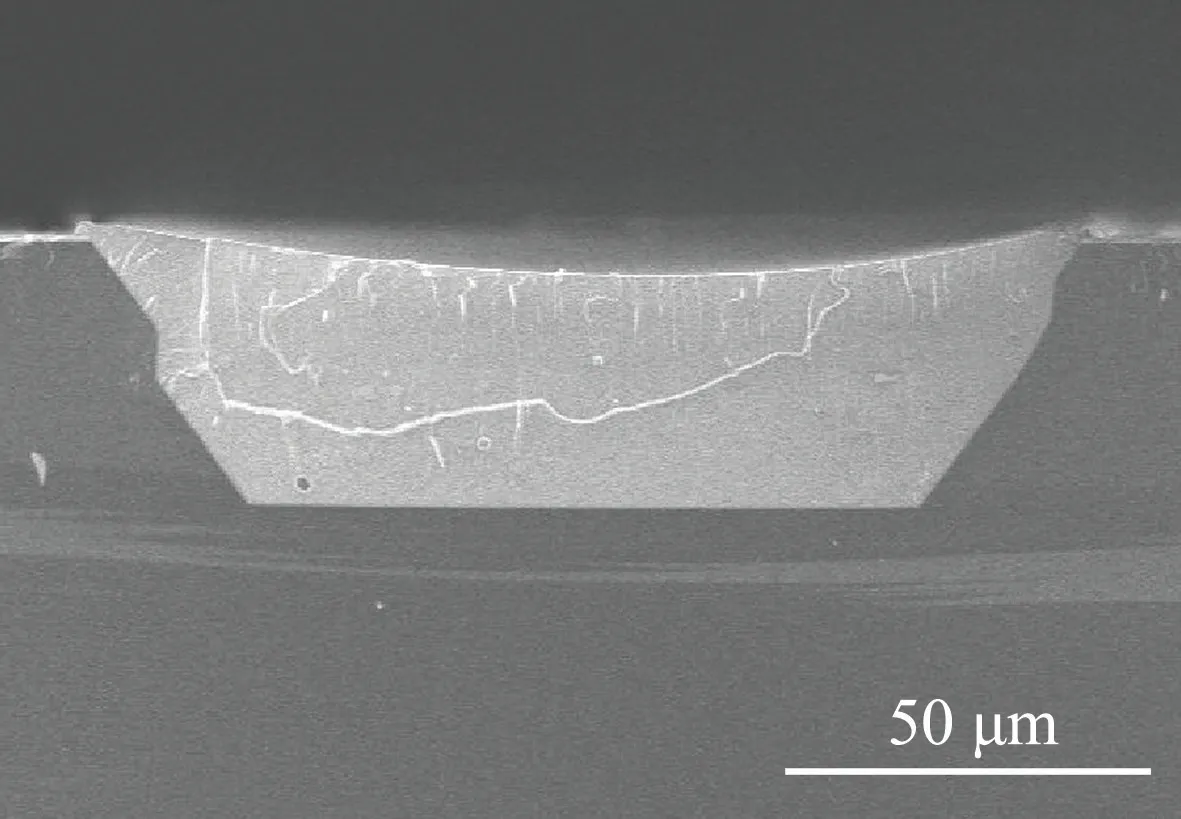

玻璃槽成型工艺是实现高可靠性梁式引线结构的关键技术之一。基于玻璃钝化的梁式引线结构芯片,需在势垒结构四周刻蚀出“V” 型玻璃槽结构,用以填充玻璃,使之与硅片保持平坦,以利于制作势垒和欧姆接触的引出端。TMAH 湿法腐蚀工艺是实现“V”型玻璃槽结构的适宜途径,具备良好形貌的同时可以使硅片的工艺损伤降到最低,且能保障良好的工艺一致性。但在试验中发现,假如“V” 型玻璃槽全部采用湿法腐蚀工艺腐蚀至30 μm 以上深度,方形硅岛的四角将会出现不同程度的钻蚀,导致直角变圆滑(如图5 所示),从而影响后续工艺的进行。针对该问题,试验采用了梯度式腐蚀法,即ICP 干法刻蚀+TMAH湿法腐蚀相结合的方法,可以较好地解决直角钻蚀的问题。图6 展示了采用梯度式腐蚀法后的器件形貌,其中图6(a)为光学显微镜俯视图,可见直角钻蚀得到了明显改善;图6(b)为SEM 侧视图,显示了良好“V” 型玻璃槽侧面形貌,槽内侧壁光滑无毛刺。

图5 TMAH 湿法腐蚀后的形貌Fig.5 The morphology after TMAH-wet corrosion

图6 梯度式腐蚀法后的形貌。(a)光学显微镜俯视图;(b)SEM 侧视图Fig.6 The morphology after gradient corrosion.(a) Top view using light microscope;(b) Side view using SEM

另一个工艺难点在于玻璃钝化,工艺上需选择热膨胀系数小的钝化玻璃粉材料,以实现与硅的最佳应力匹配效果,提高器件支撑强度的同时降低翘曲变形。玻璃涂覆方面选择了刮涂法,具有易操作、可重复、污染少、利用率高等优点。玻璃浆进行烘干后体积收缩明显,易造成台面边缘缺乏覆盖从而导致漏电流增大,因此需要适当提高玻璃浆中玻璃粉的占比,但占比太高又易造成玻璃钝化均匀性差、厚薄不一。在兼顾覆盖和均匀性两方面的前提下,通过大量试验摸索得出了玻璃粉与溶剂最佳质量配比为8 ∶2,可保证玻璃钝化膜的覆盖效果。优化后的玻璃钝化形貌如图7所示,可见V 形玻璃槽能够得到完全、严密的覆盖填充。

图7 V 形槽玻璃钝化后的形貌Fig.7 The morphology of V-groove after glass passivation

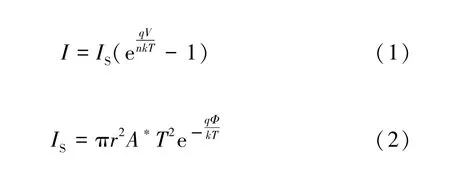

肖特基二极管是目前使用最多的非线性器件[9-10],有别于欧姆接触[11]器件,它的金属电极系统与半导体在二者的界面上接触形成了肖特基接触或整流接触[12]。其中,肖特基接触势垒的设计尤为重要,是器件电参数实现的关键技术之一。随肖特基势垒高度的降低,其不均匀性将增大[13],对于肖特基对管而言研制难度更高。肖特基势垒二极管的伏安特性为:

式中:IS为饱和电流;q为电子电荷;n为理想因子;k为玻耳兹曼常数;T为热力学温度;r为势垒结半径;A*为理查逊常数;Φ为金属-半导体接触的势垒高度。

势垒高度Φ的精准设计是实现低势垒性能的关键。势垒金属的选择对器件性能的优劣有重要的影响,表1列出了几种常见金属与n-Si 接触的势垒高度,此外,势垒金属的选择还需要结合稳定性以及黏附性能等综合考虑。从耐烧毁特性的角度来看,应尽量选择那些与硅共熔温度高、热导率高、比热与比重之积大(即热扩散率小)且与SiO2黏附性能好的金属;从势垒高度来看,许多金属都可以与n-Si 形成中低势垒;从与硅共熔温度要高来看,Mo、Ta、Ti 较为合适;而从与SiO2黏附性能来看,Al、Cr、Ti 具有良好附着力。综合比较,选择Ti 作为低势垒金属是较佳选择。

表1 常见金属与n-Si 接触的势垒高度Tab.1 The barrier height of common metal in contact with silicon

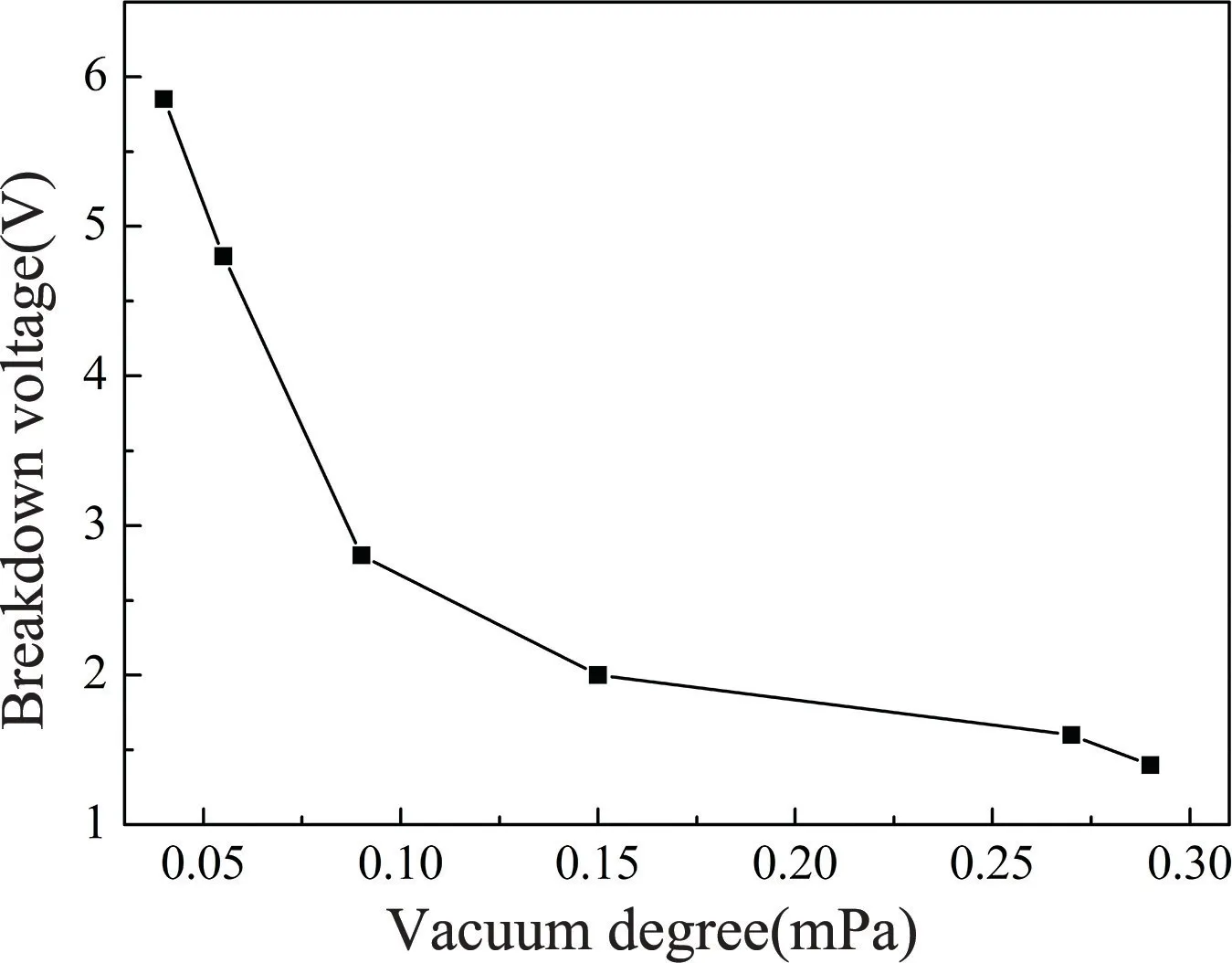

除势垒金属的设计外,随后的蒸发工艺同样至关重要,直接影响器件的电参数性能。当选择钛(Ti)作为低势垒金属时,试验中发现蒸发腔室的真空度对器件电参数特别是击穿电压有明显影响,如图8 所示。经研究发现由于Ti 金属极活泼、易氧化,如果蒸发腔室的真空度较低,残余空气中的活性分子(如氧分子)与金属原子将形成化合物,影响肖特基器件的势垒高度;蒸发金属粒子的直线运动也会受到残余气体分子的碰撞而形成雾状微粒,难以制备均匀平整的势垒金属薄膜,导致器件电参数一致性的下降。经试验发现,真空度越高(≤0.07 mPa),蒸发金属粒子的平均自由程越大,越容易获得高质量的势垒金属薄膜。

图8 真空度对击穿电压的影响Fig.8 The influence of vacuum degree on breakdown voltage

3 结果与分析

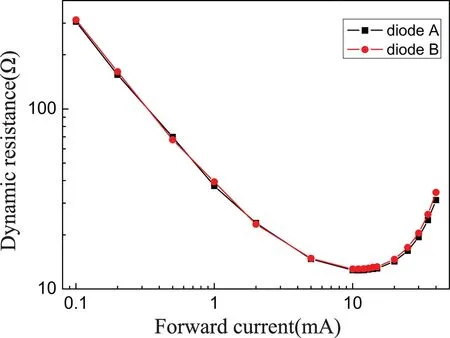

在室温下对研制器件两路芯片进行正向I-V测试,测试结果如图9 所示。两路芯片在正向电流1 mA 时的正向电压分别为312 mV 和313 mV,呈现低势垒特性,且芯片对称性极佳,偏差仅为0.3%。图10 为测得的对管芯片动态电阻随正向电流的变化曲线,动态电阻随正向电流增大而降低,在10 mA 附近达到最低点后逐渐增大,呈现U 型变化趋势,这是由于肖特基器件在大信号输入下电流特性趋近饱和的缘故。当正向电流为5 mA 时,动态电阻分别为14.6 Ω 和14.7 Ω,偏差为0.7%。

图9 梁式引线T 型串联对管芯片的正向I-V 曲线Fig.9 The forward I-V curves of T-type beam lead Schottky diode series pairs

图10 动态电阻随正向电流的变化曲线Fig.10 The dynamic resistance curves with forward current

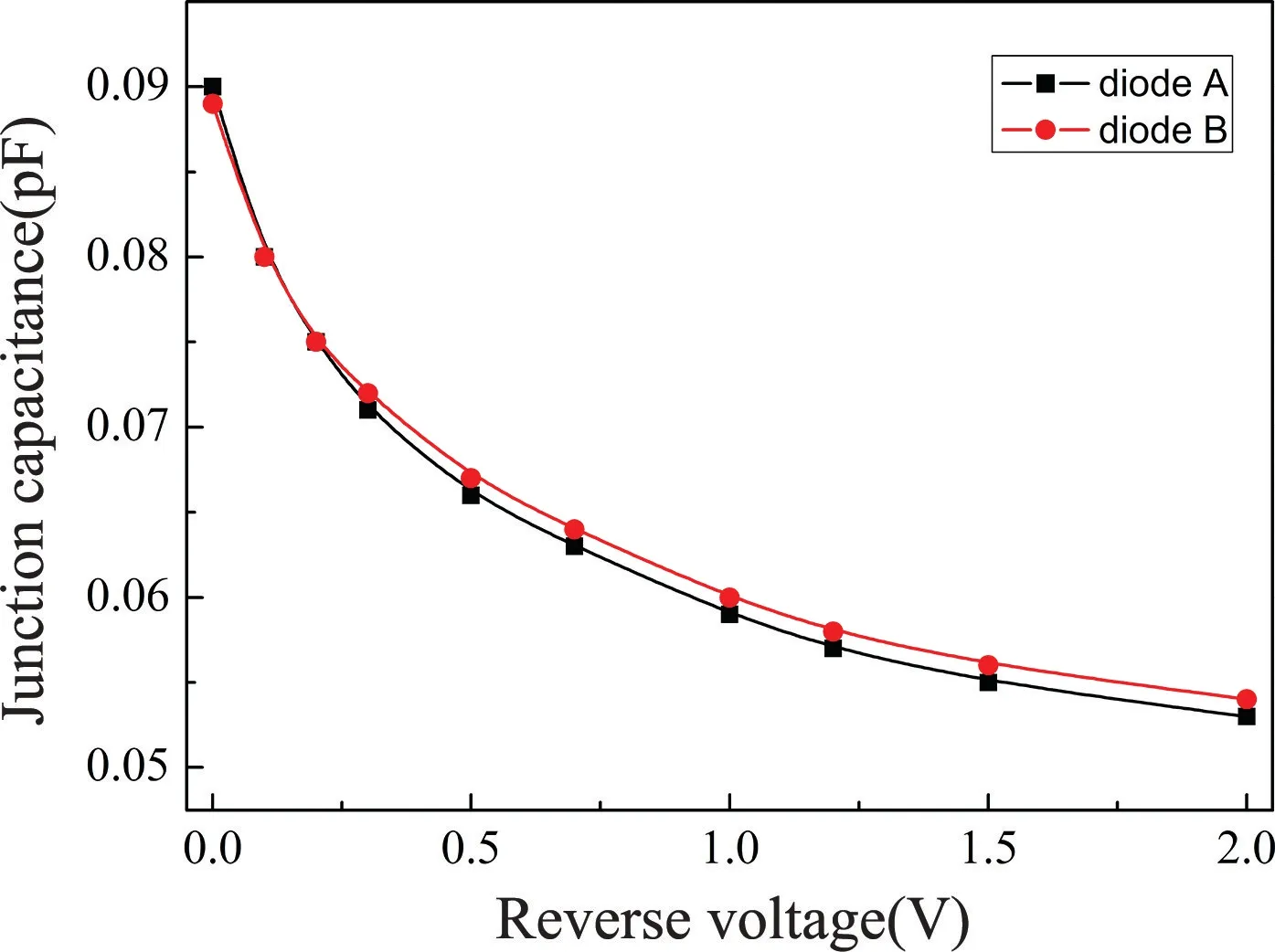

梁式引线T 型串联对管芯片的工作频率与电容值密切相关。图11 显示了测得的对管芯片C-V曲线,零偏置下其结电容仅为0.09 pF 和0.089 pF,偏差为1.1%。

图11 梁式引线T 型串联对管芯片的C-V 曲线Fig.11 The C-V curves of T-type beam lead Schottky diode series pairs

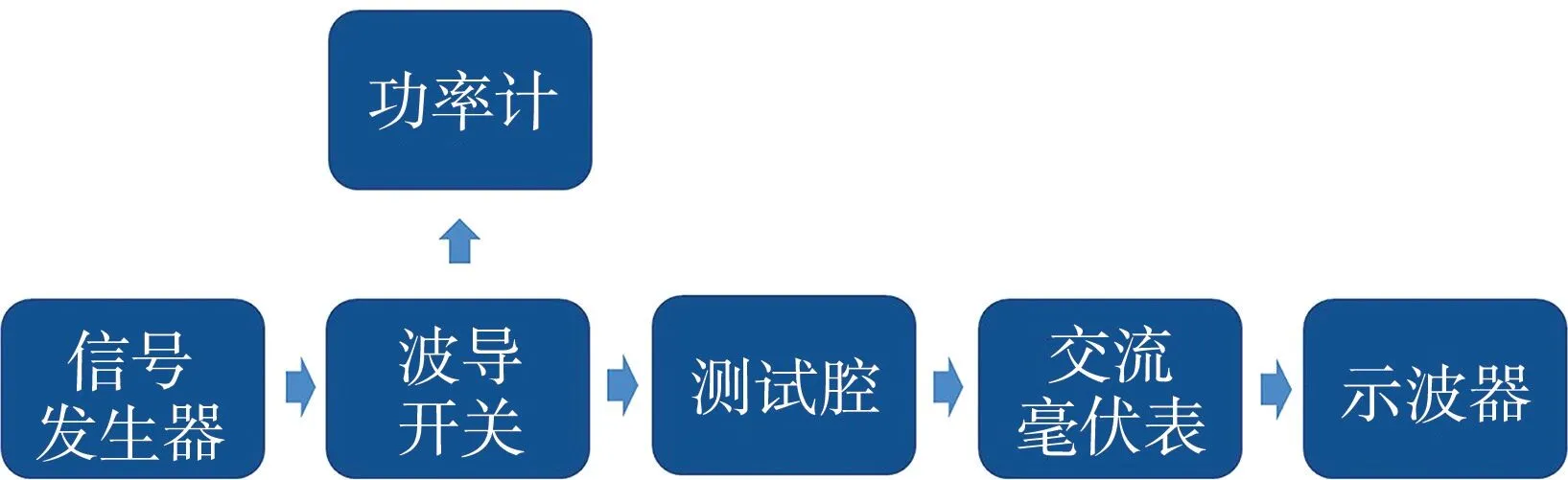

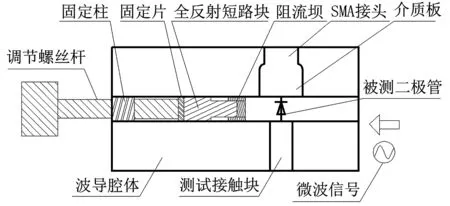

检波电路是梁式引线T 型串联对管芯片的重要用途[14-15],电压灵敏度SV是其电路核心应用指标。设计的适用于10 GHz 下测试系统方框图如图12 所示。10 GHz 下检波二极管的微波性能测试通常需放置在波导系统中进行,需研制一款可调谐的波导测试腔体,腔体的设计主要涉及波导尺寸的选择、截止波长的范围、主模波的选取、功率输入接口和微带线同轴转换输出等方面,最终设计的波导测试腔体的结构示意图如图13 所示。

图12 电压灵敏度测试系统方框图Fig.12 The block diagram of voltage sensitivity test system

图13 微带型检波二极管测试腔体结构示意图Fig.13 The schematic diagram of microstrip detector diode test cavity

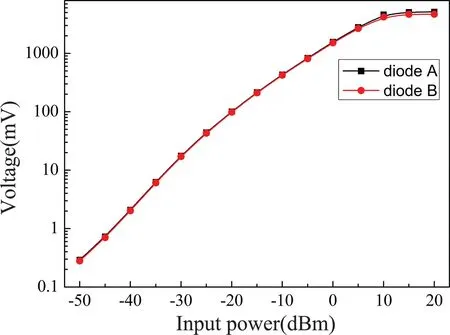

图14 显示了在10 GHz 时测得的对管芯片输出电压与输入功率的关系曲线,对管芯片在-50~10 dBm区间内呈现良好的线性输出关系,在10 dBm 以上区间呈饱和现象。对管芯片在输入功率1 μW 时,输出电压分别为17.5 mV 和17.2 mV,仍体现了较好的对称性。

图14 输出电压与输入功率的关系曲线Fig.14 The relationship between the output voltage and the input power

与美国HP 公司的HSCH-5531 性能对比结果如表2 所示。主要电参数均达到进口器件同一水平。

表2 研制器件与HSCH-5531 的性能对比Tab.2 Comparison between the developed device and HSCH-5531 in performance

4 结论

本文通过玻璃槽成型与钝化技术结合低势垒蒸发工艺实现了Si 基梁式引线低势垒肖特基二极管T 型串联对管芯片的研制。研制的芯片正向压降VF≤350 mV,结电容Cjo≤0.1 pF,击穿电压VBR≥4 V,动态电阻RD≤20 Ω,电压灵敏度Sv≥17 mV/μW。得益于梯度式TMAH 湿法腐蚀及低势垒蒸发工艺,集成管芯的参数一致性极佳(偏差小于5%),可进一步拓展应用于其他集成管堆结构,有利于促进检波混频电路的小型化发展。